IEC PAS 62326-20:2011

(Main)Printed boards - Part 20: Electronic circuit board for high-brightness LEDs

Printed boards - Part 20: Electronic circuit board for high-brightness LEDs

IEC/PAS 62326-20:2011(E) specifies the properties of the electronic circuit board for high-brightness LEDs (hereafter described as "ECB").

General Information

- Status

- Replaced

- Publication Date

- 25-Jan-2011

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 4 - TC 91/WG 4

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 03-Feb-2016

- Completion Date

- 13-Feb-2026

Relations

- Replaced By

IEC 62326-20:2016 - Printed boards - Part 20: Printed circuit boards for high-brightness LEDs - Effective Date

- 05-Sep-2023

Get Certified

Connect with accredited certification bodies for this standard

TL 9000 QuEST Forum

Telecommunications quality management system.

ANCE

Mexican certification and testing association.

Intertek Slovenia

Intertek testing, inspection, and certification services in Slovenia.

Sponsored listings

Frequently Asked Questions

IEC PAS 62326-20:2011 is a technical specification published by the International Electrotechnical Commission (IEC). Its full title is "Printed boards - Part 20: Electronic circuit board for high-brightness LEDs". This standard covers: IEC/PAS 62326-20:2011(E) specifies the properties of the electronic circuit board for high-brightness LEDs (hereafter described as "ECB").

IEC/PAS 62326-20:2011(E) specifies the properties of the electronic circuit board for high-brightness LEDs (hereafter described as "ECB").

IEC PAS 62326-20:2011 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards; 33.160.30 - Audio systems. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC PAS 62326-20:2011 has the following relationships with other standards: It is inter standard links to IEC 62326-20:2016. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC PAS 62326-20:2011 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC/PAS 62326-20 ®

Edition 1.0 2011-01

PUBLICLY AVAILABLE

SPECIFICATION

PRE-STANDARD

colour

inside

Printed boards –

Part 20: Electronic circuit board for high-brightness LEDs

IEC/PAS 62326-20:2011(E)

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC/PAS 62326-20 ®

Edition 1.0 2011-01

PUBLICLY AVAILABLE

SPECIFICATION

PRE-STANDARD

colour

inside

Printed boards –

Part 20: Electronic circuit board for high-brightness LEDs

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

PRICE CODE

X

ICS 31.180 ISBN 978-2-88912-345-2

– 2 – PAS 62326-20 IEC:2011(E)

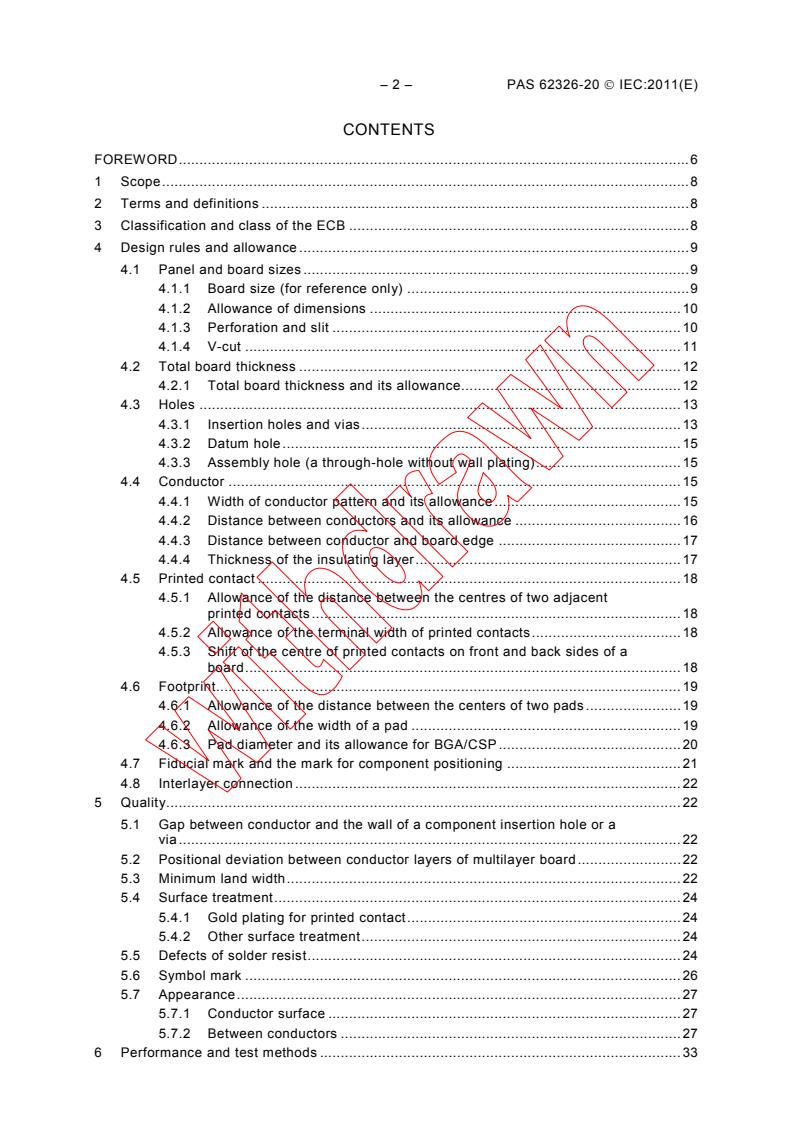

CONTENTS

FOREWORD . 6

1 Scope . 8

2 Terms and definitions . 8

3 Classification and class of the ECB . 8

4 Design rules and allowance . 9

4.1 Panel and board sizes . 9

4.1.1 Board size (for reference only) . 9

4.1.2 Allowance of dimensions . 10

4.1.3 Perforation and slit . 10

4.1.4 V-cut . 11

4.2 Total board thickness . 12

4.2.1 Total board thickness and its allowance . 12

4.3 Holes . 13

4.3.1 Insertion holes and vias . 13

4.3.2 Datum hole . 15

4.3.3 Assembly hole (a through-hole without wall plating) . 15

4.4 Conductor . 15

4.4.1 Width of conductor pattern and its allowance . 15

4.4.2 Distance between conductors and its allowance . 16

4.4.3 Distance between conductor and board edge . 17

4.4.4 Thickness of the insulating layer . 17

4.5 Printed contact . 18

4.5.1 Allowance of the distance between the centres of two adjacent

printed contacts . 18

4.5.2 Allowance of the terminal width of printed contacts . 18

4.5.3 Shift of the centre of printed contacts on front and back sides of a

board . 18

4.6 Footprint. 19

4.6.1 Allowance of the distance between the centers of two pads . 19

4.6.2 Allowance of the width of a pad . 19

4.6.3 Pad diameter and its allowance for BGA/CSP . 20

4.7 Fiducial mark and the mark for component positioning . 21

4.8 Interlayer connection . 22

5 Quality . 22

5.1 Gap between conductor and the wall of a component insertion hole or a

via . 22

5.2 Positional deviation between conductor layers of multilayer board . 22

5.3 Minimum land width . 22

5.4 Surface treatment . 24

5.4.1 Gold plating for printed contact . 24

5.4.2 Other surface treatment . 24

5.5 Defects of solder resist . 24

5.6 Symbol mark . 26

5.7 Appearance . 27

5.7.1 Conductor surface . 27

5.7.2 Between conductors . 27

6 Performance and test methods . 33

PAS 62326-20 IEC:2011(E) – 3 –

6.1 Observation of component mounting for and vias . 33

6.1.1 Observation with standard conditions . 33

6.1.2 Observation after thermal shock test . 34

7 Marking, packaging and storage . 47

7.1 Marking on a product . 47

7.2 Marking on the package . 47

7.3 Packaging and storage . 47

7.3.1 Packaging . 47

7.3.2 Storage . 47

8 Normative references . 47

Annex A (informative) Additional information to IEC/PAS 62326-20. 48

Figure 1 – Example of classification and their application by base materials,

electronic circuit boards and final products . 9

Figure 2 – Board arrangement in a panel . 9

Figure 3 – Distances from the datum point to perforation and slit . 10

Figure 4 – Distance from the datum point to V-cut . 11

Figure 5 – Allowance of position off-set of V-cuts on front and back surfaces . 11

Figure 6 – PWB board with symbol mark, solder resist, copper foil and plating . 12

Figure 7 – Positions of component insertion holes . 13

Figure 8 – Distance between the wall of a hole to the board edge . 14

Figure 9 – Hole wall and the minimum designed spacing to the inner conductor . 15

Figure 10 – Width of finished conductor . 16

Figure 11 – Distance between finished conductors . 17

Figure 12 – Thickness of the insulating layer . 17

Figure 13 – Distance between centres of terminals of printed contacts . 18

Figure 14 – Terminal width of a printed contact . 18

Figure 15 – Shift of the centre of printed contacts on front and back sides of a board . 19

Figure 16 – Foot print . 19

Figure 17– Pad width of a footprint . 20

Figure 18 – Allowance of pad diameter of BGA/CSP formed of conductor only . 20

Figure 19 – Pad diameter (d) of BGA/CSP formed at the opening of solder resist . 21

Figure 20 – Examples of fiducial mark and component positioning mark . 21

Figure 21-1 – Minimum land width on the outer layer . 23

Figure 21-2 – Minimum land width on the inner layer with a plated through-hole . 23

Figure 21-3 – Allowable area of land break . 24

Figure 22 – Exposure of conductor . 25

Figure 23 – Minimum land width caused by the shift of solder resist . 25

Figure 24 – The overlap, smear and shift of solder resist . 26

Figure 25 – Examples . 26

Figure 26 – Example of measling . 27

Figure 27 – Examples of crazing . 28

Figure 28 – Missing of conductor . 28

Figure 29 – Conductor residue . 28

– 4 – PAS 62326-20 IEC:2011(E)

Figure 30 – Land. 29

Figure 31 – Defects in a pad of a footprint . 29

Figure 32 – Defects in BGA/CSP mounting pads . 30

Figure 33 – The areas to be checked for defects of a printed contact . 31

Figure 34 – Defects in a printed contact . 31

Figure 35 – Defect on a plating of a component mounting hole . 33

Figure 36-1 – Resin smear . 34

Figure 36-2 – Corner crack . 35

Figure 36-3 – Barrel crack . 35

Figure 36-4 – Foil crack . 35

Figure 37 – The relations between resistance and width, thickness and temperature

of conductor . 36

Figure 38 – Temperature rise as functions of width and thickness of conductor and

current . 37

Table 1 – Application and classification . 8

Table 2 – Panel dimensions (informative purpose) . 10

Table 3– Allowance of dimensions . 10

Table 4 – Allowance of the distances from the datum point to perforation and slit . 11

Table 5 – Allowance for the distance from the datum point to the center of the V-cut . 12

Table 6 – Total thickness and its allowance . 12

Table 7 – Allowance of holes for component insertion . 13

Table 8 – Position allowance of component insertion holes . 13

Table 9 – Distance between a hole wall and board edge . 14

Table 10 – Minimum clearance between the hole wall and the inner layer conductor . 14

Table 11 – Allowance of conductor width . 16

Table 12 – Allowance of the distance between conductors . 16

Table 13 – Distance between conductor and board edge . 17

Table 14 – Allowance of the terminal width of a printed contact . 18

Table 15 – Allowance of the distance between the centres of two pads . 19

Table 16 – Allowance of the width of a pad of a footprint . 20

Table 17 – Pad diameter and its allowance for BGA/CSP . 20

Table 18 – Allowance of the pad diameter (d) of BGA/CSP formed at the opening of

solder resist . 21

Table 19 – Shapes and sizes of typical fiducial marks and component positioning

marks . 22

Table 20 – Minimum thickness of copper plating . 22

Table 21 – Minimum land width . 23

Table 22 – Minimum land width . 25

Table 23 – The overlap, smear and shift of solder resist over a fool print . 26

Table 24 – Allowance of the area of a defect, remaining width and protrusion of a

land . 29

Table 25 – Defect of a pad of a footprint . 30

Table 26 – Defects in BGA/CSP mounting pads . 30

Table 27 – Defects in a printed contact . 32

PAS 62326-20 IEC:2011(E) – 5 –

Table 28 – Allowance in horizontal sectioning . 34

Table 29 – Specification and test methods . 38

Table A.1 – The relation between thermal conductive parameter (W/(mK)) and heat

transfer coefficient parameter . 49

Table A.2 – The relation between thermal conductive parameter (W/(mK)) and heat

transfer coefficient parameter . 49

– 6 – PAS 62326-20 IEC:2011(E)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

PRINTED BOARDS –

Part 20: Electronic circuit board for high-brightness LEDs

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization

comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to

promote international co-operation on all questions concerning standardization in the electrical and

electronic fields. To this end and in addition to other activities, IEC publishes International Standards,

Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter

referred to as “IEC Publication(s)”). Their preparation is entrusted to technical committees; any IEC National

Committee interested in the subject dealt with may participate in this preparatory work. International,

governmental and non-governmental organizations liaising with the IEC also participate in this preparation.

IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with

conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has

representation from all interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated

in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage

or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard, but made

available to the public.

IEC-PAS 62326-20 was submitted by the JPCA (Japan Electronics Packaging and Circuits

Association) and has been processed by IEC technical committee 91: Electronics assembly

technology.

PAS 62326-20 IEC:2011(E) – 7 –

It is based on JPCA-TMC-LED01S-2010. It is published as a double-logo PAS and JPCA.

The text of this PAS is based on the This PAS was approved for

following document: publication by the P-members of the

committee concerned as indicated in

the following document

Draft PAS Report on voting

91/926/PAS 91/942A/RVD

Following publication of this PAS, which is a pre-standard publication, the technical

committee or subcommittee concerned may transform it into an International Standard.

This PAS shall remain valid for an initial maximum period of 3 years starting from the

publication date. The validity may be extended for a single period up to a maximum of

3 years, at the end of which it shall be published as another type of normative document, or

shall be withdrawn.

A list of all the parts in the IEC 62326 series, under the general title Printed boards, can be

found on the IEC website.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct

understanding of its contents. Users should therefore print this document using a

colour printer.

– 8 – PAS 62326-20 IEC:2011(E)

PRINTED BOARDS –

Part 20: Electronic circuit board for high-brightness LEDs

1 Scope

This PAS specifies the properties of the electronic circuit board for high-brightness LEDs

(hereafter described as “ECB”).

NOTE Standards relevant to the present standards are given below.

JPCA-TD01 Terms and definitions for printed circuits

JIS C 5603 Terms and definitions for printed circuits

2 Terms and definitions

For the purpose of this document, the terms used in this PAS shall be in accordance with

JPCA-TD01 and JIS C 5603, unless otherwise specified.

3 Classification and class of the ECB

The ECB specified in this PAS shall satisfy the specification of (A) to (C) in Table 1 in the

following way. The materials used in the materials of PWB are not specified; however, they

shall be agreed upon between user and supplier depending on the application area of the

boards in question.

Table 1 – Application and classification

Small Thermal Heat

Classification

classification conductivity transfer

Definition

Definition

(thermal parameter parameter

(insulation

conductivity)

property) W/(mK) W/(m K)

I No specification

<1 <10

A Standard boards Ⅱ Electric strength <1,000 V

Ⅲ Electric strength 1,000 V≤

No specification

Ⅰ

Thermal

Electric strength <1,000 V

B conductive Ⅱ

boards

1≤ <10

Electric strength 1,000 V≤

Ⅲ

No specification

Ⅰ

High thermal

C conductive Ⅱ Electric strength <1,000 V

boards

1≤ 10≤

Electric strength 1,000 V≤

Ⅲ

PAS 62326-20 IEC:2011(E) – 9 –

Heat Radiation A B C

Resin type substrate (CEM-3, FR-4, FR-5 ) Resin type substrate (with thermal via)

Flexible type substrate High thermal conductive resin substrate

Metal core substrate

Classsification by base materials

Metal base substrate

Ceramic type substrate

Conventional substrate for discreat type electronic parts mounted boards

Classification by electronic circuit boards Substrate for semiconductor package

Substrate for Chip on Board

Assistant lighting lamp

Lamp substitute for halogen lamp

Lamp substitute for fluorescent lamp substitution

Classification by final products

Lamp substitute for filament lamp

Street lamp

Lamp substitute for HID

Insulation class Ⅰ Ⅱ Ⅲ Ⅰ Ⅱ Ⅲ Ⅰ Ⅱ Ⅲ

Figure 1 – Example of classification and their application by base materials,

electronic circuit boards and final products

4 Design rules and allowance

4.1 Panel and board sizes

4.1.1 Board size (for reference only)

The size of the board of the product (axb) illustrated in Figure 2 shall be selected so that

the boards can be arranged efficiently within a panel with a size specified in Table 2. Or, a

proper panel with a size given in the table shall be selected so as to satisfy the required

efficient arrangement of the boards.

Table 1. PWB

Board size of the product: a x b

Space between board and

panel edges: c ,c ,c ,c

1 2 3 4

Space between boards: e ,e

1 2

Figure 2 – Board arrangement in a panel

– 10 – PAS 62326-20 IEC:2011(E)

Table 2 – Panel dimensions (informative purpose)

mm

Division

Size of CCL (copper

clad laminate) panel

4 6 8 9

1 000 × 1 000 500 × 500 333 × 500 250 × 500 333 × 333

333 × 600

1 000 × 1 200 500 × 600 300 × 500 333 × 400

400 × 500

4.1.2 Allowance of dimensions

The allowance of dimensions of a board or a panel is given in Table 3.

Table 3– Allowance of dimensions

mm

Longitudinal size Allowance

≤ 100 ±0,2

Add 0,1 for each 50 exceeding a length of 100.

100<

4.1.3 Perforation and slit

The perforation and slit are shown in Figure 3. The allowance of the distances from the

datum point to the center of the cut of the perforation and slit is given in Table 4.

Figure 3 – Distances from the datum point to perforation and slit

PAS 62326-20 IEC:2011(E) – 11 –

Table 4 – Allowance of the distances from the datum point to perforation and slit

mm

Distances from the datum

Allowance

point to perforation and slit

≤ 100 ±0,2

100 < Add 0,1 for each 50 beyond a length of 100.

4.1.4 V-cut

The V-cut is shown in Figure 4. The allowance of the distance from the reference datum to

the center of cut of the V (g to g ) is given in Table 5. The allowance of the deviation of the

1 4

position of the V-cut on the front and back planes is 0,2 mm, and the allowance of the uncut

thickness of the board is the sum of the allowance of the board thickness ±0,1 mm.

Board Peripheral

V-cut

Datum point

Figure 4 – Distance from the datum point to V-cut

mm

Insulating board

Figure 5 – Allowance of position off-set of V-cuts on front and back surfaces

– 12 – PAS 62326-20 IEC:2011(E)

Table 5 – Allowance for the distance from the datum point to the center of the V-cut

Distance from the datum

point to the center of the Allowance

V-cut

≤100 ±0,2

>100 Add 0,1 for each 50 mm exceeding a length over 100 mm

4.2 Total board thickness

4.2.1 Total board thickness and its allowance

The allowance of the total board thickness (t) of a board with solder resist and symbol

marks as shown in Figure 6 is given in Table 6.

Solder resist

Symbol mark

Plating

Copper foil

Figure 6 – PWB board with symbol mark, solder resist, copper foil and plating

Table 6 – Total thickness and its allowance

mm

Total thickness

(center value of the final board) Allowance

mm

+ 0,10

≤ 0,3 to < 0,5

- 0,05

≤ 0,5 to < 0,8 ±0,10

≤ 0,8 to < 1,10 ±0,15

≤ 1,10 to < 1,40 ±0,17

≤ 1,40 to < 2,00 ±0,19

≤ 2,00 ±10 %

PAS 62326-20 IEC:2011(E) – 13 –

4.3 Holes

4.3.1 Insertion holes and vias

(1) Allowance of component insertion holes

Allowance of component insertion holes is given in Table 7. The allowance given in this

table is not applicable to vias (through-hole vias, buried vias and blind vias). The allowance

of through-holes with a diameter less than 0,6 mm for insertion of a component and holes

for press-fit of a component is to be agreed between user and supplier.

Table 7 – Allowance of holes for component insertion

mm

Item Allowance

0,6 ≤ <2,0 ±0,10

Plated

through-hole

2,0 ≤ ±0,15

Non-plated through-hole

±0,10

(2) Position of a hole for component insertion

The center of a hole for component insertion should be at the cross point of the grid for

pattern design including the complementary grid lines used. The allowance of a component

→

insertion hole position, (| , j|), the deviation from the designed position in respect to

the datum point as shown in Figure 7 is given in Table 8.

Finished hole

Datum hole

Designed hole positin (X, Y)

Datum hole (0,0)

Outer line of multilayer PWB Datum line

Figure 7 – Positions of component insertion holes

Table 8 – Position allowance of component insertion holes

mm

Longer dimension of

Allowance

rectangular board

≤ 400 0,10

400< For board exceeding 400, add 0,05 for each additional 100

– 14 – PAS 62326-20 IEC:2011(E)

(3) Distance from the board edge to the wall of a hole

Distance from the board edge to the wall of a hole (d) is shown in Figure 8. The distance (d)

between the walls of a through-hole before plating and of a hole for component insertion

shall be larger than either 1,0 mm. The distance in the case of press hole formation shall be

in accordance with Table 9.

Figure 8 – Distance between the wall of a hole to the board edge

Table 9 – Distance between a hole wall and board edge

mm

Distance (j) between a component hole before plating and

Item

the via wall

HDI PWB ≤ 1,0 mm and also longer than the board thickness (t)

Standard PWB ≤ 1,5 mm and also longer than the board thickness (t)

(4) Minimum clearance between hole wall and the inner conductor

The minimum clearance between the hole wall and the inner conductor (k) as illustrated in

Figure 9 shall be 0,325 mm. If the distance 0,325 mm is guaranteed in the design of the

pattern, the minimum separation is guaranteed.

Table 10 – Minimum clearance between the hole wall and the inner layer conductor

Minimum clearance between hole wall and the inner layer

conductor

Item

Standard value Minimum value

Component

0,5

hole

HDI PWB 0,25

Via 0,30

Component

0,5

hole

Standard PWB 0,30

Via 0,35

PAS 62326-20 IEC:2011(E) – 15 –

Insulating

Copper foil

board

Through hole

plating

Figure 9 – Hole wall and the minimum designed spacing to the inner conductor

4.3.2 Datum hole

(1) Allowance of a datum hole

+0,10

The allowance of a datum hole shall be ±0,05 mm, or mm. A through hole without wall

−0,00

plating shall be used as a datum hole.

4.3.3 Assembly hole (a through-hole without wall plating)

(1) Allowance of an assembly hole

The allowance of an assembly hole shall be ±0,10 mm.

(2) Allowance of the position of an assembly hole

The allowance of the position of an assembly hole shall be in accordance with the Table 8

of 4.3.1 (2).

(3) Distance between an assembly hole and the board edge

The distance between an assembly hole and the board edge shall be larger than 2,0 mm. In

case the distance is less than 2,0 mm, the distance shall be agreed between user and

supplier.

(4) The distance between an assembly hole and the inner conductor

The distance between the wall of an assembly hole and the inner conductor shall be larger

than 1,0 mm.

4.4 Conductor

4.4.1 Width of conductor pattern and its allowance

The allowance of the formed conductor width as illustrated in Figure 10 shall be in

accordance with Table 11. The allowance of the finishied conductor pattern specifically

designed for impedance control shall be agreed between the user and supplier.

– 16 – PAS 62326-20 IEC:2011(E)

Table 11 – Allowance of conductor width

Conductor Allowance Conductor with

a

thickness (mm) for reference

50 <75 ± 25 15 to 20

± 30 20 to 40

7500 <100

100 <300 ± 50 30 to 50

300 ± 100 40 to 70

± 150 70

Thick copper foil

± 200 105

circuits

± 300 140

a

The conductor thickness is the copper foil thickness plus the thickness of plated copper.

Conductor

Insulating

substrate

Figure 10 – Width of finished conductor

4.4.2 Distance between conductors and its allowance

The allowance of the distance between conductors (m) shall be as given in Table 12. The

allowance of the finishied conductor pattern specifically designed for impedance control

shall be agreed between the user and supplier.

Table 12 – Allowance of the distance between conductors

Allowance Conductor with

Conductor

a

thickness (mm) for reference

50 <75 ± 25 15 to 20

± 30 20 to 40

7500 <100

± 50 30 to 50

100 <300

300 ± 100 40 to 70

a

The conductor thickness is the copper foil thickness plus the thickness of plated copper.

PAS 62326-20 IEC:2011(E) – 17 –

Conductor

Insulating

substrate

Figure 11 – Distance between finished conductors

4.4.3 Distance between conductor and board edge

The distance between conductor and board edge shall be larger than 0,5 mm. The distance

for the case of pressing shall be as given in Table 13 excluding the board printed contact

portions.

Table 13 – Distance between conductor and board edge

Distance between conductor and

Board thickness

board edge

< 0,8 0,5≤

0,8≤ ≤2,0 More than the board thickness

4.4.4 Thickness of the insulating layer

The thickness of an insulating layer is illustrated in Figure 12.

Conductor

Insulating

substrate

(1) (2) (3)

NOTE In case the surface of copper foil is roughened, the thickness of t he insulating substrate is the minimum

distance applicable to the substrate.

Figure 12 – Thickness of the insulating layer

– 18 – PAS 62326-20 IEC:2011(E)

4.5 Printed contact

4.5.1 Allowance of the distance between the centres of two adjacent printed

contacts

The allowance of the distance between the centres of two adjacent printed contacts (p,p )

n

as illustrated in Figure 13 shall be ±0,10 mm. Add 0,01 mm for each additional 20 mm in

case the distance between the centres of terminals exceeds 100 mm.

Figure 13 – Distance between centres of terminals of printed contacts

4.5.2 Allowance of the terminal width of printed contacts

The allowance of the terminal width of printed contacts (w) as illustrated in Figure 14 is

specified in Table 14.

Figure 14 – Terminal width of a printed contact

Table 14 – Allowance of the terminal width of a printed contact

mm

Terminal width Allowance

≤ 1,0 ±0,05

1,0< ±0,10

4.5.3 Shift of the centre of printed contacts on front and back sides of a board

The allowance of the shift of the centre of printed contacts on front and back sides of a

board (q) as illustrated in Figure 15 shall be ±0,20 mm.

PAS 62326-20 IEC:2011(E) – 19 –

Printed contact

Insulating

substrate

Figure 15 – Shift of the centre of printed contacts on front and back sides of a board

4.6 Footprint

4.6.1 Allowance of the distance between the centers of two pads

The allowance of the distance between the centres of two adjacent pads (S ) and of two

adjascent parallel pads (S) as illustrated in Figure 16 is specified in Table 15.

Figure 15. Footprint

Figure 16 – Foot print

Table 15 – Allowance of the distance between the centres of two pads

mm

Distance between

Allowance

centres

S ±0,03

S ±0,05

4.6.2 Allowance of the width of a pad

The allowance of the width of a pad of a footprint (w) as illustrated in Figure 17 is specified

in Table 16. The allowance for a pad narrower than 0,15 mm shall be agreed between the

user and supplier.

– 20 – PAS 62326-20 IEC:2011(E)

Insulating

substrate

Figure 17– Pad width of a footprint

Table 16 – Allowance of the width of a pad of a footprint

mm

Pad width Allowance

0,15 < ≤0,35 ±0,04

0,35< ±0,06

4.6.3 Pad diameter and its allowance for BGA/CSP

The allowance of pad diameter for BGA/CSP is specified in 4.6.3 (1) and 4.6.3 (2) specified

below.

(1) The pattern is shown in Figure 18. The allowance of the pad diameter (d) of BGA/CSP

made of conductor only is given in Table 17.

Pad Pad

Figure 18 Pad diameter of BGA/CSP formed of conductor only

Conductor

Insulating

Insulating Conductor

substrate

substrate

Figure 18 – Allowance of pad diameter of BGA/CSP formed of conductor only

Table 17 – Pad diameter and its allowance for BGA/CSP

Allowance of pad Conductor thickness

Item

diameter (mm)

(µm, for reference)

HDI PWB + 0,02 – 0,03 20 to 30

Standard PWB + 0,03 – 0,05 30 to 50

PAS 62326-20 IEC:2011(E) – 21 –

(2) The pattern is shown in Figure 19. The allowance of the pad diameter (d) of BGA/CSP

formed at the opening of solder resist is given in Table 18.

Table 18 – Allowance of the pad diameter (d) of BGA/CSP formed

at the opening of solder resist

mm

Item Allowance

HDI PWB ± 0,03

Standard PWB ± 0,05

Solder resist

Pad

Solder resist

Conductor

Insulating board

Figure 19 – Pad diameter (d) of BGA/CSP formed at the opening of solder resist

4.7 Fiducial mark and the mark for component positioning

4.7.1 The typical form and the size of the fiducial mark and the mark for component

positioning as illustrated in Figure 20 are specified in Table 19.

Conponent positioning

k

Footprint

Fiducial

Multilayer PWB

Figure 20 – Examples of fiducial mark and component positioning mark

– 22 – PAS 62326-20 IEC:2011(E)

Table 19 – Shapes and sizes of typical fiducial marks

and component positioning marks

mm

Item Shape Diameter

Fiducial and component

Circle 1,0

positioning marks

4.7.2 Dimensional allowance of fiducial mark and component positioning mark

The dimensional allowance of fiducial mark and component positioning mark as illustrated

in Figure 21 is ±0,1 mm.

4.7.3 Position allowance of the component positioning mark and the farthest footprint from

the mark (u ,u ) as illustrated in Figure 21 shall be ±0,05 mm.

1 2

4.8 Interlayer connection

(1) Copper plating

The minimum thickness of copper plating on the wall of via and component insertion holes

is given in Table 20.

Table 20 – Minimum thickness of copper plating

a

Board thickness, or layer Minimum thickness of copper plating

thickness (mm) (µm)

2,4< Thickness shall be agreed between the

user and supplier.

1,0 < ≤2,4 15

0,5 < ≤1,0 12

0,5≤ 10

a

The measurement shall be made by optical observation of a microsectioned vertical cross section. Local

surface deviation is not accounted.

5 Quality

5.1 Gap between conductor and the wall of a component insertion hole or a via

The gap between conductor and the wall of a component insertion hole or a via, or the gap

between the inner conductor and the wall of a hole shall be larger than 0,13 mm.

5.2 Positional deviation between conductor layers of multilayer board

The deviation of conductor layers of multilayer board shall satisfy the conditions specified in

4.5.3, 5.1, and 5.3.

5.3 Minimum land width

The minimum land width on the most outer layer (w ) caused by the shift of land and the

) are specified in Table 21 (also see

hole, and the minimum land width on an inner layer (w

Figures 21-1 to 21-3).

PAS 62326-20 IEC:2011(E) – 23 –

Table 21 – Minimum land width

mm

a

Item Minimum land width

At the joint of land and

Minimum land width w ≧0,03

conductor

on outer layer

b

w

Other area θ≦90°

Case of non-conductive

w ≧0,05

component insertion hole

At the joint of land and

w ≧0,03

conductor

Minimum land width

on inner layer

c

w

2 Others (except laser

θ≦90°

d

drilled hole)

a

Regardless of the shape of a land.

b

Includes the thickness of through-hole plating.

c

Does not include the thickness of through-hole plating.

d

No break of inner land is allowed for a laser drilled hole.

Figure 21-1 – Minimum land width on the outer layer

Plated through hole

Figure 21-2 – Minimum land width on the inner layer with a plated through-hole

– 24 – PAS 62326-20 IEC:2011(E)

Figure 21-3 – Allowable area of land break

5.4 Surface treatment

5.4.1 Gold plating for printed contact

The gold plating for printed contact is generally plated of hard gold on the nickel plating.

1) Nickel plating: the thickness of nickel plating on a printed contact shall be more than

2,0 µm.

2) Gold plating: the hard gold shall be used for plating on a printed contact with a plating

thickness of more than 0,1 µm.

5.4.2 Other surface treatment

The details of other surface treatment including gold flush plating and solder coating

depends on the methods for interconnection (such as soldering or wire bonding). These

details shall be agreed by the user and supplier.

5.5 Defects of solder resist

1) The defects in a pad for BGA/CSP shall be in accordance with 4.6.3 (diameter and

allowance of pads for BGA/CCP).

2) Solder resist shall not have scratch, peeling, pin-hole, or foreign material. Solder resist

shall not have any bubble extending to two conductors.

3) Exposure of conductor after application of solder resist shall be in conformance to the

illustrations in Figure 22.

PAS 62326-20 IEC:2011(E) – 25 –

(Not acceptable)

(Acceptable)

Conductor Conductor

Solder resist

Solder resist

Insulating

Insulating

Conductor

Conductor

Solder Land Solder resist

Land

Insulating

In

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...