IEC 63378-6:2026

(Main)Thermal standardization on semiconductor packages - Part 6: Thermal resistance and capacitance model for transient temperature prediction at junction and measurement points

Thermal standardization on semiconductor packages - Part 6: Thermal resistance and capacitance model for transient temperature prediction at junction and measurement points

IEC 63378-6:2026 specifies a thermal resistance and capacitance model for semiconductor packages. This model is named the digital transformation using thermal resistance and capacitance (DXRC) model. It predicts transient temperature at junction and measurement points.

This document applies to semiconductor packages such as TO-252, TO-263, and HSOP. It supports single chip packages dissipated heat from single package surface.

Normalisation thermique des boîtiers de semiconducteurs - Partie 6: Modèle de résistance thermique et de capacité pour la prédiction de la température transitoire aux points de jonction et de mesure

L’IEC 63378-6:2026 spécifie un modèle de résistance thermique et de capacité pour les boîtiers de semiconducteurs. Ce modèle est appelé transformation numérique utilisant le modèle de résistance et de capacité thermiques (DXRC, Digital transformation using thermal resistance and capacitance). Il prédit la température transitoire aux points de jonction et de mesure.

Le présent document s’applique aux boîtiers de semiconducteurs tels que TO-252, TO-263 et HSOP. Il prend en charge les boîtiers monopuces dissipant la chaleur d’une seule surface du boîtier.

General Information

- Status

- Published

- Publication Date

- 03-Feb-2026

- Technical Committee

- SC 47D - Semiconductor devices packaging

- Drafting Committee

- WG 2 - TC 47/SC 47D/WG 2

- Current Stage

- PPUB - Publication issued

- Start Date

- 04-Feb-2026

- Completion Date

- 20-Feb-2026

Overview

IEC 63378-6:2026 is an international standard developed by the International Electrotechnical Commission (IEC), focusing on the thermal standardization of semiconductor packages. Specifically, this document defines a thermal resistance and capacitance model for predicting transient temperatures at the junction and measurement points of semiconductor packages. Referred to as the DXRC (Digital Transformation using thermal Resistance and Capacitance) model, this approach supports evaluating dynamic thermal performance, particularly for packages such as TO-252, TO-263, and HSOP, where heat dissipates from a single package surface.

By providing a standardized methodology for modeling and predicting thermal behavior, IEC 63378-6:2026 assists engineers, designers, and manufacturers in ensuring accurate, consistent thermal analysis, which is critical for the reliable operation and lifespan of electronic components.

Key Topics

- DXRC Thermal Model: The core of IEC 63378-6:2026 is the DXRC model, a compact network of thermal resistances and capacitances, specifically structured for transient temperature prediction within a semiconductor package.

- Transient Temperature Prediction: The standard details procedures for predicting how temperatures change over time at both the semiconductor junction and various measurement points, offering valuable insights for reliability assessments and design optimization.

- Applicable Package Types: The model is designed for common industry package types, including TO-252, TO-263, and HSOP, covering single chip packages with heat dissipation from the top surface.

- RC Topology: The DXRC model consists of the Near Junction Area RC (NJA-RC) and Measurement Points Area RC (MPA-RC), capturing essential heat transfer paths within a package.

- Optimization and Validation: Instructions are provided on calculating and optimizing RC values based on measurement, simulation, datasheet information, or other empirical junction temperature data.

- Support for CFD and System Design: The standard supports integration with computational fluid dynamics (CFD) analysis, reducing simulation times and resource requirements.

Applications

IEC 63378-6:2026 serves crucial roles in several areas of electronics design and manufacturing:

- Thermal Design and Management: Enables engineers to predict how semiconductor junction temperatures evolve in real-world use, facilitating better heat management and minimizing thermal failure risks.

- Reliability Testing: Provides a standardized modeling approach, ensuring repeatable and consistent thermal analysis, which is vital for qualification and reliability or stress testing of power semiconductors.

- Simulation Accuracy: Supports faster and more memory-efficient thermal simulations by employing compact thermal models that maintain accuracy for transient temperature responses.

- Quality Assurance: Helps manufacturers validate the thermal performance of semiconductor packages in compliance with international standards, ensuring product consistency across markets.

- Integration with Advanced Tools: The DXRC model aligns with modern digital transformation workflows, enabling seamless use with electronic design automation (EDA) and CFD tools, enhancing the efficiency of design verification processes.

Related Standards

For comprehensive thermal analysis and standardization, consider the following related documents:

- IEC 63378-6 Series:

- Parts 1 and 2 focus on model creation methods using semiconductor datasheets and measurement data.

- IEC 60050-521:

- Provides fundamental definitions for terms like thermal resistance and capacitance in semiconductor technology.

- IEC/TR 60890:

- Addresses thermal resistance calculations for electrical equipment in enclosures.

Adhering to IEC 63378-6:2026 and related standards ensures best practices in semiconductor thermal management, contributing to improved product performance, reliability, and compliance with global market requirements.

For the latest updates and future amendments, visit the IEC webstore.

Buy Documents

IEC 63378-6:2026 - Thermal standardization on semiconductor packages - Part 6: Thermal resistance and capacitance model for transient temperature prediction at junction and measurement points Released:2/4/2026

IEC 63378-6:2026 - Normalisation thermique des boîtiers de semiconducteurs - Partie 6: Modele de résistance thermique et de capacité pour la prédiction de la température transitoire aux points de jonction et de mesure Released:2/4/2026

IEC 63378-6:2026 - Thermal standardization on semiconductor packages - Part 6: Thermal resistance and capacitance model for transient temperature prediction at junction and measurement points Released:2/4/2026

Frequently Asked Questions

IEC 63378-6:2026 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Thermal standardization on semiconductor packages - Part 6: Thermal resistance and capacitance model for transient temperature prediction at junction and measurement points". This standard covers: IEC 63378-6:2026 specifies a thermal resistance and capacitance model for semiconductor packages. This model is named the digital transformation using thermal resistance and capacitance (DXRC) model. It predicts transient temperature at junction and measurement points. This document applies to semiconductor packages such as TO-252, TO-263, and HSOP. It supports single chip packages dissipated heat from single package surface.

IEC 63378-6:2026 specifies a thermal resistance and capacitance model for semiconductor packages. This model is named the digital transformation using thermal resistance and capacitance (DXRC) model. It predicts transient temperature at junction and measurement points. This document applies to semiconductor packages such as TO-252, TO-263, and HSOP. It supports single chip packages dissipated heat from single package surface.

IEC 63378-6:2026 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 63378-6:2026 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 63378-6 ®

Edition 1.0 2026-02

INTERNATIONAL

STANDARD

Thermal standardization on semiconductor packages -

Part 6: Thermal resistance and capacitance model for transient temperature

prediction at junction and measurement points

ICS 31.080.01 ISBN 978-2-8327-1001-2

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or

by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either

IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright

or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local

IEC member National Committee for further information.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - IEC Products & Services Portal - products.iec.ch

webstore.iec.ch/advsearchform Discover our powerful search engine and read freely all the

The advanced search enables to find IEC publications by a

publications previews, graphical symbols and the glossary.

variety of criteria (reference number, text, technical With a subscription you will always have access to up to date

committee, …). It also gives information on projects, content tailored to your needs.

replaced and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published containing more than 22 500 terminological entries in English

details all new publications released. Available online and and French, with equivalent terms in 25 additional languages.

once a month by email. Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer

Service Centre: sales@iec.ch.

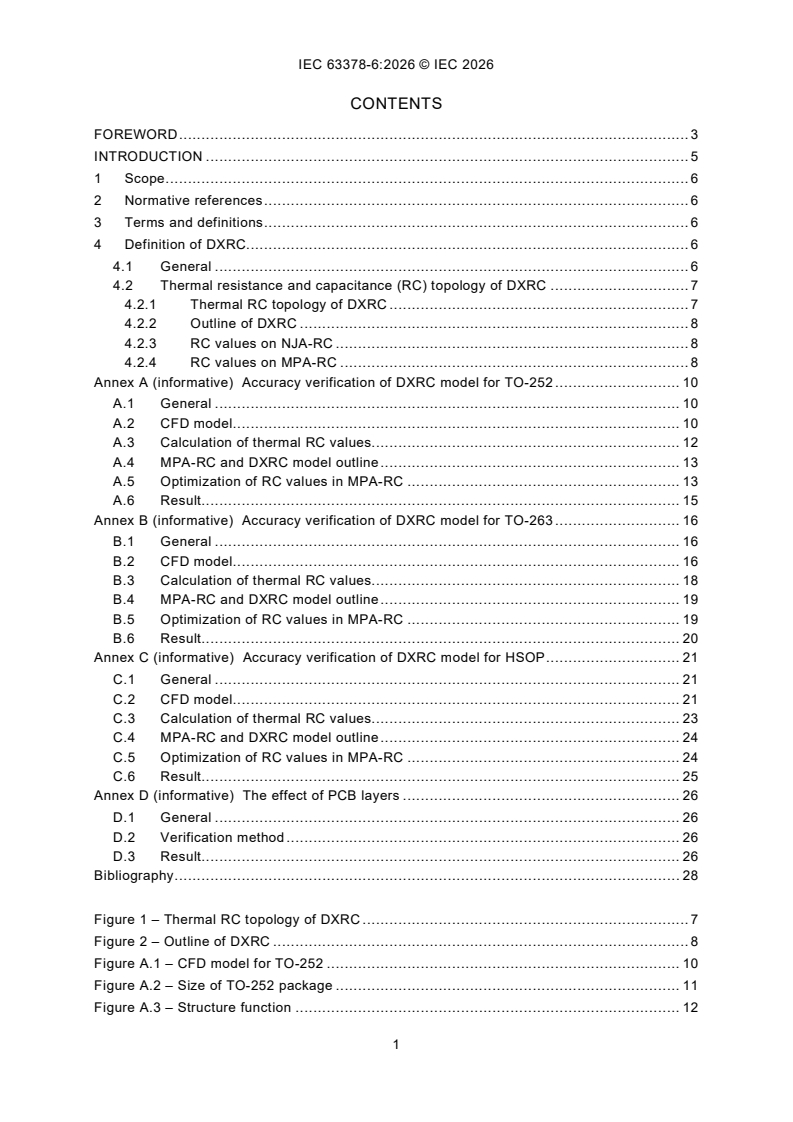

CONTENTS

FOREWORD . 3

INTRODUCTION . 5

1 Scope . 6

2 Normative references . 6

3 Terms and definitions . 6

4 Definition of DXRC. 6

4.1 General . 6

4.2 Thermal resistance and capacitance (RC) topology of DXRC . 7

4.2.1 Thermal RC topology of DXRC . 7

4.2.2 Outline of DXRC . 8

4.2.3 RC values on NJA-RC . 8

4.2.4 RC values on MPA-RC . 8

Annex A (informative) Accuracy verification of DXRC model for TO-252 . 10

A.1 General . 10

A.2 CFD model. 10

A.3 Calculation of thermal RC values. 12

A.4 MPA-RC and DXRC model outline . 13

A.5 Optimization of RC values in MPA-RC . 13

A.6 Result. 15

Annex B (informative) Accuracy verification of DXRC model for TO-263 . 16

B.1 General . 16

B.2 CFD model. 16

B.3 Calculation of thermal RC values. 18

B.4 MPA-RC and DXRC model outline . 19

B.5 Optimization of RC values in MPA-RC . 19

B.6 Result. 20

Annex C (informative) Accuracy verification of DXRC model for HSOP . 21

C.1 General . 21

C.2 CFD model. 21

C.3 Calculation of thermal RC values. 23

C.4 MPA-RC and DXRC model outline . 24

C.5 Optimization of RC values in MPA-RC . 24

C.6 Result. 25

Annex D (informative) The effect of PCB layers . 26

D.1 General . 26

D.2 Verification method . 26

D.3 Result. 26

Bibliography . 28

Figure 1 – Thermal RC topology of DXRC . 7

Figure 2 – Outline of DXRC . 8

Figure A.1 – CFD model for TO-252 . 10

Figure A.2 – Size of TO-252 package . 11

Figure A.3 – Structure function . 12

Figure A.4 – Result of verification . 15

Figure B.1 – CFD model for TO-263 . 16

Figure B.2 – Size of TO-263 package . 17

Figure B.3 – Structure function . 18

Figure B.4 – Result of verification . 20

Figure C.1 – CFD model for HSOP . 21

Figure C.2 – Size of HSOP package . 22

Figure C.3 – Structure function . 23

Figure C.4 – Result of verification . 25

Figure D.1 – Comparisons of temperature rise between the detailed model and the

DXRC model . 27

Table A.1 – Material attributes . 11

Table A.2 – Thermal resistances in NJA-RC . 12

Table A.3 – Thermal capacitances in NJA-RC . 13

Table A.4 – Input variables . 14

Table A.5 – Optimized RC values . 14

Table B.1 – Material attributes . 17

Table B.2 – Thermal resistances in NJA-RC . 18

Table B.3 – Thermal capacitances in NJA-RC . 19

Table B.4 – Optimized RC values . 20

Table C.1 – Material Attributes . 22

Table C.2 – Thermal resistances in NJA-RC . 23

Table C.3 – Thermal capacitances in NJA-RC . 24

Table C.4 – Optimized RC values . 25

Table D.1 – Combination of the coverages of copper layers . 26

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

Thermal standardization on semiconductor packages -

Part 6: Thermal resistance and capacitance model for transient

temperature prediction at junction and measurement points

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC Publication(s)”). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for

Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence between

any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) IEC draws attention to the possibility that the implementation of this document may involve the use of (a)

patent(s). IEC takes no position concerning the evidence, validity or applicability of any claimed patent rights in

respect thereof. As of the date of publication of this document, IEC had not received notice of (a) patent(s), which

may be required to implement this document. However, implementers are cautioned that this may not represent

the latest information, which may be obtained from the patent database available at https://patents.iec.ch. IEC

shall not be held responsible for identifying any or all such patent rights.

IEC 63378-6 has been prepared by subcommittee 47D: Semiconductor devices packaging, of

IEC Technical Committee 47: Semiconductor devices. It is an International Standard.

The text of this International Standard is based on the following documents:

Draft Report on voting

47D/991/CDV 47D/998/RVC

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in

accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available

at www.iec.ch/members_experts/refdocs. The main document types developed by IEC are

described in greater detail at www.iec.ch/publications.

A list of all parts in the IEC 63378 series, published under the general title Thermal

standardization on semiconductor packages, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the

stability date indicated on the IEC website under webstore.iec.ch in the data related to the

specific document. At this date, the document will be

– reconfirmed,

– withdrawn, or

– revised.

INTRODUCTION

The IEC 63378-6 series is composed of the following parts:

1,2

– IEC 63378-6-1 [1] defines the model creation method using a datasheet of semiconductor

devices.

– IEC 63378-6-2 defines the model creation method using measurement data of

semiconductor devices.

The IEC 63378-6 series includes subjects such as the definition of a new thermal compact

model for thermal transient analysis of semiconductor packages, model creation methods,

accuracy assessment of these models, etc.

___________

Numbers in square brackets refer to the Bibliography.

Under preparation. Stage at the time of publication: IEC APUB 63378-6-1:2026.

Under development.

1 Scope

This part of IEC 63378 specifies a thermal resistance and capacitance model for semiconductor

packages. This model is named the digital transformation using thermal resistance and

capacitance (DXRC) model. It predicts transient temperature at junction and measurement

points.

This document applies to semiconductor packages such as TO-252, TO-263, and HSOP. It

supports single chip packages dissipated heat from single package surface.

2 Normative references

There are no normative references in this document.

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminology databases for use in standardization at the following

addresses:

– IEC Electropedia: available at https://www.electropedia.org/

– ISO Online browsing platform: available at https://www.iso.org/obp

3.1

thermal resistance

quotient of the difference between the virtual temperature of the device and the temperature of

a stated external reference point, by the steady-state power dissipation in the device

[SOURCE: IEC 60050-521:2002 [3], 521-05-13]

3.2

thermal capacitance

ability of a material to store thermal energy, calculated by product of specific heat and density

3.3

thermal resistance from junction to case top

θ

JC

thermal resistance between a junction and a semiconductor package surface

3.4

thermal RC topology

thermal network consisting of several thermal resistances, capacitances, and nodes

4 Definition of DXRC

4.1 General

Compact thermal models (CTMs) are commonly used for computer fluid dynamics (CFD)

analysis in semiconductor and electronics industries. Using CTMs reduces calculation time and

memory usage. However, there are few methods for CTMs which can support transient analysis

and estimation of measurement points. DXRC is a method to create CTMs which supports

predicting the temperature at a junction and arbitrary measurement points.

4.2 Thermal resistance and capacitance (RC) topology of DXRC

4.2.1 Thermal RC topology of DXRC

Thermal RC topology of DXRC shall be defined as in Figure 1. It has two RC circuit areas

named Near Junction Area – RC (NJA-RC) and Measurement Points Area – RC (MPA-RC).

NJA-RC contains a junction node named T and other nodes linking from it named from T to

J 1

T . These nodes are completely inside nodes, thus they do not have any surfaces which

N

exchange heat with the external environment. Each node has one thermal capacitance and is

connected to a neighbouring node. Only T generates heat. The end node of NJA-RC is

J

via a thermal resistance. MPA-RC contains

connected to the top node of MPA-RC named T

CORE

three nodes named T , T and T which are describing measurement points and five nodes

C L S

named T , T , T , T and T which are connecting to external 3D models via CTM

BI BO LB SB TOP

surfaces. This topology is defined according to the heat flow paths from junction to package

surfaces. Note that this thermal RC topology contains only thermal property inside a package,

namely, the thermal property of PCB and other surrounding environments is not contained.

Key

T thermal node representing the junction in a thermal RC topology

J

T internal thermal node as a branch point, not representing any actual location

CORE

T internal thermal nodes between T and T , not representing any actual locations, a natural number

N J CORE

starting from the one closest to T for N

J

T thermal node representing an arbitrary position on the top surface of the package, with a surface based on

TOP

the top surface of the package, that exchanges heat with the surrounding environment

T internal thermal node representing at an arbitrary position on the bottom metal surface of the package

C

T thermal node with a surface based on the metal surface directly under the chip, which exchanges heat with

BI

the surrounding environment

T thermal node with a surface based on the bottom resin surface of the package, which exchanges heat with

BO

the surrounding environment

T internal thermal node representing an arbitrary position on the lead terminals

L

T thermal node with surfaces based on the bottom surface of the lead terminals, which exchange heat with

LB

the surrounding environment

T internal thermal node representing an arbitrary position on a metal heat spreader of the package

S

T thermal node with a surface based on the bottom surface of a part of a metal heat spreader, which

SB

exchanges heat with the surrounding environment

Figure 1 – Thermal RC topology of DXRC

4.2.2 Outline of DXRC

DXRC has T , T , T , T and T as surface nodes. These surfaces should be defined

BI BO LB SB TOP

according to outline of semiconductor packages. An example is shown in Figure 2.

Figure 2 – Outline of DXRC

4.2.3 RC values on NJA-RC

RC values contained in NJA-RC shall be calculated by a common method [1]. Measurement,

simulation, datasheet of semiconductor packages and any other rising temperature data of

junction may be used as input data. The thermal resistance range between T and T should

J N

be smaller than between T and T in order to add MPA-RC later.

J C

4.2.4 RC values on MPA-RC

RC values on MPA-RC shall be optimized to minimize the error defined by Equations (1) and

(2). Other methods such as curve fitting may be used if equivalent optimization is possible.

Additionally, any optimization algorithm may be used. The input data are temperature rises at

a junction and at least one measurement point. This temperature data is the same as input data

at 4.2.3.

T tT− t

() ()

input DXRC

eT_ t ×100

()

(1)

J

Tt

()

input

eT_ t T t− T t

() () ()

(2)

M input DXRC

where

e_T (t) and e_T (t) are errors at time t between the input data and the result of DXRC

J M

for T and measurement points respectively;

J

T (t) is the temperature of input data;

input

T (t) is the estimated temperature by DXRC;

DXRC

t in the m-th power of 10 is calculated by Equation (3).

=

=

1,5

n

mm+1 m

(3)

tn=10+ 10 −×10 (=1, 2,,1 0)

( )

where

m is the integer number.

Both data can be calculated using linear interpolation or other methods if the times of the data

do not correspond to the times defined in Equation (3). Since error is dependent on surrounding

environments such as PCBs, input data should be prepared according to them. For details,

please refer to Annex A to Annex D.

Annex A

(informative)

Accuracy verification of DXRC model for TO-252

A.1 General

The result of the accuracy verification of a DXRC model is shown in this Annex A. The input

data was obtained by the calculation of a semiconductor package model shown in Figure A.1,

which was reproduced in detail.

A.2 CFD model

The CFD model shown in Figure A.1 was used. A semiconductor package (TO-252) shown in

Figure A.2 was mounted on a printed circuit board (PCB) which was located on a cold plate via

a thermal interface material (TIM). The package model consists of the chip, die attach, spreader,

lead terminals, and mold. The PCB consists of copper and dielectric layers, and vias. Other

spaces in the solution domain were occupied by air. Their material specifications are shown in

Table A.1. The T located on the exposed spreader was used as a measurement poin

...

IEC 63378-6 ®

Edition 1.0 2026-02

NORME

INTERNATIONALE

Normalisation thermique des boîtiers de semiconducteurs -

Partie 6: Modèle de résistance thermique et de capacité pour la prédiction de la

température transitoire aux points de jonction et de mesure

ICS 31.080.01 ISBN 978-2-8327-1001-2

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et

les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Recherche de publications IEC - IEC Products & Services Portal - products.iec.ch

webstore.iec.ch/advsearchform Découvrez notre puissant moteur de recherche et consultez

La recherche avancée permet de trouver des publications gratuitement tous les aperçus des publications, symboles

IEC en utilisant différents critères (numéro de référence, graphiques et le glossaire. Avec un abonnement, vous aurez

texte, comité d’études, …). Elle donne aussi des toujours accès à un contenu à jour adapté à vos besoins.

informations sur les projets et les publications remplacées

ou retirées. Electropedia - www.electropedia.org

Le premier dictionnaire d'électrotechnologie en ligne au

IEC Just Published - webstore.iec.ch/justpublished monde, avec plus de 22 500 articles terminologiques en

Restez informé sur les nouvelles publications IEC. Just anglais et en français, ainsi que les termes équivalents

Published détaille les nouvelles publications parues. dans 25 langues additionnelles. Egalement appelé

Disponible en ligne et une fois par mois par email. Vocabulaire Electrotechnique International (IEV) en ligne.

Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette

publication ou si vous avez des questions contactez-

nous: sales@iec.ch.

SOMMAIRE

AVANT-PROPOS . 3

INTRODUCTION . 5

1 Domaine d’application . 6

2 Références normatives . 6

3 Termes et définitions. 6

4 Définition de DXRC . 7

4.1 Généralités . 7

4.2 Topologie de résistance et de capacité (RC) thermique de DXRC . 7

4.2.1 Topologie RC thermique de DXRC . 7

4.2.2 Contours de DXRC . 8

4.2.3 Valeurs RC sur NJA-RC. 9

4.2.4 Valeurs RC sur la MPA-RC . 9

Annexe A (informative) Vérification de la précision du modèle DXRC pour TO-252 . 11

A.1 Généralités . 11

A.2 Modèle CFD . 11

A.3 Calcul des valeurs RC thermiques . 13

A.4 Contours du modèle MPA-RC et DXRC . 14

A.5 Optimisation des valeurs de RC dans la MPA-RC . 14

A.6 Résultat . 16

Annexe B (informative) Vérification de la précision du modèle DXRC pour TO-263 . 17

B.1 Généralités . 17

B.2 Modèle CFD . 17

B.3 Calcul des valeurs RC thermiques . 19

B.4 Contours du modèle MPA-RC et DXRC . 20

B.5 Optimisation des valeurs de RC dans la MPA-RC . 20

B.6 Résultat . 21

Annexe C (informative) Vérification de la précision du modèle DXRC pour HSOP . 22

C.1 Généralités . 22

C.2 Modèle CFD . 22

C.3 Calcul des valeurs RC thermiques . 24

C.4 Contours du modèle MPA-RC et DXRC . 25

C.5 Optimisation des valeurs de RC dans la MPA-RC . 25

C.6 Résultat . 26

Annexe D (informative) L’effet des couches de carte à circuit imprimé . 27

D.1 Généralités . 27

D.2 Méthode de vérification . 27

D.3 Résultat . 27

Bibliographie . 29

Figure 1 – Topologie RC thermique de DXRC . 8

Figure 2 – Contours de DXRC. 9

Figure A.1 – Modèle CFD pour TO-252 . 11

Figure A.2 – Taille du boîtier TO-252 . 12

Figure A.3 – Fonction de structure . 13

Figure A.4 – Résultat de la vérification . 16

Figure B.1 – Modèle CFD pour TO-263 . 17

Figure B.2 – Taille du boîtier TO-263 . 18

Figure B.3 – Fonction de structure . 19

Figure B.4 – Résultat de la vérification . 21

Figure C.1 – Modèle CFD pour HSOP . 22

Figure C.2 – Taille du boîtier HSOP . 23

Figure C.3 – Fonction de structure . 24

Figure C.4 – Résultat de la vérification . 26

Figure D.1 – Comparaisons d’échauffement entre le modèle détaillé et le modèle

DXRC. 28

Tableau A.1 – Attributs de matériaux . 12

Tableau A.2 – Résistances thermiques dans NJA-RC . 13

Tableau A.3 – Capacités thermiques dans NJA-RC . 14

Tableau A.4 – Variables d’entrée . 15

Tableau A.5 – Valeurs RC optimisées . 15

Tableau B.1 – Attributs de matériaux . 18

Tableau B.2 – Résistances thermiques dans NJA-RC . 19

Tableau B.3 – Capacités thermiques dans NJA-RC . 20

Tableau B.4 – Valeurs RC optimisées . 21

Tableau C.1 – Attributs de matériaux . 23

Tableau C.2 – Résistances thermiques dans NJA-RC . 24

Tableau C.3 – Capacités thermiques dans NJA-RC . 25

Tableau C.4 – Valeurs RC optimisées. 26

Tableau D.1 – Combinaison des couvertures des couches de cuivre . 27

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

____________

Normalisation thermique des boîtiers de semiconducteurs -

Partie 6: Modèle de résistance thermique et de capacité pour la prédiction

de la température transitoire aux points de jonction et de mesure

AVANT-PROPOS

1) La Commission Electrotechnique Internationale (IEC) est une organisation mondiale de normalisation composée

de l’ensemble des comités électrotechniques nationaux (Comités nationaux de l’IEC). L’IEC a pour objet de

favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de

l’électricité et de l’électronique. À cet effet, l’IEC – entre autres activités – publie des Normes internationales,

des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au public (PAS) et des

Guides (ci-après dénommés "Publication(s) de l’IEC"). Leur élaboration est confiée à des comités d’études, aux

travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les organisations

internationales, gouvernementales et non gouvernementales, en liaison avec l’IEC, participent également aux

travaux. L’IEC collabore étroitement avec l’Organisation Internationale de Normalisation (ISO), selon des

conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de l’IEC concernant les questions techniques représentent, dans la mesure du

possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux de l’IEC intéressés

sont représentés dans chaque comité d’études.

3) Les Publications de l’IEC se présentent sous la forme de recommandations internationales et sont agréées

comme telles par les Comités nationaux de l’IEC. Tous les efforts raisonnables sont entrepris afin que l’IEC

s’assure de l’exactitude du contenu technique de ses publications; l’IEC ne peut pas être tenue responsable de

l’éventuelle mauvaise utilisation ou interprétation qui en est faite par un quelconque utilisateur final.

4) Dans le but d’encourager l’uniformité internationale, les Comités nationaux de l’IEC s’engagent, dans toute la

mesure possible, à appliquer de façon transparente les Publications de l’IEC dans leurs publications nationales

et régionales. Toutes divergences entre toutes Publications de l’IEC et toutes publications nationales ou

régionales correspondantes doivent être indiquées en termes clairs dans ces dernières.

5) L’IEC elle-même ne fournit aucune attestation de conformité. Des organismes de certification indépendants

fournissent des services d’évaluation de conformité et, dans certains secteurs, accèdent aux marques de

conformité de l’IEC. L’IEC n’est responsable d’aucun des services effectués par les organismes de certification

indépendants.

6) Tous les utilisateurs doivent s’assurer qu’ils sont en possession de la dernière édition de cette publication.

7) Aucune responsabilité ne doit être imputée à l’IEC, à ses administrateurs, employés, auxiliaires ou mandataires,

y compris ses experts particuliers et les membres de ses comités d’études et des Comités nationaux de l’IEC,

pour tout préjudice causé en cas de dommages corporels et matériels, ou de tout autre dommage de quelque

nature que ce soit, directe ou indirecte, ou pour supporter les coûts (y compris les frais de justice) et les dépenses

découlant de la publication ou de l’utilisation de cette Publication de l’IEC ou de toute autre Publication de l’IEC,

ou au crédit qui lui est accordé.

8) L’attention est attirée sur les références normatives citées dans cette publication. L’utilisation de publications

référencées est obligatoire pour une application correcte de la présente publication.

9) L’IEC attire l’attention sur le fait que la mise en application du présent document peut entraîner l’utilisation d’un

ou de plusieurs brevets. L’IEC ne prend pas position quant à la preuve, à la validité et à l’applicabilité de tout

droit de brevet revendiqué à cet égard. À la date de publication du présent document, l’IEC n’avait pas reçu

notification qu’un ou plusieurs brevets pouvaient être nécessaires à sa mise en application. Toutefois, il y a lieu

d’avertir les responsables de la mise en application du présent document que des informations plus récentes

sont susceptibles de figurer dans la base de données de brevets, disponible à l’adresse https://patents.iec.ch.

L’IEC ne saurait être tenue pour responsable de ne pas avoir identifié de tels droits de brevet.

L’IEC 63378-6 a été établie par le sous-comité 47D: Boîtiers des dispositifs semiconducteurs,

du comité d’études 47 de l’IEC: Dispositifs à semiconducteurs. Il s’agit d’une Norme

internationale.

Le texte de cette Norme internationale est issu des documents suivants:

Projet Rapport de vote

47D/991/CDV 47D/998/RVC

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à son approbation.

La langue employée pour l’élaboration de cette Norme internationale est l’anglais.

Ce document a été rédigé selon les Directives ISO/IEC, Partie 2, il a été développé selon les

Directives ISO/IEC, Partie 1 et les Directives ISO/IEC, Supplément IEC, disponibles sous

www.iec.ch/members_experts/refdocs. Les principaux types de documents développés par

l’IEC sont décrits plus en détail sous www.iec.ch/publications.

Une liste de toutes les parties de la série IEC 63378, publiées sous le titre général

Normalisation thermique des boîtiers de semiconducteurs, se trouve sur le site web de l’IEC.

Le comité a décidé que le contenu de ce document ne sera pas modifié avant la date de stabilité

indiquée sur le site web de l’IEC sous webstore.iec.ch dans les données relatives au document

recherché. À cette date, le document sera

– reconduit,

– supprimé, ou

– révisé.

INTRODUCTION

La série IEC 63378-6 est composée des parties suivantes:

1,2

– L'IEC 63378-6-1 [1] définit la méthode de création de modèle utilisant une fiche technique

de dispositifs à semiconducteurs.

– L'IEC 63378-6-2 définit la méthode de création de modèle utilisant des données de mesure

des dispositifs à semiconducteurs.

La série IEC 63378-6 inclut des sujets tels que la définition d’un nouveau modèle thermique

compact pour l’analyse des transitoires thermiques des boîtiers de semiconducteurs, les

méthodes de création de modèles, l’évaluation de la précision de ces modèles, etc.

___________

Les chiffres entre crochets renvoient à la Bibliographie.

En cours d’élaboration. Stade au moment de la publication: IEC APUB 63378-6-1:2026.

En cours d’élaboration.

1 Domaine d’application

La présente partie de l’IEC 63378 spécifie un modèle de résistance thermique et de capacité

pour les boîtiers de semiconducteurs. Ce modèle est appelé transformation numérique utilisant

le modèle de résistance et de capacité thermiques (DXRC, Digital transformation using thermal

resistance and capacitance). Il prédit la température transitoire aux points de jonction et de

mesure.

Le présent document s’applique aux boîtiers de semiconducteurs tels que TO-252, TO-263 et

HSOP. Il prend en charge les boîtiers monopuces dissipant la chaleur d’une seule surface du

boîtier.

2 Références normatives

Le présent document ne contient aucune référence normative.

3 Termes et définitions

Pour les besoins du présent document, les termes et définitions suivants s’appliquent.

L’ISO et l’IEC tiennent à jour des bases de données terminologiques destinées à être utilisées

en normalisation, consultables aux adresses suivantes:

– IEC Electropedia: disponible à l’adresse https://www.electropedia.org/

– ISO Online browsing platform: disponible à l’adresse https://www.iso.org/obp

3.1

résistance thermique (d'un dispositif à semiconducteurs)

quotient de la différence entre la température virtuelle du dispositif et la température d’un point

de référence extérieur spécifié, par la puissance dissipée, en régime permanent, par le

dispositif

[SOURCE: IEC 60050-521:2002 [3], 521-05-13]

3.2

capacité thermique

capacité d’un matériau à stocker de l’énergie thermique, calculée par produit de la chaleur et

de la densité spécifiques

3.3

résistance thermique entre la jonction et le dessus du boîtier

θ

JC

résistance thermique entre une jonction et la surface d’un boîtier de semiconducteurs

3.4

topologie RC thermique

réseau thermique constitué de plusieurs résistances, capacités et nœuds thermiques

4 Définition de DXRC

4.1 Généralités

Les modèles thermiques compacts (CTM, Compact thermal models) sont couramment utilisés

pour l’analyse de la dynamique des fluides par ordinateur (CFD, Computer fluid dynamics) dans

les industries des semiconducteurs et de l’électronique. L’utilisation de CTM réduit le temps de

calcul et l’utilisation de la mémoire. Cependant, il existe peu de méthodes pour les CTM qui

peuvent prendre en charge l’analyse transitoire et l’estimation des points de mesure. Le DXRC

est une méthode de création de CTM qui prend en charge la prédiction de la température à une

jonction et à des points de mesure arbitraires.

4.2 Topologie de résistance et de capacité (RC) thermique de DXRC

4.2.1 Topologie RC thermique de DXRC

La topologie RC thermique du DXRC doit être définie comme à la Figure 1. Elle dispose de

deux zones de circuit RC appelées Zone adjacente à la jonction – RC (NJA-RC) et Zone des

points de mesure – RC (MPA-RC). NJA-RC contient un nœud de jonction nommé T et d’autres

J

nœuds reliant celui-ci nommé de T à T . Ces nœuds sont complètement internes, ils n’ont

1 N

donc pas de surfaces échangeant de la chaleur avec l’environnement extérieur. Chaque nœud

possède une capacité thermique et est connecté à un nœud voisin. Seul T génère de la chaleur.

J

Le nœud d’extrémité de NJA-RC est connecté au nœud supérieur de MPA-RC nommé T

CORE

par l’intermédiaire d’une résistance thermique. MPA-RC contient trois nœuds nommés T , T

C L

et T qui décrivent des points de mesure et cinq nœuds nommés T , T , T , T et T qui

S BI BO LB SB TOP

se connectent à des modèles 3D externes par l’intermédiaire de surfaces CTM. Cette topologie

est définie en fonction des trajets de flux de chaleur entre la jonction et la surface du boîtier.

Noter que cette topologie RC thermique ne contient que la propriété thermique à l’intérieur d’un

boîtier; en d’autres termes, la propriété thermique de la carte à circuit imprimé et d’autres

environnements n’est pas incluse.

Légende

T nœud thermique représentant la jonction dans une topologie RC thermique

J

T nœud thermique interne en tant que point de branchement, ne représentant aucun emplacement réel

CŒUR

T nœuds thermiques internes entre T et T , ne représentant aucun emplacement réel, un nombre naturel

N J CŒUR

commençant par celui le plus proche de T pour N

J

T nœud thermique représentant une position arbitraire sur la surface supérieure du boîtier, avec une surface

TOP

basée sur la surface supérieure du boîtier, qui échange de la chaleur avec l’environnement

T nœud thermique interne représentant une position arbitraire sur la surface métallisée inférieure du boîtier

C

T nœud dont la surface est basée sur la surface métallique située directement sous la puce, qui échange de

BI

la chaleur avec l’environnement

T nœud thermique dont la surface est basée sur la surface en résine inférieure du boîtier, qui échange de la

BO

chaleur avec l’environnement

T nœud thermique interne représentant une position arbitraire sur les bornes de sortie

L

T nœud thermique dont les surfaces sont basées sur la surface inférieure des bornes de sortie, qui échangent

LB

de la chaleur avec l’environnement

T nœud thermique interne représentant une position arbitraire sur un dissipateur thermique métallique du

S

boîtier

T nœud thermique dont la surface est basée sur la surface inférieure d’une partie d’un dissipateur thermique

SB

métallique, qui échange de la chaleur avec l’environnement

Figure 1 – Topologie RC thermique de DXRC

4.2.2 Contours de DXRC

DXRC a comme nœuds de surface T , T , T , T et T . Il convient que ces surfaces

BI BO LB SB TOP

soient définies conformément aux contours des boîtiers de semiconducteurs. Un exemple est

représenté à la Figure 2.

Figure 2 – Contours de DXRC

4.2.3 Valeurs RC sur NJA-RC

Les valeurs RC contenues dans NJA-RC doivent être calculées par une méthode commune [1].

La mesure, la simulation, la fiche technique des boîtiers de semiconducteurs et toute autre

donnée de température croissante de la jonction peuvent être utilisées comme données

d’entrée. Il convient que la plage de résistance thermique entre T et T soit inférieure à celle

J N

entre T et T afin d’ajouter MPA-RC ultérieurement.

J C

4.2.4 Valeurs RC sur la MPA-RC

Les valeurs RC sur la MPA-RC doivent être optimisées pour réduire le plus possible l’erreur

définie par les Équations (1) et (2). D’autres méthodes, telles que l’ajustement de courbe,

peuvent être utilisées si une optimisation équivalente est possible. En outre, n’importe quel

algorithme d’optimisation peut être utilisé. Les données d’entrée sont des échauffements au

niveau d’une jonction et au moins un point de mesure. Ces données de température sont les

mêmes que les données d’entrée du paragraphe 4.2.3.

T (tT) − (t)

input DXRC

eT_ t ×100

( )

(1)

J

Tt( )

input

eT_ (t) T (t)− T (t)

(2)

M input DXRC

où

e_T (t) et e_T (t) sont des erreurs à l’instant t entre les données d'entrée et le

J M

résultat de DXRC respectivement pour T et les points de

J

mesure;

T (t) est la température des données d’entrée;

input

T (t) est la température estimée par DXRC;

DXRC

e

t dans la puissance m- de 10 est calculée par l’Équation (3).

=

=

1,5

n

mm+1 m

(3)

tn=10+ 10 −×10 (=1, 2,,1 0)

( )

où

m est le nombre entier.

Les deux données peuvent être calculées à l’aide d’une interpolation linéaire ou d’autres

méthodes si les temps des données ne correspondent pas aux temps définis à l’Équation (3).

Comme l’erreur dépend des environnements tels que les cartes à circuit imprimé, il convient de

préparer les données d’entrée en fonction de celles-ci. Voir l’Annexe A à l’Annexe D pour plus

de précisions.

Annexe A

(informative)

Vérification de la précision du modèle DXRC pour TO-252

A.1 Généralités

Le résultat de la vérification de précision d’un modèle DXRC est présenté dans la présente

Annexe A. Les données d’entrée ont été obtenues par le calcul d’un modèle de boîtier de

semiconducteurs représenté à la Figure A.1, laquelle a été reproduite en détail.

A.2 Modèle CFD

Le modèle CFD représenté à la Figure A.1 a été utilisé. Un boîtier de semiconducteurs (TO-252)

représenté à la Figure A.2 est monté sur une carte à circuit imprimé située sur une plaque froide

par l’intermédiaire d’un matériau d’interface thermique (TIM). Le modèle de boîtier se compose

de la puce, de la fixation de la puce, du dissipateur, des bornes de sortie et du moule. La carte

à circuit imprimé est constituée de cuivre et de couches diélectriques, et de trous de liaison.

L’air occupait les autres régions du domaine de solution. Leurs spécifications de matière sont

indiquées dans le Tableau A.1. Le T situé sur le dissipateur apparent a été utilisé comme point

S

de mesure. La puissance, 1 W, a été appliquée comme une fonction échelonnée

...

IEC 63378-6 ®

Edition 1.0 2026-02

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Thermal standardization on semiconductor packages -

Part 6: Thermal resistance and capacitance model for transient temperature

prediction at junction and measurement points

Normalisation thermique des boîtiers de semiconducteurs -

Partie 6: Modèle de résistance thermique et de capacité pour la prédiction de la

température transitoire aux points de jonction et de mesure

ICS 31.080.01 ISBN 978-2-8327-1001-2

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or

by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either

IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright

or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local

IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et

les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - IEC Products & Services Portal - products.iec.ch

webstore.iec.ch/advsearchform Discover our powerful search engine and read freely all the

The advanced search enables to find IEC publications by a publications previews, graphical symbols and the glossary.

variety of criteria (reference number, text, technical With a subscription you will always have access to up to date

committee, …). It also gives information on projects, content tailored to your needs.

replaced and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published containing more than 22 500 terminological entries in English

details all new publications released. Available online and and French, with equivalent terms in 25 additional languages.

once a month by email. Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer

Service Centre: sales@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Recherche de publications IEC - IEC Products & Services Portal - products.iec.ch

webstore.iec.ch/advsearchform Découvrez notre puissant moteur de recherche et consultez

La recherche avancée permet de trouver des publications gratuitement tous les aperçus des publications, symboles

IEC en utilisant différents critères (numéro de référence, graphiques et le glossaire. Avec un abonnement, vous aurez

texte, comité d’études, …). Elle donne aussi des toujours accès à un contenu à jour adapté à vos besoins.

informations sur les projets et les publications remplacées

ou retirées. Electropedia - www.electropedia.org

Le premier dictionnaire d'électrotechnologie en ligne au

IEC Just Published - webstore.iec.ch/justpublished monde, avec plus de 22 500 articles terminologiques en

Restez informé sur les nouvelles publications IEC. Just anglais et en français, ainsi que les termes équivalents

Published détaille les nouvelles publications parues. dans 25 langues additionnelles. Egalement appelé

Disponible en ligne et une fois par mois par email. Vocabulaire Electrotechnique International (IEV) en ligne.

Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette

publication ou si vous avez des questions contactez-

nous: sales@iec.ch.

CONTENTS

FOREWORD . 3

INTRODUCTION . 5

1 Scope . 6

2 Normative references . 6

3 Terms and definitions . 6

4 Definition of DXRC. 6

4.1 General . 6

4.2 Thermal resistance and capacitance (RC) topology of DXRC . 7

4.2.1 Thermal RC topology of DXRC . 7

4.2.2 Outline of DXRC . 8

4.2.3 RC values on NJA-RC . 8

4.2.4 RC values on MPA-RC . 8

Annex A (informative) Accuracy verification of DXRC model for TO-252 . 10

A.1 General . 10

A.2 CFD model. 10

A.3 Calculation of thermal RC values. 12

A.4 MPA-RC and DXRC model outline . 13

A.5 Optimization of RC values in MPA-RC . 13

A.6 Result. 15

Annex B (informative) Accuracy verification of DXRC model for TO-263 . 16

B.1 General . 16

B.2 CFD model. 16

B.3 Calculation of thermal RC values. 18

B.4 MPA-RC and DXRC model outline . 19

B.5 Optimization of RC values in MPA-RC . 19

B.6 Result. 20

Annex C (informative) Accuracy verification of DXRC model for HSOP . 21

C.1 General . 21

C.2 CFD model. 21

C.3 Calculation of thermal RC values. 23

C.4 MPA-RC and DXRC model outline . 24

C.5 Optimization of RC values in MPA-RC . 24

C.6 Result. 25

Annex D (informative) The effect of PCB layers . 26

D.1 General . 26

D.2 Verification method . 26

D.3 Result. 26

Bibliography . 28

Figure 1 – Thermal RC topology of DXRC . 7

Figure 2 – Outline of DXRC . 8

Figure A.1 – CFD model for TO-252 . 10

Figure A.2 – Size of TO-252 package . 11

Figure A.3 – Structure function . 12

Figure A.4 – Result of verification . 15

Figure B.1 – CFD model for TO-263 . 16

Figure B.2 – Size of TO-263 package . 17

Figure B.3 – Structure function . 18

Figure B.4 – Result of verification . 20

Figure C.1 – CFD model for HSOP . 21

Figure C.2 – Size of HSOP package . 22

Figure C.3 – Structure function . 23

Figure C.4 – Result of verification . 25

Figure D.1 – Comparisons of temperature rise between the detailed model and the

DXRC model . 27

Table A.1 – Material attributes . 11

Table A.2 – Thermal resistances in NJA-RC . 12

Table A.3 – Thermal capacitances in NJA-RC . 13

Table A.4 – Input variables . 14

Table A.5 – Optimized RC values . 14

Table B.1 – Material attributes . 17

Table B.2 – Thermal resistances in NJA-RC . 18

Table B.3 – Thermal capacitances in NJA-RC . 19

Table B.4 – Optimized RC values . 20

Table C.1 – Material Attributes . 22

Table C.2 – Thermal resistances in NJA-RC . 23

Table C.3 – Thermal capacitances in NJA-RC . 24

Table C.4 – Optimized RC values . 25

Table D.1 – Combination of the coverages of copper layers . 26

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

Thermal standardization on semiconductor packages -

Part 6: Thermal resistance and capacitance model for transient

temperature prediction at junction and measurement points

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC Publication(s)”). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for

Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence between

any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) IEC draws attention to the possibility that the implementation of this document may involve the use of (a)

patent(s). IEC takes no position concerning the evidence, validity or applicability of any claimed patent rights in

respect thereof. As of the date of publication of this document, IEC had not received notice of (a) patent(s), which

may be required to implement this document. However, implementers are cautioned that this may not represent

the latest information, which may be obtained from the patent database available at https://patents.iec.ch. IEC

shall not be held responsible for identifying any or all such patent rights.

IEC 63378-6 has been prepared by subcommittee 47D: Semiconductor devices packaging, of

IEC Technical Committee 47: Semiconductor devices. It is an International Standard.

The text of this International Standard is based on the following documents:

Draft Report on voting

47D/991/CDV 47D/998/RVC

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in

accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available

at www.iec.ch/members_experts/refdocs. The main document types developed by IEC are

described in greater detail at www.iec.ch/publications.

A list of all parts in the IEC 63378 series, published under the general title Thermal

standardization on semiconductor packages, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the

stability date indicated on the IEC website under webstore.iec.ch in the data related to the

specific document. At this date, the document will be

– reconfirmed,

– withdrawn, or

– revised.

INTRODUCTION

The IEC 63378-6 series is composed of the following parts:

1,2

– IEC 63378-6-1 [1] defines the model creation method using a datasheet of semiconductor

devices.

– IEC 63378-6-2 defines the model creation method using measurement data of

semiconductor devices.

The IEC 63378-6 series includes subjects such as the definition of a new thermal compact

model for thermal transient analysis of semiconductor packages, model creation methods,

accuracy assessment of these models, etc.

___________

Numbers in square brackets refer to the Bibliography.

Under preparation. Stage at the time of publication: IEC APUB 63378-6-1:2026.

Under development.

1 Scope

This part of IEC 63378 specifies a thermal resistance and capacitance model for semiconductor

packages. This model is named the digital transformation using thermal resistance and

capacitance (DXRC) model. It predicts transient temperature at junction and measurement

points.

This document applies to semiconductor packages such as TO-252, TO-263, and HSOP. It

supports single chip packages dissipated heat from single package surface.

2 Normative references

There are no normative references in this document.

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminology databases for use in standardization at the following

addresses:

– IEC Electropedia: available at https://www.electropedia.org/

– ISO Online browsing platform: available at https://www.iso.org/obp

3.1

thermal resistance

quotient of the difference between the virtual temperature of the device and the temperature of

a stated external reference point, by the steady-state power dissipation in the device

[SOURCE: IEC 60050-521:2002 [3], 521-05-13]

3.2

thermal capacitance

ability of a material to store thermal energy, calculated by product of specific heat and density

3.3

thermal resistance from junction to case top

θ

JC

thermal resistance between a junction and a semiconductor package surface

3.4

thermal RC topology

thermal network consisting of several thermal resistances, capacitances, and nodes

4 Definition of DXRC

4.1 General

Compact thermal models (CTMs) are commonly used for computer fluid dynamics (CFD)

analysis in semiconductor and electronics industries. Using CTMs reduces calculation time and

memory usage. However, there are few methods for CTMs which can support transient analysis

and estimation of measurement points. DXRC is a method to create CTMs which supports

predicting the temperature at a junction and arbitrary measurement points.

4.2 Thermal resistance and capacitance (RC) topology of DXRC

4.2.1 Thermal RC topology of DXRC

Thermal RC topology of DXRC shall be defined as in Figure 1. It has two RC circuit areas

named Near Junction Area – RC (NJA-RC) and Measurement Points Area – RC (MPA-RC).

NJA-RC contains a junction node named T and other nodes linking from it named from T to

J 1

T . These nodes are completely inside nodes, thus they do not have any surfaces which

N

exchange heat with the external environment. Each node has one thermal capacitance and is

connected to a neighbouring node. Only T generates heat. The end node of NJA-RC is

J

via a thermal resistance. MPA-RC contains

connected to the top node of MPA-RC named T

CORE

three nodes named T , T and T which are describing measurement points and five nodes

C L S

named T , T , T , T and T which are connecting to external 3D models via CTM

BI BO LB SB TOP

surfaces. This topology is defined according to the heat flow paths from junction to package

surfaces. Note that this thermal RC topology contains only thermal property inside a package,

namely, the thermal property of PCB and other surrounding environments is not contained.

Key

T thermal node representing the junction in a thermal RC topology

J

T internal thermal node as a branch point, not representing any actual location

CORE

T internal thermal nodes between T and T , not representing any actual locations, a natural number

N J CORE

starting from the one closest to T for N

J

T thermal node representing an arbitrary position on the top surface of the package, with a surface based on

TOP

the top surface of the package, that exchanges heat with the surrounding environment

T internal thermal node representing at an arbitrary position on the bottom metal surface of the package

C

T thermal node with a surface based on the metal surface directly under the chip, which exchanges heat with

BI

the surrounding environment

T thermal node with a surface based on the bottom resin surface of the package, which exchanges heat with

BO

the surrounding environment

T internal thermal node representing an arbitrary position on the lead terminals

L

T thermal node with surfaces based on the bottom surface of the lead terminals, which exchange heat with

LB

the surrounding environment

T internal thermal node representing an arbitrary position on a metal heat spreader of the package

S

T thermal node with a surface based on the bottom surface of a part of a metal heat spreader, which

SB

exchanges heat with the surrounding environment

Figure 1 – Thermal RC topology of DXRC

4.2.2 Outline of DXRC

DXRC has T , T , T , T and T as surface nodes. These surfaces should be defined

BI BO LB SB TOP

according to outline of semiconductor packages. An example is shown in Figure 2.

Figure 2 – Outline of DXRC

4.2.3 RC values on NJA-RC

RC values contained in NJA-RC shall be calculated by a common method [1]. Measurement,

simulation, datasheet of semiconductor packages and any other rising temperature data of

junction may be used as input data. The thermal resistance range between T and T should

J N

be smaller than between T and T in order to add MPA-RC later.

J C

4.2.4 RC values on MPA-RC

RC values on MPA-RC shall be optimized to minimize the error defined by Equations (1) and

(2). Other methods such as curve fitting may be used if equivalent optimization is possible.

Additionally, any optimization algorithm may be used. The input data are temperature rises at

a junction and at least one measurement point. This temperature data is the same as input data

at 4.2.3.

T tT− t

() ()

input DXRC

eT_ t ×100

()

(1)

J

Tt

()

input

eT_ t T t− T t

() () ()

(2)

M input DXRC

where

e_T (t) and e_T (t) are errors at time t between the input data and the result of DXRC

J M

for T and measurement points respectively;

J

T (t) is the temperature of input data;

input

T (t) is the estimated temperature by DXRC;

DXRC

t in the m-th power of 10 is calculated by Equation (3).

=

=

1,5

n

mm+1 m

(3)

tn=10+ 10 −×10 (=1, 2,,1 0)

( )

where

m is the integer number.

Both data can be calculated using linear interpolation or other methods if the times of the data

do not correspond to the times defined in Equation (3). Since error is dependent on surrounding

environments such as PCBs, input data should be prepared according to them. For details,

please refer to Annex A to Annex D.

Annex A

(informative)

Accuracy verification of DXRC model for TO-252

A.1 General

The result of the accuracy verification of a DXRC model is shown in this Annex A. The input

data was obtained by the calculation of a semiconductor package model shown in Figure A.1,

which was reproduced in detail.

A.2 CFD model

The CFD model shown in Figure A.1 was used. A semiconductor package (TO-252) shown in

Figure A.2 was mounted on a printed circuit board (PCB) which was located on a cold plate via

a thermal interface material (TIM). The package model consists of the chip, die attach, spreader,

lead terminals, and mold. The PCB consists of copper and dielectric layers, and vias. Other

spaces in the solution domain were occupied by air. Their material specifications are shown in

Table A.1. The T located on the exposed spreader was used as a measurement point. The

S

power, 1 W, was applied as a step function on the top surface of the chip. The bottom surface

of the cold plate was fixed at 0 °C. Only thermal conduction was solved. The transient time

period was 100 s and each time step was defined based on Equation (3). The package model

was replaced with the DXRC model when the result of the DXRC model was calculated.

Figure A.1 – CFD model for TO-252

Dimensions in millimetres

Figure A.2 – Size of TO-252 package

Table A.1 – Material attributes

Materials Thermal conductivity Density Specific heat

(W/m∙K) (J/kg∙K)

(kg/m )

Chip -0,42T+159 (where T is Temperature) 2 330 823

Die attach 20 10 000 200

Spreader 302 8 900 380

Lead terminal 301 8 900 385

Mold 0,649 1 840 900

Layer 447 8 930 471

Insulator 1,061 6 (in plane) / 0,524 2 (axial) 1 980 686

Via plate 447 8 930 471

Via fill 42,7 7 400 600

TIM 4,23 2 330 675

Cold plate 391 8 890 385

Air 0,026 1 1,16 1 005

A.3 Calculation of thermal RC values

The structure function obtained from the detailed semiconductor package CFD model is shown

in Figure A.3. It was calculated according to a common method [1]. At the same time, the

thermal resistance from junction to case top, θ is calculated as 1,22 K/W. In this case, the

JC

thermal resistance range of NJA-RC was determined as 0,97 K/W. It is 0,8 times θ . The

JC

thermal RC values in NJA-RC were obtained as shown Table A.2 and Table A.3.

Figure A.3 – Structure function

Table A.2 – Thermal resistances in NJA-RC

Node Thermal resistance Node Thermal Node Thermal resistance

resistance

(K/W) (K/W) (K/W)

-3 -3 -2

T -T T -T T -T

3,71 × 10 7,99 × 10 1,71 × 10

J 1 1 2 2 3

-2 -2 -2

T -T T -T T -T

2,87 × 10 3,64 × 10 3,59 × 10

3 4 4 5 5 6

-2 -2 -2

T -T T -T T -T

2,94 × 10 2,17 × 10 1,54 × 10

6 7 7 8 8 9

-2 -3 -3

T -T T -T T -T

1,12 × 10 8,63 × 10 7,40 × 10

9 10 10 11 11 12

-3 -3 -3

T -T T -T T -T

7,18 × 10 7,96 × 10 9,92 × 10

12 13 13 14 14 15

-2 -2 -2

T -T T -T T -T

1,34 × 10 1,90 × 10 2,69 × 10

15 16 16 17 17 18

-2 -2 -2

T -T T -T T -T

3,64 × 10 4,56 × 10 5,14 × 10

18 19 19 20 20 21

-2 -2 -2

T -T T -T T -T

5,22 × 10 4,90 × 10 4,44 × 10

21 22 22 23 23 24

-2 -2 -2

T -T T -T T -T

4,08 × 10 3,92 × 10 3,94 × 10

24 25 25 26 26 27

Node Thermal resistance Node Thermal Node Thermal resistance

resistance

(K/W) (K/W) (K/W)

-2 -2 -2

T -T T -T T -T

3,96 × 10 3,70 × 10 3,08 × 10

27 28 28 29 29 30

-2 -2 -2

T -T T -T T -T

2,28 × 10 1,61 × 10 1,23 × 10

30 31 31 32 32 33

-2 -2 -2

T -T T -T T -T

1,13 × 10 1,28 × 10 1,61 × 10

33 34 34 35 35 36

-2 -2 -2

T -T T -T T -T

2,02 × 10 2,52 × 10 1,95 × 10

36 37 37 38 38 CORE

Table A.3 – Thermal capacitances in NJA-RC

Node Thermal capacitance Node Thermal capacitance Node Thermal capacitance

(J/K) (J/K) (J/K)

-5 -5 -5

T T T

9,52 × 10 8,73 × 10 3,91 × 10

J 1 2

-5 -5 -5

T T T

2,05 × 10 1,43 × 10 1,33 × 10

3 4 5

-5 -5 -5

T T T

1,55 × 10 2,12 × 10 3,10 × 10

6 7 8

-5 -5 -5

T T T

4,59 × 10 6,53 × 10 8,56 × 10

9 10 11

-4 -4 -5

T T T

1,00 × 10 1,04 × 10 9,54 × 10

12 13 14

-5 -5 -5

T T T

7,94 × 10 6,21 × 10 4,76 × 10

15 16 17

-5 -5 -5

T T T

3,73 × 10 3,12 × 10 2,88 × 10

18 19 20

-5 -5 -5

T T T

2,96 × 10 3,36 × 10 4,05 × 10

21 22 23

-5 -5 -5

T T T

4,94 × 10 5,83 × 10 6,55 × 10

24 25 26

-5 -5 -4

T T T

7,18 × 10 8,18 × 10 1,03 × 10

27 28 29

-4 -4 -4

T T T

1,48 × 10 2,31 × 10 3,54 × 10

30 31 32

-4 -4 -4

T T T

4,73 × 10 5,15 × 10 4,76 × 10

33 34 35

-4 -4 -4

T T T

4,19 × 10 3,76 × 10 1,90 × 10

36 37 38

A.4 MPA-RC and DXRC model outline

Nodes belonging to the MPA-RC were connected to the NJA-RC according to Figure 1. In this

case, T and T were omitted. Since RC values in MPA-RC would be optimized, they were

C L

specified tentative values such as 1. The outline of the DXRC model was defined the same as

that of Figure 2.

A.5 Optimization of RC values in MPA-RC

The RC values in MPA-RC were obtained by optimization. Input variables of optimization are

shown in Table A.4. Curve fitting between the input data and the DXRC was used as an

objective function. Two types of optimization algorithms, genetic algorithm (GA) and software-

specific algorithm (SSA) were used to investigate the dependence of algorithm. Optimized input

variables are shown in Table A.5. As can be seen, the optimized values using GA and SSA are

different. This results from the fact that each value does not have a physical meaning and the

solution is not unique. Moreover, this is also because this type of optimization is a multi-

objective optimization. Therefore, it is important that a solution with high accuracy exists and

that at least one of them is found rather than each value itself.

Table A.4 – Input variables

Name Type Minimum Maximum Resolution

-2 2 4

T -T

Resistance (W/K) 1,0 × 10 1,0 × 10 1,0 × 10

CORE BI

-2 2 4

T -T

Resistance (W/K) 1,0 × 10 1,0 × 10 1,0 × 10