IEC 60749-26:2013

(Main)Semiconductor devices - Mechanical and climatic test methods - Part 26: Electrostatic discharge (ESD) sensitivity testing - Human body model (HBM)

Semiconductor devices - Mechanical and climatic test methods - Part 26: Electrostatic discharge (ESD) sensitivity testing - Human body model (HBM)

IEC 60749-26:2013 establishes the procedure for testing, evaluating, and classifying components and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined human body model (HBM) electrostatic discharge (ESD). The purpose (objective) of this standard is to establish a test method that will replicate HBM failures and provide reliable, repeatable HBM ESD test results from tester to tester, regardless of component type. Repeatable data will allow accurate classifications and comparisons of HBM ESD sensitivity levels. ESD testing of semiconductor devices is selected from this test method, the machine model (MM) test method (see IEC 60749-27) or other ESD test methods in the IEC 60749 series. The HBM and MM test methods produce similar but not identical results; unless otherwise specified, this test method is the one selected. This edition includes the following significant technical changes with respect to the previous edition:

a) descriptions of oscilloscope and current transducers have been refined and updated;

b) the HBM circuit schematic and description have been improved;

c) the description of stress test equipment qualification and verification has been completely re-written;

d) qualification and verification of test fixture boards has been revised;

e) a new section on the determination of ringing in the current waveform has been added;

f) some alternate pin combinations have been included;

g) allowance for non-supply pins to stress to a limited number of supply pin groups (associated non-supply pins) and allowance for non-supply to non-supply (i.e., I/O to I/O) stress to be limited to a finite number of 2 pin pairs (coupled non-supply pin pairs);

h) explicit allowance for HBM stress using 2 pin HBM testers for die only shorted supply groups.

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques - Partie 26: Essai de sensibilité aux décharges électrostatiques (DES) - Modèle du corps humain (HBM)

La CEI 60749-26:2013 établit une procédure pour les essais, l'évaluation et la classification des composants et des microcircuits en fonction de leur susceptibilité (sensibilité) aux dommages ou de leur dégradation suite à leur exposition à des décharges électrostatiques (DES) sur un modèle de corps humain (HBM) défini. Le but (objectif) de cette norme est de déterminer une méthode d'essai permettant de reproduire les défaillances du HBM et de fournir des résultats d'essais de DES de HBM fiables et reproductibles d'un appareil d'essai à un autre, sans tenir compte du type de composant. Des données reproductibles autoriseront des classifications et des comparaisons précises des niveaux de sensibilité de DES de HBM. Les essais de DES des dispositifs à semiconducteurs sont choisis entre la présente méthode d'essai, celle du modèle de machine (MM) (voir CEI 60749-27) ou toute autre méthode d'essai de la série CEI 60749. Les méthodes d'essai HBM et MM produisent des résultats similaires mais non identiques; sauf indication contraire, la présente méthode d'essai est celle qui prévaut. Cette édition inclut les modifications techniques majeures suivantes par rapport à l'édition précédente:

a) les descriptions de l'oscilloscope et des transducteurs de courant ont été améliorées et mises à jour;

b) le schéma de circuit et la description du HBM ont été améliorés;

c) la description de la qualification et de la vérification du matériel d'essai de contrainte a été entièrement réécrite;

d) la qualification et la vérification des cartes de montage d'essai ont été révisées;

e) une nouvelle section concernant la détermination de l'oscillation de la forme d'onde de courant a été ajoutée;

f) certaines variantes de combinaisons de broches ont été incluses;

g) autorisation de contrainte pour les broches n'assurant pas l'alimentation jusqu'à un nombre limité de groupes de broches d'alimentation (broches associées n'assurant pas l'alimentation) et autorisation de limiter les contraintes entre broches n'assurant pas l'alimentation et broches n'assurant pas l'alimentation (c'est-à-dire, E/S vers E/S) à un nombre fini de 2 paires de broches (paires de broches couplées n'assurant pas l'alimentation);

- h) autorisation explicite de contrainte de HBM utilisant des appareils d'essai de HBM à 2 broches pour puce seulement pour des groupes d'alimentations court-circuitées.

General Information

- Status

- Published

- Publication Date

- 22-Apr-2013

- Technical Committee

- TC 47 - Semiconductor devices

- Drafting Committee

- WG 2 - TC 47/WG 2

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 15-Jan-2018

- Completion Date

- 31-Jan-2017

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 60749-26:2013 is an essential international standard developed by the International Electrotechnical Commission (IEC) for evaluating the Electrostatic Discharge (ESD) sensitivity of semiconductor devices using the Human Body Model (HBM). This standard specifies repeatable test methods to simulate real-world ESD events and classifies semiconductor components and microcircuits based on their susceptibility to ESD-induced failure or degradation.

By establishing precise procedures, IEC 60749-26 ensures reliable and consistent ESD sensitivity test results across different labs and test equipment, enabling effective product qualification, component comparison, and robust ESD protection in electronic design and manufacturing.

Key Topics

- Human Body Model (HBM) Test Method: Provides a defined method to replicate the ESD failures typically caused by human contact, ensuring authenticity in testing semiconductor devices’ resilience.

- Test Procedure and Classification: Outlines steps for applying HBM ESD stress to components, capturing waveform data, and evaluating device response to assign ESD sensitivity levels.

- Apparatus and Equipment Requirements: Specifies minimum requirements for oscilloscopes, current probes, evaluation loads, and ESD simulators to verify accuracy and repeatability of test results.

- Equipment Qualification and Verification: Requires periodic qualification and verification of test equipment and fixture boards to maintain reliability and compliance.

- Pin Categorization and Grouping: Defines classification of device pins (such as supply, non-supply, and shorted pins) and appropriate stress test combinations for comprehensive device assessment.

- Safety Measures: Details safety protocols for personnel and process setup during ESD testing.

Applications

IEC 60749-26 is widely used in the design, manufacturing, and quality assurance of semiconductor devices to ensure immunity to common ESD threats. It plays a critical role in:

- Device Qualification and Reliability Assessment: Manufacturers use this standard to classify the ESD sensitivity of integrated circuits, transistors, diodes, microchips, and hybrid circuits before market release.

- Supply Chain Quality Control: Buyers and OEMs rely on HBM ESD classification levels for supplier qualification and to meet contractual ESD protection requirements.

- Failure Analysis and Comparison: Engineering teams utilize the standard to analyze failed components, benchmark ESD robustness, and select suitable device candidates for sensitive applications.

- Compliance Testing: Regulatory and certification bodies reference IEC 60749-26 to validate compliance with international ESD protection standards.

- Process Improvement: Test results derived from following IEC 60749-26 procedures drive improvements in device layout, packaging, and process controls to enhance overall ESD immunity.

Related Standards

For a comprehensive ESD robustness program and further guidance, consider the following related standards:

- IEC 60749 Series: The parent series for mechanical and climatic test methods of semiconductor devices, encompassing other ESD test approaches.

- IEC 60749-27: Specifies the Machine Model (MM) ESD test method. The MM method provides supplementary but not identical insights compared to HBM testing.

- ANSI/ESDA/JEDEC JS-001: The US joint standard for HBM ESD testing, harmonized with IEC 60749-26 for global compatibility.

- JEDEC JESD22-A114: Earlier JEDEC standard for HBM ESD testing, incorporated into later harmonized standards.

Practical Value

Implementing IEC 60749-26:2013 helps companies minimize ESD-related failures, improve device reliability, and meet international market expectations for semiconductor ESD robustness. The widespread adoption of this standard ensures that products are tested under proven, consistent conditions, safeguarding electronic systems across industries-from consumer devices to automotive and industrial applications. By adhering to IEC 60749-26, organizations enhance their competitiveness, reduce warranty claims, and maintain product integrity in ESD-prone environments.

Keywords: IEC 60749-26, semiconductor ESD sensitivity, human body model, ESD test method, HBM testing, electrostatic discharge, device classification, electronic component reliability, standardization, IEC standards.

Buy Documents

IEC 60749-26:2013 - Semiconductor devices - Mechanical and climatic test methods - Part 26: Electrostatic discharge (ESD) sensitivity testing - Human body model (HBM) Released:4/23/2013

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

NYCE

Mexican standards and certification body.

ANCE

Mexican certification and testing association.

Sponsored listings

Frequently Asked Questions

IEC 60749-26:2013 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Mechanical and climatic test methods - Part 26: Electrostatic discharge (ESD) sensitivity testing - Human body model (HBM)". This standard covers: IEC 60749-26:2013 establishes the procedure for testing, evaluating, and classifying components and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined human body model (HBM) electrostatic discharge (ESD). The purpose (objective) of this standard is to establish a test method that will replicate HBM failures and provide reliable, repeatable HBM ESD test results from tester to tester, regardless of component type. Repeatable data will allow accurate classifications and comparisons of HBM ESD sensitivity levels. ESD testing of semiconductor devices is selected from this test method, the machine model (MM) test method (see IEC 60749-27) or other ESD test methods in the IEC 60749 series. The HBM and MM test methods produce similar but not identical results; unless otherwise specified, this test method is the one selected. This edition includes the following significant technical changes with respect to the previous edition: a) descriptions of oscilloscope and current transducers have been refined and updated; b) the HBM circuit schematic and description have been improved; c) the description of stress test equipment qualification and verification has been completely re-written; d) qualification and verification of test fixture boards has been revised; e) a new section on the determination of ringing in the current waveform has been added; f) some alternate pin combinations have been included; g) allowance for non-supply pins to stress to a limited number of supply pin groups (associated non-supply pins) and allowance for non-supply to non-supply (i.e., I/O to I/O) stress to be limited to a finite number of 2 pin pairs (coupled non-supply pin pairs); h) explicit allowance for HBM stress using 2 pin HBM testers for die only shorted supply groups.

IEC 60749-26:2013 establishes the procedure for testing, evaluating, and classifying components and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined human body model (HBM) electrostatic discharge (ESD). The purpose (objective) of this standard is to establish a test method that will replicate HBM failures and provide reliable, repeatable HBM ESD test results from tester to tester, regardless of component type. Repeatable data will allow accurate classifications and comparisons of HBM ESD sensitivity levels. ESD testing of semiconductor devices is selected from this test method, the machine model (MM) test method (see IEC 60749-27) or other ESD test methods in the IEC 60749 series. The HBM and MM test methods produce similar but not identical results; unless otherwise specified, this test method is the one selected. This edition includes the following significant technical changes with respect to the previous edition: a) descriptions of oscilloscope and current transducers have been refined and updated; b) the HBM circuit schematic and description have been improved; c) the description of stress test equipment qualification and verification has been completely re-written; d) qualification and verification of test fixture boards has been revised; e) a new section on the determination of ringing in the current waveform has been added; f) some alternate pin combinations have been included; g) allowance for non-supply pins to stress to a limited number of supply pin groups (associated non-supply pins) and allowance for non-supply to non-supply (i.e., I/O to I/O) stress to be limited to a finite number of 2 pin pairs (coupled non-supply pin pairs); h) explicit allowance for HBM stress using 2 pin HBM testers for die only shorted supply groups.

IEC 60749-26:2013 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general; 33.200 - Telecontrol. Telemetering; 35.100 - Open systems interconnection (OSI). The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60749-26:2013 has the following relationships with other standards: It is inter standard links to IEC 60749-26:2006, IEC 60749-26:2018. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60749-26:2013 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 60749-26 ®

Edition 3.0 2013-04

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 26: Electrostatic discharge (ESD) sensitivity testing – Human body model

(HBM)

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 26: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle du

corps humain (HBM)

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les

microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

Useful links:

IEC publications search - www.iec.ch/searchpub Electropedia - www.electropedia.org

The advanced search enables you to find IEC publications The world's leading online dictionary of electronic and

by a variety of criteria (reference number, text, technical electrical terms containing more than 30 000 terms and

committee,…). definitions in English and French, with equivalent terms in

It also gives information on projects, replaced and additional languages. Also known as the International

withdrawn publications. Electrotechnical Vocabulary (IEV) on-line.

IEC Just Published - webstore.iec.ch/justpublished Customer Service Centre - webstore.iec.ch/csc

Stay up to date on all new IEC publications. Just Published If you wish to give us your feedback on this publication

details all new publications released. Available on-line and or need further assistance, please contact the

also once a month by email. Customer Service Centre: csc@iec.ch.

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

Liens utiles:

Recherche de publications CEI - www.iec.ch/searchpub Electropedia - www.electropedia.org

La recherche avancée vous permet de trouver des Le premier dictionnaire en ligne au monde de termes

publications CEI en utilisant différents critères (numéro de électroniques et électriques. Il contient plus de 30 000

référence, texte, comité d’études,…). termes et définitions en anglais et en français, ainsi que

Elle donne aussi des informations sur les projets et les les termes équivalents dans les langues additionnelles.

publications remplacées ou retirées. Egalement appelé Vocabulaire Electrotechnique

International (VEI) en ligne.

Just Published CEI - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications de la CEI.

Just Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur

Disponible en ligne et aussi une fois par mois par email. cette publication ou si vous avez des questions

contactez-nous: csc@iec.ch.

IEC 60749-26 ®

Edition 3.0 2013-04

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 26: Electrostatic discharge (ESD) sensitivity testing – Human body model

(HBM)

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 26: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle du

corps humain (HBM)

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

PRICE CODE

INTERNATIONALE

CODE PRIX X

ICS 31.080.01 ISBN 978-2-83220-746-8

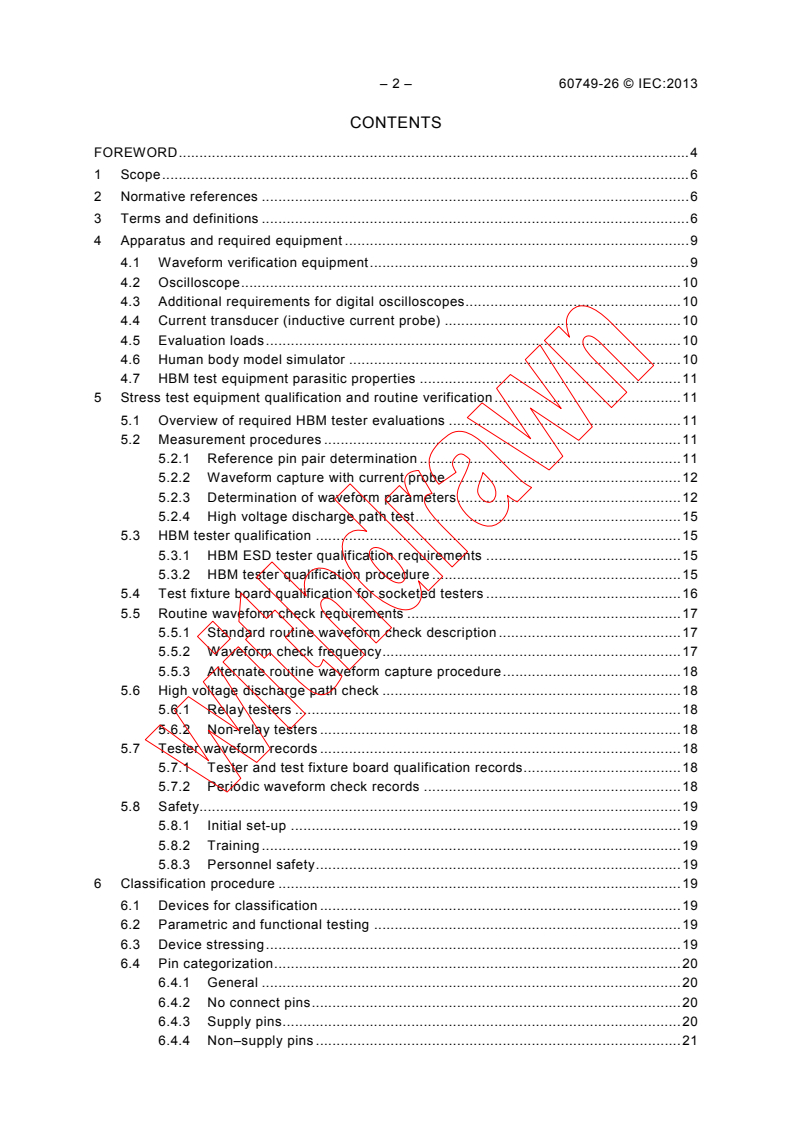

– 2 – 60749-26 © IEC:2013

CONTENTS

FOREWORD . 4

1 Scope . 6

2 Normative references . 6

3 Terms and definitions . 6

4 Apparatus and required equipment . 9

4.1 Waveform verification equipment . 9

4.2 Oscilloscope . 10

4.3 Additional requirements for digital oscilloscopes . 10

4.4 Current transducer (inductive current probe) . 10

4.5 Evaluation loads . 10

4.6 Human body model simulator . 10

4.7 HBM test equipment parasitic properties . 11

5 Stress test equipment qualification and routine verification . 11

5.1 Overview of required HBM tester evaluations . 11

5.2 Measurement procedures . 11

5.2.1 Reference pin pair determination . 11

5.2.2 Waveform capture with current probe . 12

5.2.3 Determination of waveform parameters . 12

5.2.4 High voltage discharge path test . 15

5.3 HBM tester qualification . 15

5.3.1 HBM ESD tester qualification requirements . 15

5.3.2 HBM tester qualification procedure . 15

5.4 Test fixture board qualification for socketed testers . 16

5.5 Routine waveform check requirements . 17

5.5.1 Standard routine waveform check description . 17

5.5.2 Waveform check frequency . 17

5.5.3 Alternate routine waveform capture procedure . 18

5.6 High voltage discharge path check . 18

5.6.1 Relay testers . 18

5.6.2 Non-relay testers . 18

5.7 Tester waveform records . 18

5.7.1 Tester and test fixture board qualification records . 18

5.7.2 Periodic waveform check records . 18

5.8 Safety. 19

5.8.1 Initial set-up . 19

5.8.2 Training . 19

5.8.3 Personnel safety . 19

6 Classification procedure . 19

6.1 Devices for classification . 19

6.2 Parametric and functional testing . 19

6.3 Device stressing . 19

6.4 Pin categorization . 20

6.4.1 General . 20

6.4.2 No connect pins . 20

6.4.3 Supply pins . 20

6.4.4 Non–supply pins . 21

60749-26 © IEC:2013 – 3 –

6.5 Pin groupings . 21

6.5.1 Supply pin groups . 21

6.5.2 Shorted non-supply pin groups . 22

6.6 Pin stress combinations . 22

6.6.1 Pin stress combination categorisation . 22

6.6.2 Non-supply and supply to supply combinations (1, 2, … N) . 24

6.6.3 Non-supply to non-supply combinations . 25

6.7 Testing after stressing . 26

7 Failure criteria . 26

8 Component classification . 26

Annex A (informative) HBM test method flow chart . 27

Annex B (informative) HBM test equipment parasitic properties . 30

Annex C (informative) Example of testing a product using Table 2, Table 3, or Table 2

with a two-pin HBM tester . 34

Annex D (informative) Examples of coupled non-supply pin pairs . 40

Figure 1 – Simplified HBM simulator circuit with loads . 11

Figure 2 – Current waveform through shorting wires . 13

Figure 3 – Current waveform through a 500 Ω resistor . 14

Figure 4 – Peak current short circuit ringing waveform . 15

Figure B.1 – Diagram of trailing pulse measurement setup. 30

Figure B.2 – Positive stress at 4 000 V . 31

Figure B.3 – Negative stress at 4 000 V . 31

Figure B.4 – Illustration of measuring voltage before HBM pulse with a Zener diode or

a device . 32

Figure B.5 – Example of voltage rise before the HBM current pulse across a 9,4 V

Zener diode . 32

Figure C.1 – Example to demonstrate the idea of the partitioned test . 35

Table 1 – Waveform specification . 17

Table 2 – Preferred pin combinations sets . 23

Table 3 – Alternative pin combinations sets . 24

Table 4 – HBM ESD component classification levels . 26

Table C.1 – Product testing in accordance with Table 2 . 36

Table C.2 – Product testing in accordance with Table 3 . 37

Table C.3 – Alternative product testing in accordance with Table 2 . 38

– 4 – 60749-26 © IEC:2013

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 26: Electrostatic discharge (ESD) sensitivity testing –

Human body model (HBM)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-26 has been prepared by IEC technical committee 47:

Semiconductor devices in collaboration with technical committee 101.

This third edition cancels and replaces the second edition published in 2006. This edition

constitutes a technical revision. This standard is based upon ANSI/ESDA/JEDEC JS-001-

2010. It is used with permission of the copyright holders, ESD Association and JEDEC Solid

state Technology Association.

NOTE ANSI/ESDA/JEDEC JS-001 resulted from the merging of JESD22-A114F and ANSI/ESD STM5.1.

This edition includes the following significant technical changes with respect to the previous

edition:

a) descriptions of oscilloscope and current transducers have been refined and updated;

b) the HBM circuit schematic and description have been improved;

60749-26 © IEC:2013 – 5 –

c) the description of stress test equipment qualification and verification has been completely

re-written;

d) qualification and verification of test fixture boards has been revised;

e) a new section on the determination of ringing in the current waveform has been added;

f) some alternate pin combinations have been included;

g) allowance for non-supply pins to stress to a limited number of supply pin groups

(associated non-supply pins) and allowance for non-supply to non-supply (i.e., I/O to I/O)

stress to be limited to a finite number of 2 pin pairs (coupled non-supply pin pairs);

h) explicit allowance for HBM stress using 2 pin HBM testers for die only shorted supply

groups.

The text of this standard is based on the following documents:

FDIS Report on voting

47/2160/FDIS 47/2167/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 60749 series, published under the general title Semiconductor

devices – Mechanical and climatic test methods, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct

understanding of its contents. Users should therefore print this document using a

colour printer.

– 6 – 60749-26 © IEC:2013

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 26: Electrostatic discharge (ESD) sensitivity testing –

Human body model (HBM)

1 Scope

This standard establishes the procedure for testing, evaluating, and classifying components

and microcircuits according to their susceptibility (sensitivity) to damage or degradation by

exposure to a defined human body model (HBM) electrostatic discharge (ESD).

The purpose (objective) of this standard is to establish a test method that will replicate HBM

failures and provide reliable, repeatable HBM ESD test results from tester to tester,

regardless of component type. Repeatable data will allow accurate classifications and

comparisons of HBM ESD sensitivity levels.

ESD testing of semiconductor devices is selected from this test method, the machine model

(MM) test method (see IEC 60749-27) or other ESD test methods in the IEC 60749 series.

The HBM and MM test methods produce similar but not identical results; unless otherwise

specified, this test method is the one selected.

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60749-27, Semiconductor devices – Mechanical and climatic test methods – Part 27:

Electrostatic discharge (ESD) sensitivity testing – Machine model (MM)

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

3.1

associated non-supply pin

non-supply pin (typically an I/O pin) associated with a supply pin group

Note 1 to entry: A non-supply pin is considered to be associated with a supply pin group if either:

a) The current from the supply pin group (i.e., VDDIO) is required for the function of the electrical circuit(s) (I/O

driver) that connect (high/low impedance) to that non-supply pin.

b) A parasitic path exists between non-supply and supply pin group (e.g., open-drain type non-supply pin to a

VCC supply pin group that connects to a nearby N-well guard ring).

3.2

component

item such as a resistor, diode, transistor, integrated circuit or hybrid circuit

60749-26 © IEC:2013 – 7 –

3.3

component failure

condition in which a tested component does not meet one or more specified static or dynamic

data sheet parameters

3.4

coupled non-supply pin pair

two pins that have an intended direct current path (such as a pass gate or resistors, such as

differential amplifier inputs, or low voltage differential signaling (LVDS) pins), including

analogue and digital differential pairs and other special function pairs (e.g., D+/D-,

XTALin/XTALout, RFin/RFout, TxP/TxN, RxP/RxN, CCP_DP/CCN_DN etc.)

3.5

data sheet parameters

static and dynamic component performance data supplied by the component manufacturer or

supplier

3.6

withstand voltage

highest voltage level that does not cause device failure

Note 1 to entry: The device passes all tested lower voltages (see failure Window).

3.7

failure window

intermediate range of stress voltages that can induce failure in a particular device type, when

the device type can pass some stress voltages both higher and lower than this range

Note 1 to entry: A component with a failure window may pass a 500 V test, fail a 1 000 V test and pass 2 000 V

test. The withstand voltage of this device is 500 V.

3.8

human body model electrostatic discharge

HBM ESD

ESD event meeting the waveform criteria specified in this standard, approximating the

discharge from the fingertip of a typical human being to a grounded device

3.9

HBM ESD tester

HBM simulator

equipment that applies an HBM ESD to a component

3.10

I

ps

peak current value determined by the current at time t on the linear extrapolation of the

max

exponential current decay curve, based on the current waveform data over a 40 nanosecond

period beginning at t

max

SEE: Figure 2 a).

3.11

I

psmax

highest current value measured including the overshoot or ringing components due to internal

test simulator RLC parasitics

SEE: Figure 2 a).

3.12

no connect pin

package interconnection that is not electrically connected to a die

– 8 – 60749-26 © IEC:2013

EXAMPLE: Pin, bump, ball interconnection.

Note 1 to entry: There are some pins which are labelled as no connect, which are actually connected to the die

and should not be classified as a no connect pin.

3.13

non-socketed tester

HBM simulator that makes contact to the device under test (DUT), pins (or balls, lands, bumps

or die pads) with test probes rather than placing the DUT in a socket

3.14

non-supply pins

all pins not categorized as supply pins or no connects

Note 1 to entry: This includes pins such as input, output, offset adjusts, compensation, clocks, controls, address,

data, Vref pins and VPP pins on EPROM memory. Most non-supply pins transmit or receive information such as

digital or analog signals, timing, clock signals, and voltage or current reference levels.

3.15

package plane

low impedance metal layer built into an IC package connecting a group of bumps or pins

(typically power or ground)

Note 1 to entry: There may be multiple package planes (sometimes referred to as islands) for each power and

ground group.

3.16

pre-pulse voltage

voltage occurring at the device under test (DUT) just prior to the generation of the HBM

current pulse

SEE: Clause C.2.

3.17

pulse generation circuit

dual polarity pulse source circuit network that produces a human body discharge current

waveform

Note 1 to entry: The circuit network includes a pulse generator with its test equipment internal path up to the

contact pad of the test fixture. This circuit is also referred to as dual polarity pulse source.

3.18

ringing

high frequency oscillation superimposed on a waveform

3.19

shorted non-supply pin

any non-supply pin (typically an I/O pin) that is metallically connected (typically < 3 Ω) on the

chip or within the package to another non-supply pin (or set of non-supply pins)

3.20

spurious current pulses

small HBM shaped pulses that follow the main current pulse, and are typically defined as a

percentage of I

psmax

3.21

socketed tester

an HBM simulator that makes contact to DUT pins (or balls, lands, bumps or die pads) using a

DUT socket mounted on a test fixture board

60749-26 © IEC:2013 – 9 –

3.22

static parameters

parameters measured with the component in a non-operating condition

Note 1 to entry: These may include, but are not limited to, input leakage current, input breakdown voltage, output

high and low voltages, output drive current, and supply current.

3.23

step stress test hardening

ability of a component subjected to increasing ESD voltage stresses to withstand higher

stress levels than a similar component not previously stressed

EXAMPLE: A component may fail at 1 000 V if subjected to a single stress, but fail at 3 000 V if stressed

incrementally from 250 V.

3.24

supply pin

any pin that provides current to a circuit

Note 1 to entry: Supply pins typically transmit no information (such as digital or analogue signals, timing, clock

signals, and voltage or current reference levels). For the purpose of ESD testing, power and ground pins are

treated as supply pins.

3.25

test fixture board

specialized circuit board, with one or more component sockets, which connects the DUT(s) to

the HBM simulator

3.26

t

max

time when I is at its maximum value (I )

ps psmax

SEE: Figure 2a).

3.27

trailing current pulse

current pulse that occurs after the HBM current pulse has decayed

SEE: Clause C.1.

Note 1 to entry: A trailing current pulse is a relatively constant current often lasting for hundreds of microseconds.

3.28

two pin tester

A low parasitic HBM simulator that tests DUTs in pin pairs where floating pins are not

connected to the simulator thereby eliminating DUT-tester interactions from parasitic tester

loading of floating pins

4 Apparatus and required equipment

4.1 Waveform verification equipment

All equipment used to evaluate the tester shall be calibrated in accordance with the

manufacturer's recommendation. This includes the oscilloscope, current transducer and high

voltage resistor load. Maximum time between calibrations shall be one year. Calibration shall

be traceable to national or international standards.

Equipment capable of verifying the pulse waveforms defined in this standard test method

includes, but is not limited to, an oscilloscope, evaluation loads and a current transducer.

– 10 – 60749-26 © IEC:2013

4.2 Oscilloscope

A digital oscilloscope is recommended but analogue oscilloscopes are also permitted. In order

to ensure accurate current waveform capture, the oscilloscope shall meet the following

requirements:

a) Minimum sensitivity of 100 mA per major division when used in conjunction with the

current transducer specified in 4.4;

b) Minimum bandwidth of 350 MHz;

c) For analogue scopes, minimum writing rate of one major division per nanosecond.

4.3 Additional requirements for digital oscilloscopes

Where a digital oscilloscope is used the following additional requirements apply:

a) Recommended channels: 2 or more;

b) Minimum sampling rate: 10 samples per second;

c) Minimum vertical resolution: 8-bit;

d) Minimum vertical accuracy: ± 2,5 %;

e) Minimum time base accuracy: 0,01 %;

f) Minimum record length: 10 k points.

4.4 Current transducer (inductive current probe)

a) Minimum bandwidth of 200 MHz;

b) Peak pulse capability of 12 A;

c) Rise time of less than 1 ns;

d) Capable of accepting a solid conductor as specified in 4.5;

e) Provides an output voltage per signal current as required in 4.2

(This is usually between 1 mV/mA and 5 mV/mA.);

f) Low-frequency 3 dB point below 10 kHz (e.g., Tektronix CT2) for measurement of decay

constant t (see 5.2.3.2, Table 1, and Note below).

d

NOTE Results using a current probe with a low-frequency 3 dB point of 25 kHz (e.g., Tektronix CT1) to measure

decay constant t are acceptable if t is found to be between 130 ns and 165 ns.

d d

4.5 Evaluation loads

Two evaluation loads are necessary to verify tester functionality:

a) Load 1: A solid 18 – 24 AWG (non-US standard wire size 0,25 to 0,75 mm cross-section)

tinned copper shorting wire as short as practicable to span the distance between the two

farthest pins in the socket while passing through the current probe or long enough to pass

through the current probe and contacted by the probes of the non-socketed tester.

b) Load 2: A 500 Ω, ± 1 %, minimum 4 000 voltage rating.

4.6 Human body model simulator

A simplified schematic of the HBM simulator or tester is given in Figure 1. The performance of

the tester is influenced by parasitic capacitance and inductance. Thus, construction of a tester

using this schematic does not guarantee that it will provide the HBM pulse required for this

standard. The waveform capture procedures and requirements described in Clause 5

determine the acceptability of the equipment for use.

60749-26 © IEC:2013 – 11 –

Dual polarity

pulse source

Terminal

S1

R1 ≥ 1 MΩ R2 ∼ 1 500 Ω A

Dual polarity

C1 ∼ 100 pF

HV supply

Terminal

B

Current

probes

IEC 893/13

Figure 1 – Simplified HBM simulator circuit with loads

The charge removal circuit shown in Figure 1 ensures a slow discharge of the device, thus

avoiding the possibility of a charged device model discharge. A simple example is a 10 kΩ or

larger resistor (possibly in series with a switch) in parallel with the test fixture board. This

resistor may also be useful to control parasitic pre-pulse voltages (See Annex C). The dual

polarity pulse generator (source) shall be designed to avoid recharge transients and double

pulses. It should be noted that reversal of terminals A and B to achieve dual polarity

performance is not permitted. Stacking of DUT socket adapters (piggybacking or insertion of

secondary sockets into the main test socket) is allowed only if the secondary socket waveform

meets the requirements of this standard defined in Table 1.

NOTE 1 The current transducers (probes) are specified in 4.4.

NOTE 2 The shorting wire (short) and 500 Ω resistor (R4) are evaluation loads specified in 4.5.

NOTE 3 Component values are nominal.

4.7 HBM test equipment parasitic properties

Some HBM simulators have been found to falsely classify HBM sensitivity levels due to

parasitic artifacts or uncontrolled voltages unintentionally built into the HBM simulators.

Methods for determining if these effects are present and optional mitigation techniques are

described in Annex C. Two-pin testers and non-socketed testers may have smaller parasitic

capacitances and may reduce the effects of tester parasitics by contacting only the pins being

stressed.

5 Stress test equipment qualification and routine verification

5.1 Overview of required HBM tester evaluations

The HBM tester and test fixture boards shall be qualified, re-qualified, and periodically verified

as described in this clause. The safety precautions described in 5.8 shall be followed at all

times.

5.2 Measurement procedures

5.2.1 Reference pin pair determination

The two pins of each socket on a test fixture board which make up the reference pin pair are

(1) the socket pin with the shortest wiring path of the test fixture to the pulse generation circuit

(terminal B) and (2) the socket pin with the longest wiring path of the test fixture from the

pulse generation circuit (terminal A) to the ESD stress socket (See Figure 1). This information

is typically provided by the equipment or test fixture board manufacturer. If more than one

pulse generation circuit is connected to a socket then there will be more than one reference

pin pair.

Charge

removal

circuit

Test

fixture

board

Short

R4 =

500 Ω

DUT

– 12 – 60749-26 © IEC:2013

It is strongly recommended that on non-positive clamp fixtures, feed through test point pads

be added on these paths to allow connection of either the shorting wire or 500 Ω load resistor

during waveform verification measurements. These test points should be added as close as

possible to the socket(s), and if the test fixture board uses more than one pulse generator,

multiple feed through test points should be added for each pulse generator’s longest and

shortest paths.

NOTE A positive clamp test socket is a zero insertion force (ZIF) socket with a clamping mechanism. It allows the

shorting wire to be easily clamped into the socket. Examples are dual in-line package (DIP) and pin grid array

(PGA) ZIF sockets.

5.2.2 Waveform capture with current probe

5.2.2.1 General

To capture a current waveform between two socket pins (usually the reference pin pair), use

the shorting wire (4.5, Load 1) for the short circuit measurement or the 500 Ω resistor (4.5,

Load 2) for the 500 Ω current measurement and the inductive current probe (4.4).

5.2.2.2 Short circuit current waveform

Attach the shorting wire between the pins to be measured. Place the current probe around the

shorting wire, as close to terminal B as practical, observing the polarity shown in Figure 1.

Apply an ESD stress at the voltage and polarity needed to execute the qualification, re-

qualification or periodic verification being conducted.

a) For positive clamp sockets, insert the shorting wire between the socket pins connected to

terminals A and B and hold in place by closing the clamp.

b) For non-positive clamp sockets, attach the shorting wire between the socket pins

connected to terminals A and B. If it is not possible to make contact within the socket,

connect the shorting wire between the reference pin pair test points or socket mounting

holes, if available. The design of the socket is important as some socket types may

include contact springs (coils) in their design. These springs can add more parasitic

inductance to the signal path and may affect the HBM waveform. Selecting sockets that

minimize the use of springs (coils) is recommended, but if this is not possible, then

keeping their length as short as possible is recommended.

c) For non-socketed testers, the shorting wire with the inductive current probe is placed on

an insulating surface and the simulator terminal A and terminal B probes are placed on the

ends of the wires.

5.2.2.3 500 Ω load current waveform

Place the current probe around the 500 Ω resistor’s lead, observing the polarity as shown in

Figure 1. Attach the 500 Ω resistor between the pins to be measured. The current probe shall

be placed around the wire between the resistor and terminal B. Apply an ESD stress at the

voltage and polarity needed to execute the qualification, re-qualification or periodic

verification being conducted.

a) For socketed testers, follow procedures according to socket type as described in 5.2.2.2.

b) For non-socketed testers, place the test load and current probe on an insulating surface

and connect the tester’s probes to the ends of the test load.

5.2.3 Determination of waveform parameters

5.2.3.1 Use of waveforms

The captured waveforms are used to determine the parameter values listed in Table 1.

60749-26 © IEC:2013 – 13 –

5.2.3.2 Short circuit waveform

Typical short circuit waveforms are shown in Figures 2a), 2b) and 4. The parameters I (peak

ps

current), t (pulse rise time), t (pulse decay time) and I (ringing) are determined from these

r d R

waveforms. Ringing may prevent the simple determination of I A graphical technique for

ps.

determining I and I is described in 5.2.3.4 and Figure 4.

ps R

5.2.3.3 500 Ω load waveform

A typical 500 Ω load waveform is shown in Figure 3. The parameters I (peak current with

pr

(pulse rise time with 500 Ω load) are determined from this waveform.

500 Ω load) and t

rr

I

psmax

I

ps

90 % I

ps

10 % I

ps

Time (ns)

t

r

40 ns

5 ns per division

t

max

IEC 894/1 3

a) Current waveform through a shorting wire (I )

psmax

I

ps

36,8 % I

ps

Time (ns)

100 ns per division

t

d

t

max

IEC 895/13

b) Current waveform through a shorting wire (t )

d

Figure 2 – Current waveform through shorting wires

Current (A) Current (A)

– 14 – 60749-26 © IEC:2013

I

pr

90 % I

pr

10 % I

pr

0 Time (ns)

t

rr

5 ns per division

IEC 896/13

Figure 3 – Current waveform through a 500 Ω resistor

5.2.3.4 Graphical determination of I and I (see Figure 4)

ps R

5.2.3.4.1 A line is drawn (manually or using numerical methods such as least squares)

through the HBM ringing waveform from t to t + 40 ns to interpolate the value of the

max max

curve for a more accurate derivation of the peak current value (I ). t is the time when

ps max

I occurs (see definition for t in Clause 3 and Figure 2a)).

psmax max

5.2.3.4.2 The maximum deviation of the measured current above the straight line fit is Ring1.

The maximum deviation of the measured current below the straight line fit is Ring2. The

maximum ringing current during a short circuit waveform measurement is defined as:

= |Ring1| + |Ring2|

I

R

Current (mA)

60749-26 © IEC:2013 – 15 –

1,68

1,66

1,64

1,62

1,60

1,58

1,56

1,54

1,52

1,50

I

psmax

1,48

1,46

I

ps

1,44

1,42

1,40

1,38

Ring2 Ring1

1,36

1,34

1,32

I = |Ring1| + |Ring2|

R

1,30

1,28

1,26

1,24

1,22

1,20

1,18

0 2,5 5,0 7,5 10,0 12,5 15,0 17,5 20,0 22,5 25,0

Time (ns)

IEC 897/13

Figure 4 – Peak current short circuit ringing waveform

5.2.4 High voltage discharge path test

This test is only required for relay-based testers. This test is intended to ensure that the tester

high voltage relays and the grounding relays that connect pulse generator(s) (i.e. terminal A)

and current return paths (i.e. terminal B) to the DUT are functioning properly. The tester

manufacturer should provide a recommended procedure and if needed, a verification board

and software.

5.3 HBM tester qualification

5.3.1 HBM ESD tester qualification requirements

HBM ESD tester qualification as described in 5.3 is required in the following situations:

a) Acceptance testing when the ESD tester is delivered or first used.

b) Periodic re-qualification in accordance with manufacturer’s recommendations. The

maximum time between re-qualification tests is one year.

c) After service or repair that could affect the waveform.

5.3.2 HBM tester qualification procedure

5.3.2.1 Test fixture board, socket and pins for socketed testers only

Use the highest pin count test fixture board with a positive clamp socket for the tester

waveform verification or the recommended waveform verification board provided by the

manufacturer.

The reference pin pair(s) of the highest pin count socket on the board shall be used for

waveform capture. Waveforms from every pulse generating circuit are to be recorded.

Current (A)

– 16 – 60749-26 © IEC:2013

Electrical continuity for all pins on the test fixture board shall be verified prior to qualification

testing. This can typically be done using the manufacturer’s recommended self-test.

5.3.2.2 Short circuit waveform capture

a) For socketed testers, configure the test fixture board, shorting wire, and transducer for the

short circuit waveform measurement as described in 5.2.2.2.

For non-socketed testers, configure the test fixture board, shorting wire, and transducer

for the short circuit waveform measurement as described in 5.2.2.2 c).

b) Apply five positive and five negative pulses at each test voltage. Record waveforms at

1 000, 2 000 and 4 000 V. Verify that the waveforms meet all parameters specified in

Figures 2a) and 2b) and Table 1.

5.3.2.3 500 Ω load waveform capture

a) For socketed testers, configure the test fixture board, resistor, and transducer for the

500 Ω load waveform measurement as described in 5.2.2.3 a).

For non-socketed testers, configure the test fixture board, resistor, and transducer for the

500 Ω load waveform measurement as described in 5.2.2.3 b).

b) Record waveforms at 1 000 and 4 000 V, both positive an

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...