IEC 61188-6-2:2021

(Main)Circuit boards and circuit board assemblies - Design and use - Part 6-2: Land pattern design - Description of land pattern for the most common surface mounted components (SMD)

Circuit boards and circuit board assemblies - Design and use - Part 6-2: Land pattern design - Description of land pattern for the most common surface mounted components (SMD)

IEC 61188-6-2:2021 describes the requirements of design and use for soldering surfaces of land pattern on circuit boards. This document includes land pattern for surface mounted components. These requirements are based on the solder joint requirements of IEC 61191‑2:2017.

Cartes imprimées et cartes imprimées équipées - Conception et utilisation - Partie 6-2: Conception de la zone de report - Description de la zone de report pour les composants montés en surface (CMS) les plus courants

L’IEC 61188-6-2:2021 décrit les exigences de conception et d’utilisation relatives aux surfaces de brasage de la zone de report sur les cartes imprimées. Le présent document porte notamment sur la zone de report des composants montés en surface. Ces exigences se fondent sur les exigences relatives aux joints de brasure de l’IEC 61191-2:2017.

General Information

- Status

- Published

- Publication Date

- 03-Feb-2021

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 12 - TC 91/WG 12

- Current Stage

- PPUB - Publication issued

- Start Date

- 04-Feb-2021

- Completion Date

- 02-Mar-2021

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 61188-6-2:2021 establishes essential requirements for the design and use of land patterns for surface mounting components (SMD) on circuit boards. Developed by the International Electrotechnical Commission (IEC), this standard provides comprehensive guidelines to ensure the compatibility and reliability of soldering surfaces for the most common SMD packages. Grounded in the solder joint requirements of IEC 61191‑2, IEC 61188-6-2 is a critical reference for PCB designers, manufacturers, and anyone involved in electronic assembly. The document outlines both generic and specific approaches to land pattern dimensioning, catering to reflow and wave soldering processes and supporting quality-driven, consistent PCB manufacturing worldwide.

Key Topics

- Land Pattern Design Principles

- Describes how to determine the correct dimensions for SMD land patterns, including considerations for component and board tolerances, and soldering process type (reflow or wave soldering).

- Solder Joint Requirements

- Aligns with IEC 61191-2 to ensure solder joint reliability and improve assembly quality.

- Terminal and Package Types

- Details dimensioning for multiple SMD terminal configurations, including flat bottom, gull wing, J-lead, and bottom termination types.

- Class of Land Pattern

- Differentiates land pattern requirements based on soldering method, supporting robust attachment and inspection.

- Courtyard Excess and Producibility

- Addresses the need for courtyard excess based on equipment performance and component size, balancing manufacturability and reliability.

Applications

IEC 61188-6-2:2021 is directly applicable in the following scenarios:

- PCB Layout Design

- Enables PCB designers to define optimal footprint dimensions, reducing the risk of soldering defects and mechanical issues.

- Electronic Assembly & Manufacturing

- Guides manufacturers in selecting or verifying land pattern dimensions for high-volume SMD assembly using reflow or wave soldering.

- Quality Assurance and Process Optimization

- Supports engineers in meeting inspection criteria and reliability standards by adhering to globally recognized land pattern rules.

- Library and CAD System Integration

- Provides a standardized approach for creating and managing component land pattern libraries in electronic CAD systems.

- Component Selection and PCB Producibility

- Assists purchasers and designers in ensuring selected components can be reliably mounted and soldered on the PCB, minimizing rework and field failures.

By adhering to this standard, organizations enhance product consistency, interoperability, and global market acceptance.

Related Standards

For a comprehensive approach to PCB and SMD assembly, IEC 61188-6-2:2021 should be applied alongside the following standards:

- IEC 61191-2:2017 – Defines general and process requirements for surface mount soldered assemblies, forming the technical foundation for land pattern requirements.

- IEC 60194-2 – Provides standardized terminologies for printed board and electronic technologies.

- IEC 61188-6-1 – Offers generic requirements for land pattern design, applicable to a broad range of PCB types.

- IEC 61188-6-4 – Focuses on dimensional drawings of SMD from the perspective of land pattern design, supporting accurate footprint creation.

Implementing IEC 61188-6-2 in harmony with these international standards streamlines PCB design workflows, ensures compliance, and fosters high-quality, reliable electronic products.

Keywords: IEC 61188-6-2, SMD land pattern, surface mounted components, PCB design, solder joint requirements, reflow soldering, wave soldering, printed circuit board patterns, electronic assembly standards, IEC 61191-2 compliance, PCB land pattern standard.

Buy Documents

IEC 61188-6-2:2021 - Circuit boards and circuit board assemblies - Design and use - Part 6-2: Land pattern design - Description of land pattern for the most common surface mounted components (SMD) Released:2/4/2021

Frequently Asked Questions

IEC 61188-6-2:2021 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Circuit boards and circuit board assemblies - Design and use - Part 6-2: Land pattern design - Description of land pattern for the most common surface mounted components (SMD)". This standard covers: IEC 61188-6-2:2021 describes the requirements of design and use for soldering surfaces of land pattern on circuit boards. This document includes land pattern for surface mounted components. These requirements are based on the solder joint requirements of IEC 61191‑2:2017.

IEC 61188-6-2:2021 describes the requirements of design and use for soldering surfaces of land pattern on circuit boards. This document includes land pattern for surface mounted components. These requirements are based on the solder joint requirements of IEC 61191‑2:2017.

IEC 61188-6-2:2021 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards; 31.190 - Electronic component assemblies. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61188-6-2:2021 has the following relationships with other standards: It is inter standard links to IEC 61188-5-5:2007, IEC 61188-5-2:2003, IEC 61188-5-3:2007, IEC 61188-5-6:2003, IEC 61188-5-8:2007, IEC 61188-5-4:2007. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 61188-6-2:2021 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 61188-6-2 ®

Edition 1.0 2021-02

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Circuit boards and circuit board assemblies – Design and use –

Part 6-2: Land pattern design – Description of land pattern for the most common

surface mounted components (SMD)

Cartes imprimées et cartes imprimées équipées – Conception et utilisation –

Partie 6-2: Conception de la zone de report – Description de la zone de report

pour les composants montés en surface (CMS) les plus courants

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC online collection - oc.iec.ch

The advanced search enables to find IEC publications by a Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews. With a subscription you will always

committee, …). It also gives information on projects, replaced have access to up to date content tailored to your needs.

and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published

containing more than 22 000 terminological entries in English

details all new publications released. Available online and

and French, with equivalent terms in 18 additional languages.

once a month by email.

Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service

Centre: sales@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Recherche de publications IEC - IEC online collection - oc.iec.ch

webstore.iec.ch/advsearchform Découvrez notre puissant moteur de recherche et consultez

La recherche avancée permet de trouver des publications IEC gratuitement tous les aperçus des publications. Avec un

en utilisant différents critères (numéro de référence, texte, abonnement, vous aurez toujours accès à un contenu à jour

comité d’études, …). Elle donne aussi des informations sur adapté à vos besoins.

les projets et les publications remplacées ou retirées.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

Le premier dictionnaire d'électrotechnologie en ligne au

Restez informé sur les nouvelles publications IEC. Just

monde, avec plus de 22 000 articles terminologiques en

Published détaille les nouvelles publications parues.

anglais et en français, ainsi que les termes équivalents dans

Disponible en ligne et une fois par mois par email.

16 langues additionnelles. Egalement appelé Vocabulaire

Electrotechnique International (IEV) en ligne.

Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette

publication ou si vous avez des questions contactez-nous:

sales@iec.ch.

IEC 61188-6-2 ®

Edition 1.0 2021-02

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Circuit boards and circuit board assemblies – Design and use –

Part 6-2: Land pattern design – Description of land pattern for the most common

surface mounted components (SMD)

Cartes imprimées et cartes imprimées équipées – Conception et utilisation –

Partie 6-2: Conception de la zone de report – Description de la zone de report

pour les composants montés en surface (CMS) les plus courants

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.180; 31.190 ISBN 978-2-8322-9354-6

– 2 – IEC 61188-6-2:2021 IEC 2021

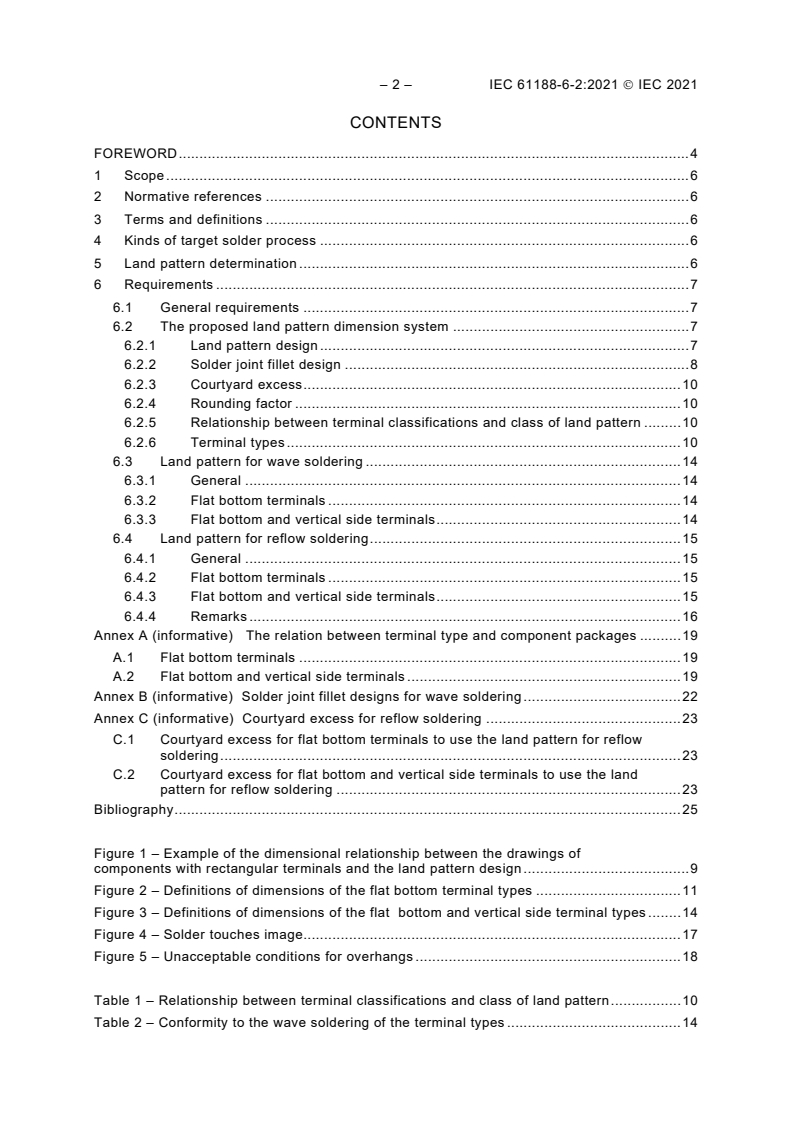

CONTENTS

FOREWORD . 4

1 Scope . 6

2 Normative references . 6

3 Terms and definitions . 6

4 Kinds of target solder process . 6

5 Land pattern determination . 6

6 Requirements . 7

6.1 General requirements . 7

6.2 The proposed land pattern dimension system . 7

6.2.1 Land pattern design . 7

6.2.2 Solder joint fillet design . 8

6.2.3 Courtyard excess . 10

6.2.4 Rounding factor . 10

6.2.5 Relationship between terminal classifications and class of land pattern . 10

6.2.6 Terminal types . 10

6.3 Land pattern for wave soldering . 14

6.3.1 General . 14

6.3.2 Flat bottom terminals . 14

6.3.3 Flat bottom and vertical side terminals . 14

6.4 Land pattern for reflow soldering . 15

6.4.1 General . 15

6.4.2 Flat bottom terminals . 15

6.4.3 Flat bottom and vertical side terminals . 15

6.4.4 Remarks . 16

Annex A (informative) The relation between terminal type and component packages . 19

A.1 Flat bottom terminals . 19

A.2 Flat bottom and vertical side terminals . 19

Annex B (informative) Solder joint fillet designs for wave soldering . 22

Annex C (informative) Courtyard excess for reflow soldering . 23

C.1 Courtyard excess for flat bottom terminals to use the land pattern for reflow

soldering . 23

C.2 Courtyard excess for flat bottom and vertical side terminals to use the land

pattern for reflow soldering . 23

Bibliography . 25

Figure 1 – Example of the dimensional relationship between the drawings of

components with rectangular terminals and the land pattern design . 9

Figure 2 – Definitions of dimensions of the flat bottom terminal types . 11

Figure 3 – Definitions of dimensions of the flat bottom and vertical side terminal types . 14

Figure 4 – Solder touches image. 17

Figure 5 – Unacceptable conditions for overhangs . 18

Table 1 – Relationship between terminal classifications and class of land pattern . 10

Table 2 – Conformity to the wave soldering of the terminal types . 14

Table 3 – Land pattern dimensions for Flat bottom terminals soldered by reflow

soldering . 15

Table 4 – Land pattern dimensions for flat bottom and vertical side terminals soldered

by reflow soldering . 16

Table A.1 – Terminal type classifications 1 – Flat bottom terminals . 19

Table A.2 – Terminal type classifications 2 – Flat bottom and vertical side terminals . 20

Table B.1 – Solder joint fillet design for wave soldering . 22

Table C.1 – Courtyard excess for flat bottom terminals to use the land pattern for

reflow soldering . 23

Table C.2 – Courtyard excess for flat bottom and vertical side terminals to use the

land pattern for reflow soldering . 24

– 4 – IEC 61188-6-2:2021 IEC 2021

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

CIRCUIT BOARDS AND CIRCUIT BOARD ASSEMBLIES –

DESIGN AND USE –

Part 6-2: Land pattern design – Description of land pattern

for the most common surface mounted components (SMD)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC Publication(s)”). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for

Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence between

any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent

rights. IEC shall not be held responsible for identifying any or all such patent rights.

IEC 61188-6-2 has been prepared by IEC technical committee 91: Electronics assembly

technology. It is an International Standard.

The text of this International Standard is based on the following documents:

Draft Report on voting

91/1637/CDV 91/1657/RVC

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in

accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available

at www.iec.ch/members_experts/refdocs. The main document types developed by IEC are

described in greater detail at www.iec.ch/standardsdev/publications.

A list of all parts in the IEC 61188 series, published under the general title Circuit boards and

circuit board assemblies – Design and use, can be found on the IEC website.

Future documents in this series will carry the new general title as cited above. Titles of existing

documents in this series will be updated at the time of the next edition.

The committee has decided that the contents of this document will remain unchanged until the

stability date indicated on the IEC website under webstore.iec.ch in the data related to the

specific document. At this date, the document will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it

contains colours which are considered to be useful for the correct understanding of its

contents. Users should therefore print this document using a colour printer.

– 6 – IEC 61188-6-2:2021 IEC 2021

CIRCUIT BOARDS AND CIRCUIT BOARD ASSEMBLIES –

DESIGN AND USE –

Part 6-2: Land pattern design – Description of land pattern

for the most common surface mounted components (SMD)

1 Scope

This part of IEC 61188 describes the requirements of design and use for soldering surfaces of

land pattern on circuit boards. This document includes land pattern for surface mounted

components. These requirements are based on the solder joint requirements of

IEC 61191-2:2017.

2 Normative references

The following documents are referred to in the text in such a way that some or all of their content

constitutes requirements of this document. For dated references, only the edition cited applies.

For undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60194-2, Printed boards design, manufacture and assembly – Vocabulary – Part 2:

Common usage in electronic technologies as well as printed board and electronic assembly

technologies

IEC 61188-6-1, Circuit boards and circuit board assemblies – Design and use – Part 6-1: Land

pattern design – Generic requirements for land pattern on circuit boards

IEC 61188-6-4, Printed boards and printed board assemblies – Design and use – Part 6-4: Land

pattern design – Generic requirements for dimensional drawings of surface mounted

components (SMD) from the viewpoint of land pattern design

IEC 61191-2:2017, Printed board assemblies – Part 2: Sectional specification – Requirements

for surface mount soldered assemblies

3 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60194-2 and

IEC 61188-6-1 apply.

ISO and IEC maintain terminological databases for use in standardization at the following

addresses:

• IEC Electropedia: available at http://www.electropedia.org/

• ISO Online browsing platform: available at http://www.iso.org/obp

4 Kinds of target solder process

Typical soldering methods used in surface mount technology include, but are not limited to:

a) reflow soldering for all process types;

b) wave soldering of surface mounted component.

5 Land pattern determination

This standard discusses the following method of providing information on land patterns.

For each typical termination type, one land pattern for one termination will be determined by

formulas based on the termination dimensions (nominal value).

The assumption is that the following dimensions have the necessary and sufficient accuracy:

a) component tolerance;

c) printed board fabrication tolerance;

d) placement tolerance.

NOTE Further information on the effect of the above dimensional tolerance on the land pattern can be found in

Annex A of IEC 61188-6-1:2021.

There are two classes of land pattern relating to the assembly limitations of components and

the intended soldering process:

• land pattern for wave soldering – For low density product applications, land patterns are

designed to accommodate several types of wave soldering applicable to surface mounted

components.

• land pattern for reflow soldering – The land patterns generated for all device families shall

provide a robust solder attachment condition for reflow soldering.

6 Requirements

6.1 General requirements

The calculated land pattern geometry for an electronic component can be different depending

upon the type of soldering process to be used. Wherever possible, land patterns should be

defined in such a manner that are transparent to the attachment process being used. Land

pattern designers can use the information contained herein to establish standard configurations

not only for manual designs but also for computer-aided design systems.

Whether parts are mounted on one side or both sides of the board, subjected to wave soldering,

reflow soldering, or other type of soldering, the land pattern and part dimensions should be

optimized to insure proper solder joint and inspection criteria.

Although patterns are dimensionally defined and since they are a part of the circuit board

geometry, they are subject to the reducibility levels and tolerances associated with plating,

etching, assembly or other conditioning process. The producibility aspects also pertain to the

use of solder mask and the registration required between the solder mask and the conductor

patterns.

A correctly designed land pattern is essential to satisfy quality standards such as IEC 61191-

2:2017, which specifies generic requirements for the concept of land pattern design. The land

pattern designer should design in accordance with the concept in this document, and they could

adopt appropriate numeric values that were suitable for their purpose. The numeric values

described in this document are the parameters that were selected as references to show the

concept of land-pattern design.

6.2 The proposed land pattern dimension system

6.2.1 Land pattern design

Distance between lands measured from outside edges (Z) and distance between lands

measured from inside edges (G) are given by the following Formula (1) and Formula (2).

NOTE In Figure 1 e), the area surrounded by dashed lines is the courtyard.

Figure 1 shows a typical example of the relationship between the land pattern design and the

component dimensions. The requirements contained in IEC 61188-6-4 about the relationship

between dimensions shall apply.

Z = H + 2 × J (1)

E T

G = S − 2 × J (2)

H

where:

Z is the distance between lands, expressed in mm. Measured from outside edges;

– 8 – IEC 61188-6-2:2021 IEC 2021

G is the distance between lands, expressed in mm. Measured from inside edges;

H is the SMD total length (nominal), expressed in mm;

E

S is the distance between the solder terminals measured from inside edges, expressed in mm;

J is the toe protrusion length, expressed in mm;

T

J is the heel protrusion length, expressed in mm.

H

6.2.2 Solder joint fillet design

Land width (X) and land length (Y) are given by the following Formula (3) and Formula (4).

XW+×2 J

1S

(3)

YJ= ++L J

T PH

(4)

where

X is the land width (nominal), expressed in mm;

Y is the land length (nominal), expressed in mm;

W is the terminal width (nominal), expressed in mm;

L is the solder terminal length (nominal), expressed in mm;

P

J is the toe protrusion length, expressed in mm;

T

J is the heel protrusion length, expressed in mm;

H

J is the side protrusion length, expressed in mm.

S

=

Key

H

SMD total length (nominal) X Land width

E

W

Y

Terminal width (nominal) Land length

SMD height (from the mounting surface to the Distance between lands. Measured from inside

A G

package upper surface) (nominal) edges

Solder terminal length (mounting surface side)

L

C Row spacing. Distance between land centers

P

(nominal)

Distance between the solder terminals. Distance between lands. Measured from outside

S Z

Measured from inside edges edges

J CY

Toe protrusion length Courtyard width

T 1

J CY

Heel protrusion length Courtyard length

H 2

J u , u

Side protrusion length Allowance for courtyard

S 1 2

NOTE In Figure 1 e), the area surrounded by dashed lines is the courtyard.

Figure 1 – Example of the dimensional relationship between the drawings of

components with rectangular terminals and the land pattern design

– 10 – IEC 61188-6-2:2021 IEC 2021

6.2.3 Courtyard excess

Since courtyard excess is influenced by equipment performance, part size accuracy, provision

for rework, etc., it should be desirable for the user to decide it. Therefore, in this document,

courtyard excess is indicated as a reference value in Annex C.

6.2.4 Rounding factor

The rounding factor of the land pattern dimension should be 0,01 mm in general. However, if

the rounding factor exceeds 10 % of the dimension, the rounding factor can be decreased to

0,005 mm.

6.2.5 Relationship between terminal classifications and class of land pattern

Relationship between terminal classifications and class of land pattern are given in Table 1.

For the relationship between each terminal type contained in the terminal classifications and

component classifications, see Annex A.

Table 1 – Relationship between terminal classifications and class of land pattern

Terminal Class of land pattern

classification

For wave soldering For reflow soldering

Flat bottom terminals 6.3.2 6.4.1

(The basic design rule is not defined) The basic design rule is shown in Table

Flat bottom and vertical 6.3.3 6.4.2

side terminals Available termination types are shown The basic design rule is shown in Table

in Table 2 4

(The basic design rule is not defined)

6.2.6 Terminal types

Figure 2 shows the flat bottom terminal types, and Figure 3 shows the Flat bottom and vertical

side terminal types with dimension symbols used in this document.

a) Bottom only chip terminal

1) Before soldering 2) After soldering

b) BGA terminal

c) BTC (QFN) terminal

Key

Øb Terminal diameter for ball

Øb Ball diameter

L Solder terminal length (mounting surface side)

P

P Pitch

W Terminal width

W Bottom centre (GND) terminal length

W Bottom centre (GND) terminal width

Figure 2 – Definitions of dimensions of the flat bottom terminal types

– 12 – IEC 61188-6-2:2021 IEC 2021

a) Flat ribbon L and gull-wing terminal

b) Round or flattened (coined) terminal

c) J terminal

Side view

Bottom view

d) Rectangular or square end terminal

e) Cylindrical End Cap terminal

f) Castellated terminal

g) Inward L-shaped ribbon terminal

Side View

Bottom View

h) Flat lug terminal

– 14 – IEC 61188-6-2:2021 IEC 2021

i) Bottom terminal (with wettable flanks)

Key

A, A Terminal height of the wettable flanks

A Terminal height (thickness)

L Solder terminal length (mounting surface side)

P

P Pitch

W,W Terminal width

Figure 3 – Definitions of dimensions of the flat

bottom and vertical side terminal types

6.3 Land pattern for wave soldering

6.3.1 General

Land pattern dimensions for wave soldering should be decided according to the adaptability to

the component package construction method.

The dimensions should be adjusted as agreed upon between user and suppliers.

6.3.2 Flat bottom terminals

Land pattern for flat bottom terminals is not included in this 6.3.2 because they cannot be wave

soldered.

6.3.3 Flat bottom and vertical side terminals

Terminal types which can be soldered by wave soldering and their restrictions are shown in

Table 2.

In general, chip components (mainly “Rectangular or Square end terminal”) smaller than 1608M

and IC packages (mainly “Flat ribbon L and Gull Wing terminals” which has multiple pins per

one side) with pitches less than 1,27 mm are not recommended to be soldered by wave

soldering.

Solder joint fillet designs for wave soldering are shown in Annex B.

Table 2 – Conformity to the wave soldering of the terminal types

IEC 61191- Terminal type Typical example Restriction Conforming or

2:2017 of component not

6.3.3 Flat ribbon L and See Figure 3.a) Single pin (per side) Conforming

gull-wing terminal

Multiple pins (per side) and Non-conforming

P = < 1,0 mm

Multiple pins (per side) and Non-conforming

P >1,0 and P − W < 0,7 mm

Multiple pins (per side) and Conforming

P > 1,0 and P − W > = 0,7 mm

(e.g. SOP P = 1,27 mm)

6.3.4 Round or flattened See Figure 3.b) P > 1,0 and P − W > = 0,7 mm Conforming

(coined) terminal

6.3.5 J terminal See Figure 3.c) P > 1,0 and P − W > = 0,7 mm Conforming

6.3.6 See Figure 3.d) S < 0,7 mm Non-conforming

IEC 61191- Terminal type Typical example Restriction Conforming or

2:2017 of component not

Rectangular or S > = 0,7 mm Conforming

Square end terminal

6.3.7 Cylindrical end-cap See to Figure 3.e) S < 0,7 mm Non-conforming

terminal

S > = 0,7 mm Conforming

6.3.9 Castellated terminal See to Figure 3.f) - Non-conforming

6.3.11 Inward L-shaped See to Figure 3.g) S < 0,7 mm Non-conforming

ribbon terminal

S > = 0,7 mm Conforming

6.3.12 Flat lug terminal See to Figure 3.h) - Non-conforming

6.3.15 Bottom terminal See to Figure 3.i) - Non-conforming

(with wettable

flanks)

6.4 Land pattern for reflow soldering

6.4.1 General

Land pattern dimensions for reflow soldering are shown in 6.4.2 to 6.4.4.

The dimensions should be adjusted as agreed upon between user and suppliers.

6.4.2 Flat bottom terminals

Land pattern dimensions for Flat bottom terminals soldered by reflow soldering are shown in

Table 3.

Table 3 – Land pattern dimensions for Flat bottom terminals

soldered by reflow soldering

IEC 61191- Terminal type Land pattern dimension

2:2017

mm

J J J Rounding factor

T S H

6.3.8 bottom only chip equal to terminal dimensions 0,01

(optional: 0,05)

6.3.13 BGA equal to terminal dimensions 0.01

(optional: 0,05)

6.3.15 BTC (QFN) equal to terminal dimensions 0,01

(optional: 0,05)

6.4.3 Flat bottom and vertical side terminals

Land pattern dimensions for flat bottom and vertical side terminals to use reflow soldering class

are shown in Table 4.

– 16 – IEC 61188-6-2:2021 IEC 2021

Table 4 – Land pattern dimensions for flat bottom and vertical side terminals

soldered by reflow soldering

IEC 61191- Terminal type Land pattern dimensions

2:2017

mm

J J J

Rounding

T S H

factor

6.3.3 Flat ribbon L and gull-wing A x 100 % A x 5 % A x 150 % 0,01

5 5 5

terminal

6.3.4 Round or flattened (coined) A x 100 % A x 5 % A x 150 % 0,01

5 5 5

terminal

6.3.5 J terminal A x 100 % A x 5 % A x 150 % 0,01

5 5 5

6.3.6 Rectangular or square end A x 40 % A x 5 % A x 10 % 0,01

terminal

6.3.7 Cylindrical end-cap terminal W x 60 % 0 W x 5 % 0,01

6.3.9 Castellated terminal A x 50 % A x 5 % A x 10 % 0,01

6.3.11 Inward L-shaped ribbon A x 10 % A x 5 % A x 40 % 0,01

4 4 4

terminal

6.3.12 Flat lug terminal A x 100 % A x 5 % A x 5 % 0,01

5 5 5

6.3.15 Bottom terminal (with wettable A x 100 % 0 0 0,01

flanks)

NOTE 1 CY (courtyard excess) is specified in Annex C. Particularly since the SMD which has rectangular or

square end terminal is progressing in miniaturization, it could be adjusted to an appropriate value according to

the capacity of the mounting equipment to be used.

NOTE 2 If the rounding factor exceeds 10 % of the dimension, the rounding factor can be decreased to

0,005 mm.

where

J is the toe protrusion length, expressed in mm;

T

J is the heel protrusion length, expressed in mm;

H

J is the side protrusion length, expressed in mm;

S

W Terminal width, expressed in mm;

A SMD height (from the mounting surface to the package upper surface), expressed in mm;

A is the wettable height of the flank, expressed in mm;

A is the terminal height (thickness), expressed in mm.

6.4.4 Remarks

6.4.4.1 Solder touching component body

Solder shall not touch the body of components with flat ribbon L and gull wing terminals or seals

according to IEC 61191-2:2017. Figure 4 shows a component body touched by solder.

Land pattern designer should design J to satisfy IEC 61191-2:2017.

H

Key

J Heel protrusion length

H

L Solder terminal length (mounting surface side)

P

Figure 4 – Solder touches image

6.4.4.2 Upper limit of component tolerance

There are acceptable conditions for overhangs in IEC 61191-2:2017. In order to satisfy the

acceptance conditions of IEC 61191-2:2017, the land pattern dimensions calculated by the

method shown in this document should only be used if the following are true even if maximum

component tolerances occur. Figure 5 shows a sample of unacceptable conditions for

overhangs.

a) The dimension Z shall always be >= H .

E

This restriction applies to the following terminal types.

– flat ribbon L and gull-wing terminal;

– round or flattened (coined) terminal;

– rectangular or square end terminal;

– cylindrical end-cap terminal;

– castellated terminal;

– flat lug terminal;

– Bottom terminal (with wettable flanks).

e) The dimension X shall always be > = W .

This restriction applies to the following terminal types.

– flat lug terminal;

– bottom terminal (with wettable flanks).

– 18 – IEC 61188-6-2:2021 IEC 2021

Z < H X < W

E 1

Key

H SMD total length (including the case of maximum tolerance)

E

W Terminal width (including the case of maximum tolerance)

X Land width

Z Distance between lands. Measured from outside edges

Figure 5 – Unacceptable conditions for overhangs

Annex A

(informative)

The relation between terminal type and component packages

A.1 Flat bottom terminals

The relation between flat bottom terminal types and component packages are shown in Table

A.1.

Table A.1 – Terminal type classifications 1 – Flat bottom terminals

Terminal type Terminal type Classification Description

Component image

image

(e.g.) (e.g.)

- Transistor diode

Bottom only

Terminations

(After soldering)

Ball Grid Array

BGA

Ball Grid Array

(BGA)

(After soldering)

Bottom side

Quad Flat No-Lead

QFN

(After soldering)

BTC

(no wettable

flanks)

bottom view

(no wettable

flanks)

A.2 Flat bottom and vertical side terminals

The relation between flat bottom and vertical side terminal types and component packages are

shown in Table A.2.

– 20 – IEC 61188-6-2:2021 IEC 2021

Table A.2 – Terminal type classifications 2 – Flat bottom and vertical side terminals

Terminal type Terminal type Classification Description

Component image

image

(e.g.) (e.g.)

SOP Small Outline Package

SSOP Shrink Small Outline

Package

TSOP Thin Small Outline

Package

TSSOP Thin Shrink Small

Outline Package

SOT Small Outline Transistor

SOD Small Outline Diode

QFP Quad Flat Pack

TQFP Thin Quad Flat Pack

Flat ribbon L and

gull-wing terminal

CQFP Ceramic Quad Flat

Pack

SQFP Shrink Quad Flat Pack

TSQFP Thin Shrink Quad Flat

Pack

- Mechanical connector

- Fixed aluminium

electrolytic chip

capacitors with non-

solid electrolyte

(vertical type)

- X’tal

Round or flattened

(coined) terminal

QFJ Quad Flat Pack J-

leaded

J terminal

SOJ Small Outline J- leaded

RESC Resistor, Chip

Rectangular or

CAPC Capacitor, Chip

square end

terminal

INDC Inductor, Chip

RESMELF Fixed cylindrical chip

resistors

Cylindrical End

Cap terminal

DIOMELF Fixed cylindrical chip

diodes

- -

Castellated

terminal

Bottom view

CAPMP Capacitor, Molded

Polarized

Inward L-shaped

ribbon terminal INDM Inductor, Molded

DIOM Diode, Molded

Terminal type Terminal type Classification Description

Component image

image

(e.g.) (e.g.)

SC-79, SC-80 -

Flat lug terminal

QFN Quad Flat No-Lead

Bottom terminal

(with wettable

flanks)

(wettable

flanks)

Bottom view

TO Generic DPAK

(Complex type)

Flat lug terminal

and gull wing

terminal

– 22 – IEC 61188-6-2:2021 IEC 2021

Annex B

(informative)

Solder joint fillet designs for wave soldering

Solder joint fillet designs for wave soldering class as Level 1 (low density) defined in IEC 61188-

5 (all parts) are shown in Table B.1.

Table B.1 – Solder joint fillet design for wave soldering

Terminal type IEC 61188-5- Land pattern dimensions

1:2002 (mm)

J J J CY Rounding

T S H

(u , u ) factor

1 2

Rectangular or square

Table 6 0,55 0 0 0,5 Nearest 0,5

end terminal

Cylindrical end-cap Table 7 0,8 0,2 0,2 0,5 Nearest 0,5

terminal

Inward L-shaped ribbon Table 11 0,1 0,1 1,0 0,5 Nearest 0,5

terminal

Flat ribbon L and gull- Table 2 0,8 0,05 0,5 0,5 Nearest 0,5

wing terminal

P > 0,625 mm

Flat ribbon L and gull- Table 3 0,8 0 0,2 0,5 Nearest 0,5

wing terminal

P = < 0,625 mm

Flat Lug terminal Table 12 1,0 1,0 0 2,0 Nearest 0,5

J terminal Table 5 0,2 0,1 0,8 1,5 Nearest 0,5

Annex C

(informative)

Courtyard excess for reflow soldering

C.1 Courtyard excess for flat bottom terminals to use the land pattern for

reflow soldering

Representative examples of courtyard excess for flat bottom terminals to use the land pattern

for reflow soldering are shown in Table C.1.

Table C.1 – Courtyard excess for flat bottom terminals

to use the land pattern for reflow soldering

IEC 61191- Terminal type Classification Courtyard excess

2:2017

(e.g.) CY (mm)

6.3.8 Bottom Only Chip LGA, CGA 0,25

6.3.13 BGA BGA 1,0

6.3.15 BTC (QFN) QFN 0,25

C.2 Courtyard excess for flat bottom and vertical side terminals to use the

land pattern for reflow soldering

Representative examples of courtyard excess for flat bottom and vertical side terminals to use

reflow soldering class are shown in Table C.2.

– 24 – IEC 61188-6-2:2021 IEC 2021

Table C.2 – Courtyard excess for flat bottom and vertical side terminals

to use the land pattern for reflow soldering

IEC 61191- Terminal type Classification Courtyard excess

2:2017

(e.g.) CY mm

6.3.3 Flat ribbon L and SSOP 0,25

Gull Wing terminal

SOP

TSOP

QFP

TQFP

CQFP

SSOP

TSSOP

SQFP

TSQFP

SOT

SOD

VSSOP

6.3.4 Round or flattened - 0,25

(coined) terminal

6.3.5 J terminal QFJ 0,25

SOJ

6.3.6 Rectangular or 3216M,2012M,1608M,1005M, 0,25 (larger than 0603M)

Square end

0603M, 0,15 (0603M)

terminal

0402M 0,10 (larger than 0402M

and smaller than 0603M)

0,05 (0402M and smaller

than 0402M)

6.3.7 Cylindrical End - 0,25

Cap terminal

6.3.9 Castellated LCC 0,25

terminal

RESCAC

CAPCAC

INDCAC

OSCSC

6.3.11 Inward L-shaped CAPMP 0,25

ribbon terminal

INDM

DIOM

6.3.12 Flat Lug terminal SC-79 0,15

SC-80

SC-81

SC-85

6.3.15 Bottom terminal 0,25

(with wettable

flanks)

Bibliography

IEC 61188-5-1:2002, Printed boards and printed board assemblies – Design and use – Part 5-

1: Attachment (land/joint) considerations – Generic requirements

IEC 61188-5-2, Printed boards and printed board assemblies – Design and use – Part 5-2:

Attachment (land/joint) considerations – Discrete components

IEC 61188-5-3, Printed boards and printed board assemblies – Design and use – Part 5-3:

Attachment (land/joint) considerations – Components with gull-wing leads on two sides

IEC 61188-5-4, Printed boards and printed board assemblies – Design and use – Part 5-4:

Attachment (land/joint) considerations – Components with J leads on two sides

IEC 61188-5-5, Printed boards and printed board assemblies – Design and use – Part 5-5:

Attachment (land/joint) considerations – Components with gull-wing leads on four sides

IEC 61188-5-6, Printed boards and printed board assemblies – Design and use – Part 5-6:

Attachment (land/joint) considerations – Chip carriers with J-leads on four sides

IEC 61188-5-8, Printed board and printed board assemblies – Design and use – Part 5-8:

Attachment (land/joint) considerations – Area array components (BGA, FBGA, CGA, LGA)

IEC 61191 (all parts), Printed board assemblies

IPC-7351B, Generic Requirements for Surface Mount Design and Land Pattern Standard

_____________

– 26 – IEC 61188-6-2:2021 IEC 2021

SOMMAIRE

AVANT-PROPOS . 28

1 Domaine d’application . 30

2 Références normatives . 30

3 Termes et définitions . 30

4 Types de procédés de brasage cibles . 30

5 Détermination de la zone de report . 31

6 Exigences . 31

6.1 Exigences générales . 31

6.2 Le système de dimension de la zone de report proposé . 32

6.2.1 Conception de la zone de report . 32

6.2.2 Conception du raccord de brasage . 32

6.2.3 Excès de périmètre . 34

6.2.4 Coefficient d’arrondi . 34

6.2.5 Lien entre les classifications des bornes et la classe de la zone de

report . 34

6.2.6 Types de bornes . 34

6.3 Zone de report pour brasage tendre à la vague . 38

6.3.1 Généralités . 38

6.3.2 Bornes à partie basse plane . 38

6.3.3 Bornes à partie basse plane et face verticale . 38

6.4 Zone de report pour brasage par refusion .

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...