IEC 60194-2:2025

(Main)Electronic assembly, design and circuit boards - Vocabulary - Part 2: Common usage in electronic technologies as well as electronic assembly technologies

Electronic assembly, design and circuit boards - Vocabulary - Part 2: Common usage in electronic technologies as well as electronic assembly technologies

IEC 60194-2:2025 covers terms and definitions related to circuit board and electronic assembly technologies as well as other electronic technologies.

The terms have been classified according to the decimal classification code (DCC) and this DCC number appears just below the defined term. The DCC numbering is fully explained in Annex A.

A list of terms in alphabetical order with code number is provided in Annex B.

This edition includes the following significant technical changes with respect to the previous edition:

a) exclusion of 116 terms transferred to IEV;

b) inclusion of 9 new terms related to printed electronics and packaging technology;

c) revision of definitions of 23 terms reflecting current technology;

d) three "printed wiring" terms were removed;

e) reintroduction of identification codes for terms.

General Information

- Status

- Published

- Publication Date

- 11-Feb-2025

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 5 - TC 91/WG 5

- Current Stage

- PPUB - Publication issued

- Start Date

- 12-Feb-2025

- Completion Date

- 28-Feb-2025

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 60194-2:2025 - Electronic assembly, design and circuit boards - Vocabulary (Part 2) defines standardized terms and definitions used in circuit board, electronic assembly and related electronic technologies. The edition classifies terminology using a decimal classification code (DCC) (explained in Annex A) and provides an alphabetical term list with codes (Annex B). This 2025 revision updates vocabulary to reflect advances such as printed electronics and packaging technologies while aligning with the IEC Electropedia/IEV.

Key topics

- Structured vocabulary and classification

- Terms are grouped and assigned DCC numbers for consistent referencing across documentation and standards.

- Annex A explains the DCC scheme; Annex B lists terms in alphabetical order with codes.

- Scope of terminology

- Engineering and design for electronic packaging

- Components and materials for electronic packaging

- Fabrication and assembly processes for interconnection structures

- Types and performance of interconnecting structures and assemblies

- Quality, reliability, fabrication and assembly terms

- Notable technical changes in 2025 edition

- 116 terms transferred to the International Electrotechnical Vocabulary (IEV)

- Addition of 9 new terms related to printed electronics and packaging

- Revision of 23 definitions to reflect current technology

- Removal of three “printed wiring” terms and reintroduction of identification codes for terms

- Reference and alignment

- Developed by IEC Technical Committee 91 (Electronics assembly technology) and designed to work with IEC Electropedia and other IEC terminology resources.

Applications

IEC 60194-2:2025 is a practical resource for:

- Design engineers and PCB designers - ensure consistent terminology in specifications, schematic notes and design reviews.

- Manufacturing and assembly engineers - standardize process descriptions, work instructions and process controls.

- Quality, reliability and test engineers - use uniform definitions when creating inspection criteria, reliability reports and failure analyses.

- Standards authors, technical writers and translators - maintain precise, unambiguous language across standards, datasheets and multilingual documentation.

- Purchasing and supply-chain teams - clarify component and process requirements in procurement documents and contracts.

- Academia and training providers - teach current, industry-aligned terminology for electronics packaging and assembly.

Related standards

- IEC 60194 series (other parts under the same general title)

- IEC 60194-1:2021 (referenced for related plane terminology)

- IEC Electropedia / IEV - authoritative online terminology resource

Keywords: IEC 60194-2:2025, electronic assembly vocabulary, circuit boards terminology, DCC classification, printed electronics terminology, IEC standards, electronics packaging vocabulary.

Frequently Asked Questions

IEC 60194-2:2025 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Electronic assembly, design and circuit boards - Vocabulary - Part 2: Common usage in electronic technologies as well as electronic assembly technologies". This standard covers: IEC 60194-2:2025 covers terms and definitions related to circuit board and electronic assembly technologies as well as other electronic technologies. The terms have been classified according to the decimal classification code (DCC) and this DCC number appears just below the defined term. The DCC numbering is fully explained in Annex A. A list of terms in alphabetical order with code number is provided in Annex B. This edition includes the following significant technical changes with respect to the previous edition: a) exclusion of 116 terms transferred to IEV; b) inclusion of 9 new terms related to printed electronics and packaging technology; c) revision of definitions of 23 terms reflecting current technology; d) three "printed wiring" terms were removed; e) reintroduction of identification codes for terms.

IEC 60194-2:2025 covers terms and definitions related to circuit board and electronic assembly technologies as well as other electronic technologies. The terms have been classified according to the decimal classification code (DCC) and this DCC number appears just below the defined term. The DCC numbering is fully explained in Annex A. A list of terms in alphabetical order with code number is provided in Annex B. This edition includes the following significant technical changes with respect to the previous edition: a) exclusion of 116 terms transferred to IEV; b) inclusion of 9 new terms related to printed electronics and packaging technology; c) revision of definitions of 23 terms reflecting current technology; d) three "printed wiring" terms were removed; e) reintroduction of identification codes for terms.

IEC 60194-2:2025 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards; 31.190 - Electronic component assemblies. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60194-2:2025 has the following relationships with other standards: It is inter standard links to IEC 60194-2:2017. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60194-2:2025 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 60194-2 ®

Edition 2.0 2025-02

INTERNATIONAL

STANDARD

Electronic assembly, design and circuit boards – Vocabulary –

Part 2: Common usage in electronic technologies as well as electronic assembly

technologies

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC Products & Services Portal - products.iec.ch

The advanced search enables to find IEC publications by a Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews, graphical symbols and the glossary.

committee, …). It also gives information on projects, replaced With a subscription you will always have access to up to date

and withdrawn publications. content tailored to your needs.

IEC Just Published - webstore.iec.ch/justpublished

Electropedia - www.electropedia.org

Stay up to date on all new IEC publications. Just Published

The world's leading online dictionary on electrotechnology,

details all new publications released. Available online and once

containing more than 22 500 terminological entries in English

a month by email.

and French, with equivalent terms in 25 additional languages.

Also known as the International Electrotechnical Vocabulary

IEC Customer Service Centre - webstore.iec.ch/csc

(IEV) online.

If you wish to give us your feedback on this publication or need

further assistance, please contact the Customer Service

Centre: sales@iec.ch.

IEC 60194-2 ®

Edition 2.0 2025-02

INTERNATIONAL

STANDARD

Electronic assembly, design and circuit boards – Vocabulary –

Part 2: Common usage in electronic technologies as well as electronic

assembly technologies

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

ICS 31.180; 31.190 ISBN 978-2-8327-0159-1

– 2 – IEC 60194-2:2025 © IEC 2025

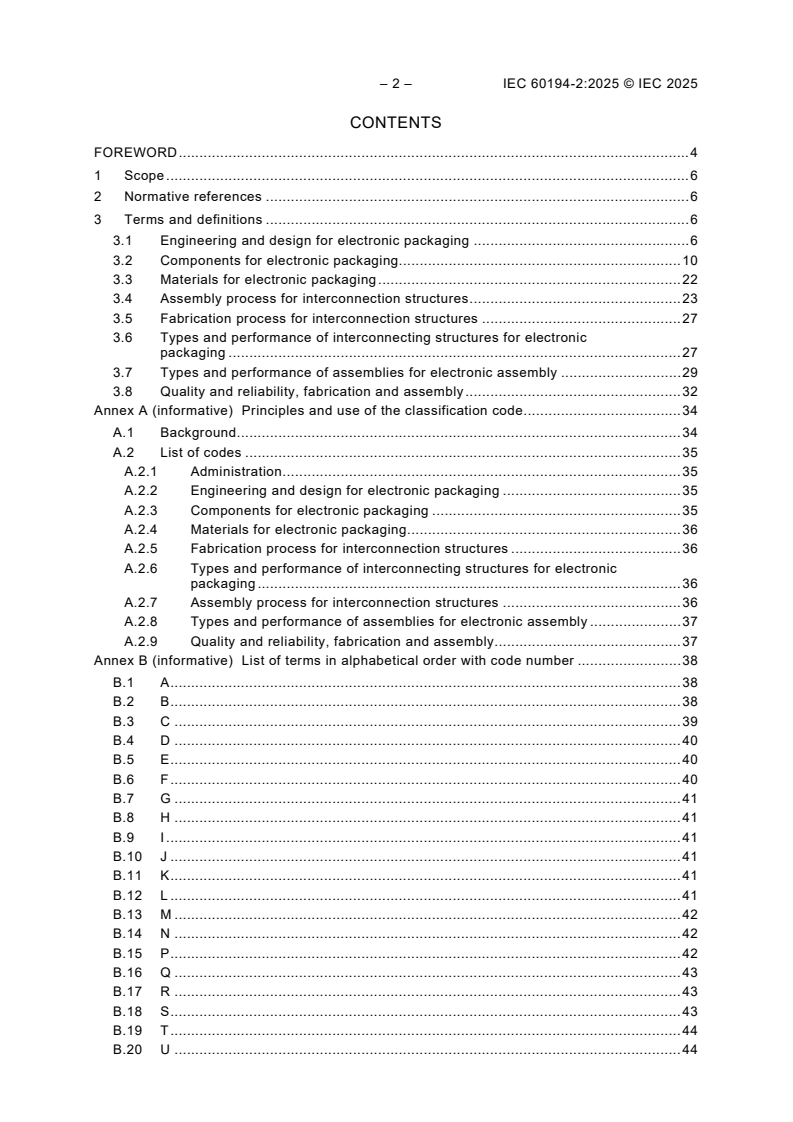

CONTENTS

FOREWORD . 4

1 Scope . 6

2 Normative references . 6

3 Terms and definitions . 6

3.1 Engineering and design for electronic packaging . 6

3.2 Components for electronic packaging. 10

3.3 Materials for electronic packaging . 22

3.4 Assembly process for interconnection structures . 23

3.5 Fabrication process for interconnection structures . 27

3.6 Types and performance of interconnecting structures for electronic

packaging . 27

3.7 Types and performance of assemblies for electronic assembly . 29

3.8 Quality and reliability, fabrication and assembly . 32

Annex A (informative) Principles and use of the classification code. 34

A.1 Background. 34

A.2 List of codes . 35

A.2.1 Administration. 35

A.2.2 Engineering and design for electronic packaging . 35

A.2.3 Components for electronic packaging . 35

A.2.4 Materials for electronic packaging . 36

A.2.5 Fabrication process for interconnection structures . 36

A.2.6 Types and performance of interconnecting structures for electronic

packaging . 36

A.2.7 Assembly process for interconnection structures . 36

A.2.8 Types and performance of assemblies for electronic assembly . 37

A.2.9 Quality and reliability, fabrication and assembly. 37

Annex B (informative) List of terms in alphabetical order with code number . 38

B.1 A . 38

B.2 B . 38

B.3 C . 39

B.4 D . 40

B.5 E . 40

B.6 F . 40

B.7 G . 41

B.8 H . 41

B.9 I . 41

B.10 J . 41

B.11 K . 41

B.12 L . 41

B.13 M . 42

B.14 N . 42

B.15 P . 42

B.16 Q . 43

B.17 R . 43

B.18 S . 43

B.19 T . 44

B.20 U . 44

B.21 V . 44

B.22 W . 44

Bibliography . 45

Figure 1 – Pin grid array . 14

Figure 2 – Passive array . 14

Figure 3 – Leaded surface-mount component – Gull wing shaped lead (Courtesy of

Aalto University) . 16

Figure 4 – Ball grid array (BGA) . 19

Figure 5 – Bumped die with inner lead . 25

Figure 6 – Flip chip . 26

Figure 7 – Chip on board (COB) . 31

– 4 – IEC 60194-2:2025 © IEC 2025

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

ELECTRONIC ASSEMBLY, DESIGN AND CIRCUIT BOARDS –

VOCABULARY –

Part 2: Common usage in electronic technologies

as well as electronic assembly technologies

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC Publication(s)”). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for

Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence between

any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) IEC draws attention to the possibility that the implementation of this document may involve the use of (a)

patent(s). IEC takes no position concerning the evidence, validity or applicability of any claimed patent rights in

respect thereof. As of the date of publication of this document, IEC had not received notice of (a) patent(s), which

may be required to implement this document. However, implementers are cautioned that this may not represent

the latest information, which may be obtained from the patent database available at https://patents.iec.ch. IEC

shall not be held responsible for identifying any or all such patent rights.

IEC 60194-2 has been prepared by IEC technical committee 91: Electronics assembly

technology. It is an International Standard.

This second edition cancels and replaces the first edition published in 2017. This edition

constitutes a technical revision.

This edition includes the following significant technical changes with respect to the previous

edition:

a) exclusion of 116 terms transferred to IEV;

b) inclusion of 9 new terms related to printed electronics and packaging technology;

c) revision of definitions of 23 terms reflecting current technology;

d) three "printed wiring" terms were removed;

e) reintroduction of identification codes for terms.

The text of this International Standard is based on the following documents:

Draft Report on voting

91/1996/FDIS 91/2014/RVD

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in

accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available

at www.iec.ch/members_experts/refdocs. The main document types developed by IEC are

described in greater detail at www.iec.ch/publications.

A list of all parts in the IEC 60194 series, published under the general title Electronic assembly,

design and circuit boards, can be found on the IEC website.

Future documents in this series will carry the new general title as cited above. Titles of existing

documents in this series will be updated at the time of the next edition.

The committee has decided that the contents of this document will remain unchanged until the

stability date indicated on the IEC website under webstore.iec.ch in the data related to the

specific document. At this date, the document will be

• reconfirmed,

• withdrawn, or

• revised.

– 6 – IEC 60194-2:2025 © IEC 2025

ELECTRONIC ASSEMBLY, DESIGN AND CIRCUIT BOARDS –

VOCABULARY –

Part 2: Common usage in electronic technologies

as well as electronic assembly technologies

1 Scope

This part of IEC 60194 covers terms and definitions related to circuit board and electronic

assembly technologies as well as other electronic technologies.

The terms have been classified according to the decimal classification code (DCC) and this

DCC number appears just below the defined term. The DCC numbering is fully explained in

Annex A.

A list of terms in alphabetical order with code number is provided in Annex B.

2 Normative references

There are no normative references in this document.

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminology databases for use in standardization at the following

addresses:

• IEC Electropedia: available at https://www.electropedia.org/

• ISO Online browsing platform: available at https://www.iso.org/obp

In order to avoid two ID numbers, the usual practice of numbering every paragraph (every term

and definition) in front of the paragraph has not been followed in this document. The official IEC

number is the number which follows the DCC and the period (e.g., 21.xxxx).

3.1 Engineering and design for electronic packaging

3.1.1

ground plane

20.1413

conductor layer, or portion thereof, that serves as a common reference for electrical circuit

returns, shielding, or heat sinking

Note 1 to entry: See also "signal plane" and "voltage plane" in IEC 60194-1:2021.

3.1.2

analogue circuit

21.0037

electrical circuit that provides a continuous relationship between its input and output

3.1.3

attenuation

21.0061

decrease of the energy of an electromagnetic wave during its propagation, represented

quantitatively by the ratio of the power flux densities at two specified points

Note 1 to entry: Attenuation is generally expressed in decibels.

[SOURCE: IEC 60050-705:1995, 705-02-05]

3.1.4

capacitive coupling

21.0174

electrical interaction between two conductors that is caused by the capacitance between them

3.1.5

characteristic impedance

21.0194

capacitive coupling quantity defined for a mode of propagation at a given frequency in a specific

uniform transmission line or uniform waveguide by one of the three following relations:

Z = SI/ || (1)

Z = /| US| (2)

Z = UI/

(3)

where

Z is the complex characteristic impedance,

S is the complex power, and

U and I are the values, usually complex, respectively of a voltage and a current

conventionally defined for each type of mode by analogy with transmission line equations.

EXAMPLE 1 For a parallel-wire transmission line, U and I can be uniquely defined, and the three equations are

consistent. If the transmission line is lossless, the characteristic impedance is real.

EXAMPLE 2 For a waveguide, the conventional definitions for U and I depend on the type of mode and generally

lead to three different values of the characteristic impedance.

EXAMPLE 3 For a circular waveguide in the dominant mode ТЕ , U = the RMS voltage along the diameter where

the magnitude of the electric field strength vector is a maximum, I = the RMS longitudinal current.

EXAMPLE 4 For a rectangular waveguide in the dominant mode TE , U = the RMS voltage between midpoints of

the two conductor faces normal to the electric field strength vector, I = the RMS longitudinal current following on one

surface normal to the electric field strength vector.

[SOURCE: IEC 60050-726:1982, 726-07-01]

3.1.6

circuit

21.0213

number of electrical elements and devices that have been interconnected to perform a desired

electrical function

– 8 – IEC 60194-2:2025 © IEC 2025

3.1.7

compensation circuit

21.0231

electrical circuit that alters the functioning of another circuit to which it is applied to achieve a

desired performance

3.1.8

crosstalk

21.0327

spurious signal

21.1006

undesirable transfer of electrical energy between neighbouring conductors (coupling) by mutual

inductance and capacitance

Note 1 to entry: See also "backward crosstalk" and "forward crosstalk".

3.1.9

digital circuit

21.0380

electrical circuit that provides two (binary) or three distinct relationships (states) between its

input and output

3.1.10

electromagnetic compatibility

EMC

21.0427

ability of equipment or a system to function satisfactorily in its electromagnetic environment

without introducing intolerable electromagnetic disturbances to anything in that environment

[SOURCE: IEC 60050-161:1990, 161-01-07]

3.1.11

electromagnetic interference

EMI

21.0431

degradation of the performance of a piece of equipment, transmission channel or system

caused by an electromagnetic disturbance

Note 1 to entry: In French, the terms "perturbation électromagnétique" and "brouillage électromagnétique"

designate respectively the cause and the effect and should not be used indiscriminately.

Note 2 to entry: In English, the terms "electromagnetic disturbance" and "electromagnetic interference" designate

respectively the cause and the effect, but they are often used indiscriminately.

[SOURCE: IEC 60050-161:1990, 161-01-06]

3.1.12

electrostatic discharge

ESD

21.1716

transfer of electric charge between bodies of different electrostatic potential in proximity or

through direct contact

[SOURCE: IEC 60050-161:1990, 161-01-22]

3.1.13

electrostatic discharge sensitive device

21.0441

device with known sensitivity or susceptibility to ESD

3.1.14

far-end crosstalk

21.0473

forward crosstalk

21.1406

noise induced into a adjacent line, as seen at the end of the adjacent line that is the farthest

from the signal source, because the adjacent line has been placed next to an active line

3.1.15

leakage current

21.0699

electric current in an unintended conductive path under normal conditions

[SOURCE: IEC 60050-161:1990, 195-05-15]

3.1.16

line coupling

21.0711

interaction between two transmission lines that is caused by their mutual inductance and

capacitance

3.1.17

load capacitance

21.0713

capacitance seen by the output of a logic circuit or other signal source

3.1.18

microwave integrated circuit

21.0762

integrated circuit that performs at microwave frequencies

3.1.19

near-end crosstalk

21.0795

backward crosstalk

21.1332

noise induced into an adjacent line, as seen at that end of the adjacent line which is closest to

the signal source, when this line has been placed near an active line

3.1.20

logic circuit

21.1005

functional digital circuit used to perform computational functions

3.1.21

conductor

22.0254

electrical path

20.0837

single conductive path in a conductive pattern

[SOURCE: IEC 60050-161:1990, 541-01-20]

3.1.22

printed contact

22.0915

element of a conductive pattern that serves as one part of a contact system

– 10 – IEC 60194-2:2025 © IEC 2025

3.1.23

signal conductor

22.0934

individual conductor that is used to transmit an impressed electrical signal

3.1.24

signal line

22.0935

conductor used to transmit a signal from one part of a circuit to another

3.1.25

conductive pattern

22.1362

configuration formed by the electrically conductive material of a circuit board

3.1.26

primary side

22.1484

side of a packaging and interconnecting structure that is defined as such on the master drawing

3.1.27

secondary side

22.1517

side of a packaging and interconnecting structure that is opposite the primary side

3.1.28

base material thickness

22.1604

thickness of the base material excluding conductive foil or material deposited on the surfaces

3.1.29

termination

22.1773

end of a conductor that connects the conductor to a terminal, distributing frame, switch or matrix

3.2 Components for electronic packaging

3.2.1

active device

30.0016

electronic component whose basic character changes while operating on an applied signal

Note 1 to entry: This includes diodes, transistors, thyristors, and integrated circuits that are used for the

rectification, amplification, switching, etc., of analogue or digital circuits in either monolithic or hybrid form.

3.2.2

add-on component

30.0019

discrete or integrated packaged or chip components that are attached to a film circuit in order

to complete the circuit's function

3.2.3

package cover

30.0053

cover that encloses the contents In the cavity of a package in the final sealing operation

3.2.4

CMOS

complementary metal oxide semiconductor

30.0221

complementary metal oxide semiconductor devices wherein N type and P type transistors are

connected together for switching

3.2.5

discrete component

30.0392

separate part of a circuit board assembly that performs a circuit function

EXAMPLE resistor, capacitor, transistor.

3.2.6

heatsink

30.0594

mechanical device that is made of a high thermal- conductivity and low specific- heat material

that dissipates heat generated by a component or assembly

3.2.7

microcircuit

30.0727

relatively high-density combination of equivalent circuit elements that are interconnected so as

to perform as an indivisible electronic circuit component

3.2.8

microelectronics

30.0759

field of science and engineering that deals with highly miniaturized electronic circuits and their

use

[SOURCE: IEC 60050-161:1990, 521-10-01]

3.2.9

monolithic integrated circuit

30.0777

integrated circuit in the form of a monolithic structure

3.2.10

package cap

30.0821

cuplike package cover

3.2.11

package lid

30.0822

flat package cover

3.2.12

perimeter sealing area

30.0844

surface on the perimeter of a package cavity that is used as an attachment to the package cover

3.2.13

semiconductor

30.1289

solid material, such as silicon, that has a resistivity that is midway between that of a conductor

and of a resistor

– 12 – IEC 60194-2:2025 © IEC 2025

3.2.14

quad flat J-lead

QFJ

30.1400

generic rectangular component package, containing an electronic device, with leads on all four

sides that are formed in a "j" shape

3.2.15

quad flat no-lead

QFN

30.1402

generic rectangular component package outline wherein the metal pad terminations are formed

on four sides of the bottom of a package

3.2.16

integrated circuit

30.1426

combination of inseparable associated circuit elements that are formed in place and

interconnected on or within a single base material to perform a particular electrical function

3.2.17

passive component

30.1468

discrete electronic device whose basic character does not change while it processes

an applied signal

3.2.18

very large scale integration

VLSI

30.1559

integrated circuits with more than 80 000 transistors on a single die that are interconnected with

conductors that are 1 μm or less in width

3.2.19

wafer level packaging

30.1564

technique of partial encapsulation and protection of die while still on the wafer and before the

wafer is divided into singulated dies

3.2.20

hermetic

30.1867

condition of sealing a component from incoming gases to a specific of inward diffusion

−6 3

cm /s

normally less than 1 × 10

3.2.21

base plane

30.2011

plane that includes the lowest point of the mounting surface of the package, except for packages

using stand-offs

3.2.22

through hole package

THP

31.0858

electronic package for pin insertion assembly type of components or devices

3.2.23

single-inline package

SIP

31.0942

component package with one straight row of pins or wire leads

3.2.24

leaded chip carrier

31.1224

chip carrier whose external connections consist of leads that are around and down the side of

the package

Note 1 to entry: See also "leadless chip carrier".

3.2.25

dual inline package

DIP

31.1387

basically, rectangular component package that has a row of leads extending from each of the

longer sides of its body that are formed at right angles to a plane and parallel to the base of its

body

3.2.26

ceramic dual inline package

CERDIP

31.1611

package that has a body of ceramic material, is hermetically sealed by a glass and that has two

parallel rows of pins

3.2.27

ceramic pin grid array

ceramic PGA

31.1612

pin grid array package (PGA) made of ceramic material, hermetically sealed by metal that has

pin-type leads in a matrix of rows and columns; terminals may be missing from some row-

column intersection

3.2.28

pin grid array

PGA

31.1965

square or rectangular component package with pins protruding from the bottom surface with a

pitch perpendicular to the plane of the package

SEE: Figure 1

– 14 – IEC 60194-2:2025 © IEC 2025

Figure 1 – Pin grid array

3.2.29

passive array

32.1295

multiple passive components of similar function mounted on the primary interconnect substrate

SEE: Figure 2

Figure 2 – Passive array

Note 1 to entry: Examples include an array of capacitors or resistors.

3.2.30

chip carrier

33.0208

low-profile, usually square, surface-mount component semiconductor package whose die cavity

or die mounting area is a large fraction of the package size and whose external connections

are usually on all four sides of the package

3.2.31

coplanar leads

33.0295

flat beam leads of a component package that have been formed so that they can simultaneously

contact one plane of a base material

3.2.32

flat pack

33.0523

rectangular component package that has a row of leads extending from each of the longer sides

of its body that are parallel to the base of its body

3.2.33

metal package

33.0579

hybrid circuit package made mainly of metal

3.2.34

leadless device

33.0694

separated part (or whole) of a wafer intended to perform a function or functions in a device

3.2.35

known tested die

KTD

33.0910

die-form semiconductor product functionally verified by probing tests equal to the expected

performance of the packaged product, without full quality assurance by supplier(s)

Note 1 to entry: The testing requirements are according to the agreement between trading partners.

3.2.36

multichip module

MCM

33.1110

module that contains two or more dice and/or minimally packaged dice

Note 1 to entry: Also see "hybrid circuit" and "multi-chip package".

3.2.37

multi-chip package

MCP

33.1112

package that contains more than one dice and/or minimally packaged dice

3.2.38

leaded surface-mount component

33.1435

surface-mount component for which external connections consist of leads that are around and

down the side of the package

SEE: Figure 3

– 16 – IEC 60194-2:2025 © IEC 2025

Key

1 Knee

2 Upper bend radius

3 Lower bend radius

4 Land

5 Heel

6 Foot

7 Toe

Figure 3 – Leaded surface-mount component –

Gull wing shaped lead (Courtesy of Aalto University)

Note 1 to entry: See also "leadless surface-mount component" in IEC 60194-1:2021.

3.2.39

leadless chip carrier

33.1435

chip carrier whose external connections consist of metallized terminations that are an integral

part of the component body

3.2.40

bipolar device

33.1573

device in which both majority and minority carriers are present

3.2.41

bonding pad

33.1585

area of metallization on an integrated circuit die that permits connection of fine wires or a

circuit element to the die

3.2.42

ceramic quad flat package

CQFP

33.1613

quad flat package (QPF) made of a ceramic material, hermetically sealed by metal, with leads

extending from all four sides

3.2.43

QFP with bumper

BQFP

33.1835

QFP package with a guarding bumper

3.2.44

quad flat pack

QFP

33.1836

generic square or rectangular component package, containing a semiconductor die, with leads

on all four sides that are formed in a "gullwing" shape

3.2.45

fine pitch QFP

33.1837

quad flat pack (QFP) package whose lead pitch centres at 0,65 mm or less

3.2.46

chip scale package

CSP

33.1838

generic term for packaging technologies that result in a packaged part that is only marginally

larger than the internal die

3.2.47

land grid array

LGA

33.1891

square package with termination lands located in a grid pattern on the bottom of the package

3.2.48

plastic ball grid array

PBGA

33.1971

polymer-based BGA

3.2.49

plastic leaded chip carrier

PLCC

33.1972

surface-mount family of integrated circuit plastic packages with leads exiting from all four sides

of the package

3.2.50

plastic quad flat pack

PQFP

33.1974

surface-mount family of integrated circuit packages, bounded on all four sides by bumpers, with

leads exiting from all four sides of the package and formed into a "gullwing" lead format

3.2.51

single chip package

SCP

33.2034

integrated circuit package containing only one semiconductor die

– 18 – IEC 60194-2:2025 © IEC 2025

3.2.52

small outline J-lead

SOJ

33.2040

generic rectangular component package, whose chip cavity or mounting area occupies a major

portion of the package area, with leads on two opposite sides that are formed in a "J" shape

3.2.53

small outline no-lead

SON

33.2050

generic rectangular component package outline wherein the metal pad terminations are formed

on two sides of the bottom of the package

3.2.54

small outline package

SOP

33.2060

generic rectangular component package, whose chip cavity or mounting area occupies a major

portion of the package area, with leads or metal pad surfaces on two opposite sides

3.2.55

system in package

SiP

33.2070

multi-chip package (MCP) that performs a system function

3.2.56

system on a chip

SoC

33.2072

active die that functions as a complete system aside from power delivery and second level

memory

Note 1 to entry: Second level memory are different forms of on-die memory additional to traditional registers and

cache/SRAM; newer memory types such as ReRAM, MRAM, hybrid D/PC-RAM or integrated HBM are possible.

3.2.57

tape carrier package

TCP

33.2077

semiconductor package that has the TAB connection and is coated with a resin

3.2.58

wafer-level package

33.2110

chip-scale package whose size is generally equal to the size of the

semiconductor device it contains and that is formed by processing on a complete wafer rather

than on an individual device

Note 1 to entry: Because of the wafer-level processing, the size of a wafer-level package may be defined by finer

dimensions and tighter tolerances than those for a similar non-wafer-level package.

Note 2 to entry: The package size will change with changes in the size of the die.

3.2.59

area array package

34.0811

package that has terminations arranged in a grid on the bottom of the package and contained

within the package outline

3.2.60

ball grid array

BGA

34.1096

surface mount package that has solder balls attached to one side of a substrate in a matrix of

rows and columns; terminals may be missing from some row-column intersections

[SOURCE: IEC 60191-6-18:2018]

SEE: Figure 4

Figure 4 – Ball grid array (BGA)

3.2.61

cupping

34.1801

condition of a ball grid array package after reflow where the corners turn up and away

from the circuit board laminate surface

Note 1 to entry: This condition in the worst case causes the balls on the outside row to be in tension and the balls

in the centre to be in compression.

Note 2 to entry: Opposite of "doming ".

3.2.62

doming

34.2011

condition of a ball grid array package after reflow where the corners turn down and

toward the circuit board laminate surface

Note 1 to entry: This condition in the worst case causes the balls on the outside row to be compressed and the balls

in the centre to be in tension.

Note 2 to entry: Opposite of "cupping ".

3.2.63

bare die

35.0111

unpackaged discrete semiconductor or integrated circuit with pads on the upper surface suitable

for interconnection to the substrate or package

– 20 – IEC 60194-2:2025 © IEC 2025

3.2.64

bond pads

35.0121

metallised areas on the die that are used for temporary or permanent electrical connection

(bonding)

3.2.65

chip

35.0205

SEE: "die".

3.2.66

dice

35.0373

more than one die

3.2.67

die

35.0375

separated part (or whole) of a wafer intended to perform a function or functions in a device

3.2.68

die device

35.0381

bare die, with or without connection structures, or a minimally packaged die

3.2.69

junction temperature

35.0666

temperature of the region of a transition between the p-type and n-type semiconductor material

in a transistor or diode element during operation

3.2.70

known good die

KGD

35.0846

die-form semiconductor product that provides assurance of equivalent quality and reliability as

that found in its conventionally packaged counterparts

3.2.71

probed die

PD

35.0912

semiconductor die evaluated by probing tests, but without quality assurance by supplier(s)

3.2.72

uncased device

35.1122

component without a package

3.2.73

wafer

35.1145

slice or a flat disc, either of semiconductor material or of such a material deposited on a

substrate, in which one or more circuits or devices can be processed

3.2.74

dicing

35.1685

separating of wafers into individual die

3.2.75

wire bond

35.2130

completed wire connection that provides electrical continuity between the die and a terminal

3.2.76

backfill

36.0075

filling a hybrid circuit package with a dry inert gas prior to hermetic sealing

3.2.77

compression seal

36.0243

tight joint made between a component package and its leads that is formed as heated metal

cools and shrinks around a glass insulator

3.2.78

support ring

36.1033

ring made of a dielectric material that is used to hold beam leads in place relative to one another

outside of a packaged device

3.2.79

J-leads

36.1752

preferred surface mount lead form used on PLCCs (plastic leaded chip carrier), so named

because the lead the lead has J shape, departs the package body near its Z-axis centreline, is

formed down then rolled under the package

Note 1 to entry: Leads so formed are shaped like the letter "J."

3.2.80

lead frame

36.1902

metallic portion of the device package on which the integrated circuit die is mounted and

connected from the die or dice bonding sites to the structure that becomes the outer leads of

the package

3.2.81

coaxial cable

37.0220

cable in the form of a central wire surrounded by a conductor tubing or sheathing that serves

as a shield and return

3.2.82

metal oxide semiconductor

MOS

39.1050

fabrication technology, resulting in the creation of FET devices

– 22 – IEC 60194-2:2025 © IEC 2025

3.2.83

passive network

39.1275

multiple passive components that have more than one function and are formed on the surface

of a separate substrate and packaged in a single SMD case

Note 1 to entry: The case is then mounted on the primary interconnected substrate of the system.

Note 2 to entry: Passive networks typically have several internal connections to form simple functions such as

terminations or filters.

3.2.84

silicon on insulator

SOI

39.1410

fabrication technology that uses an insulating material as the bulk material instead of silicon,

which may be sapphire (SOS)

Note 1 to entry: Silicon on insulator is a general term.

3.2.85

silicon on sapphire

SOS

39.1450

specific fabrication technology that uses sapphire, a variety of corundum (Al O ), as the bulk

2 3

material instead of silicon

3.3 Materials for electronic packaging

3.3.1

conductivity

40.0250

ability of a substance or material to conduct electricity

3.3.2

conductivity

40.0261

ability of a substance or material to conduct heat

3.3.3

anisotropy

40.0685

condition for a substance having differing values for properties, such as permittivity, depending

on the direction within the material

3.3.4

printed electronics sheet board

40.1276

sheet (board) of forming an electronically functional pattern and/or devices on a large-scale by

printing of conductive materials

3.3.5

base material

40.1334

insulating material upon which a conductive pattern may be formed

3.3.6

bias

44.0105

filling yarn that is off-square with the warp ends of a fabric

3.3.7

constraining core

44.0273

supporting plane that is internal to a packaging and interconnecting structure

3.3.8

creel

44.0315

device used as a yarn package rack to hold warp ends for a section beam

3.3.9

supporting plane

44.1032

planar structure that is a part of a packaging and interconnecting structure in order to provide

mechanical support, thermo-mechanical constraint, thermal conduction and/or electrical

characteristics

Note 1 to entry: It may be either internal or external to the packaging and interconnecting structure.

Note 2 to entry: See also "constraining core".

3.3.10

chemical vapour deposition

45.0202

process in which vapours and gases react chemically to produce deposits at the surface of a

substrate

[SOURCE: IEC 60050-841:2004, 841-22-07]

3.3.11

conductive ink

45.0235

conductive fluid in which chemical precursors, polymers, or particles are dissolved or dispersed

[SOURCE: IEC 62899-101:2019]

3.3.12

conductive medium

45.0261

material with a suspended powder of an electrically conductive material

Note 1 to entry: See also conductive paints, inks, pastes.

3.3.13

film conductor

45.0501

conductor formed in place on a base material by depositing a conductive material using

screening, plating or evaporating techniques

3.4 Assembly process for interconnection structures

3.4.1

bridging

70.0149

unintentional formation of a conductive path between conductors

– 24 – IEC 60194-2:2025 © IEC 2025

3.4.2

mixed component mounting technology

70.1452

component mounting technology that uses both through-hole and

surface-mounting technologies on the same packaging and interconnecting structure

3.4.3

component mounting site

70.1632

location on a packaging and interconnecting structure (P&I) that consists of a land pattern and

conductor fan-out to additional lands for testing or vias that are associated with the mounting

of a single component

3.4.4

flexible material interconnect construction

FMIC

70.1846

integration of passive and active components with mechanical components (including switches

and connectors) on a flexible or thin base material, i.e., flexible circuit board, in order to produce

an electronic assembly

3.4.5

pick-up tool

73.1759

tool used to pick up surface-mount components from a packaging medium for placement on a

substrate and which may be hand activated or a part of a pick-and-place machine

3.4.6

pick-up force

73.1760

force required to pick up a surface-mount component from its packaging medium for placement

on a substrate

3.4.7

b

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...