IEC 61188-5-6:2003

(Main)Printed boards and printed board assemblies - Design and use - Part 5-6: Attachment (land/joint) considerations - Chip carriers with J-leads on four sides

Printed boards and printed board assemblies - Design and use - Part 5-6: Attachment (land/joint) considerations - Chip carriers with J-leads on four sides

Provides information on land pattern geometries used for the surface attachment of electronic components with J leads on four sides. Provides the appropriate size, shape and tolerances of surface mount land patterns so as to ensure sufficient area for the appropriate solder fillet, and also allows for inspection, testing and reworking of resulting solder joints.

Cartes imprimées et cartes imprimées équipées - Conception et utilisation - Partie 5-6: Considérations sur les liaisons pistes-soudures - Composants à sorties en J sur quatre côtés

Donne des informations sur les géométries de zones de report utilisées pour la fixation des composants électroniques avec des sorties en J sur les quatre côtés. Fournit les dimensions, les formes et les tolérances appropriées des zones de report de montage en surface afin de garantir une surface suffisante au raccord de brasure approprié et permet également l'inspection, les essais et les retouches des joints de brasure.

General Information

- Status

- Published

- Publication Date

- 22-Jan-2003

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 12 - TC 91/WG 12

- Current Stage

- PPUB - Publication issued

- Start Date

- 23-Jan-2003

- Completion Date

- 28-Feb-2003

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 61188-5-6:2003 is an international standard published by the International Electrotechnical Commission (IEC) focusing on printed boards and printed board assemblies-specifically the design and use aspects related to component attachment. This part, Part 5-6, provides detailed guidance on attachment considerations for chip carriers with J-leads on four sides. The standard defines the geometry of land patterns used in surface mounting these components to printed circuit boards (PCBs). It specifies the appropriate size, shape, and tolerances of surface mount lands to ensure reliable solder joints that accommodate sufficient solder fillets for mechanical strength, inspection capability, testing, and ease of rework.

This standard plays a critical role in electronics assembly technology by standardizing the land pattern designs crucial for optimizing solder joint reliability and manufacturability when working with QFJ (Quad Flat J-lead) packages, both square and rectangular variants.

Key Topics

- Land Pattern Geometry: Defines the exact dimensions and layout for pads and solder joint lands to support the four-sided J-lead chip carriers.

- Component Description: Provides detailed information on the physical structure of QFJ components, including dimensions and lead form.

- Solder Joint Fillet Design: Recommends solder fillet shapes and sizes to ensure mechanical integrity and reliable electrical connection.

- Tolerance Specifications: Establishes the permissible variations in pad and joint sizes to accommodate manufacturing and assembly process capabilities.

- Inspection and Rework Considerations: Ensures land patterns allow visual inspection, testing procedures, and rework operations without compromising PCB or component integrity.

- Formats Covered: Addresses both square (QFJ square) and rectangular (QFJ rectangular) chip carrier formats.

This comprehensive approach ensures standardized, reproducible results during PCB assembly involving chip carriers with J-leads, minimizing assembly issues and enhancing product reliability.

Applications

IEC 61188-5-6:2003 is applicable across a broad range of industries including:

- Consumer Electronics: Smartphones, tablets, and wearable devices employing miniaturized chip carriers on PCBs.

- Automotive Electronics: Robust PCB assemblies requiring durable solder joints resistant to vibration and temperature changes.

- Industrial Controls: Equipment demanding high reliability and maintainability with chip carriers using J-leads.

- Telecommunications: Devices where compact, reliable surface mount assemblies are crucial.

- Medical Devices: Where precise land pattern geometry ensures reliability and safety of electronic assemblies.

Design engineers, PCB layout specialists, and manufacturing engineers use this standard to:

- Optimize PCB pad designs for improved manufacturability.

- Select appropriate component packages with standardized land dimensions.

- Establish quality control processes based on solder joint geometry.

- Facilitate international consistency in printed circuit board assembly practices.

Related Standards

IEC 61188-5-6 should be used in conjunction with other related IEC standards for printed boards and assemblies to fully cover PCB and assembly design considerations:

- IEC 61188-5-1: Provides general land pattern design principles and tables referenced in IEC 61188-5-6.

- IEC 61188 (General Series): Encompasses overall guidelines for printed board design and use, including other component attachment considerations.

- IPC Standards (e.g., IPC-7351): While not IEC standards, they complement IEC norms by offering detailed land pattern guidelines for surface mount technology.

- ISO/IEC Directives: Applied for document drafting and consistency across international standards.

Adhering to IEC 61188-5-6 helps ensure compatibility and compliance with these broader standards for PCB design, assembly, and quality assurance.

Keywords: IEC 61188-5-6, J-leads, chip carriers, surface mount land pattern, PCB design, solder joint, printed circuit board, QFJ packages, electronics assembly, land pattern geometry, solder fillet design, PCB manufacturing standards.

Frequently Asked Questions

IEC 61188-5-6:2003 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Printed boards and printed board assemblies - Design and use - Part 5-6: Attachment (land/joint) considerations - Chip carriers with J-leads on four sides". This standard covers: Provides information on land pattern geometries used for the surface attachment of electronic components with J leads on four sides. Provides the appropriate size, shape and tolerances of surface mount land patterns so as to ensure sufficient area for the appropriate solder fillet, and also allows for inspection, testing and reworking of resulting solder joints.

Provides information on land pattern geometries used for the surface attachment of electronic components with J leads on four sides. Provides the appropriate size, shape and tolerances of surface mount land patterns so as to ensure sufficient area for the appropriate solder fillet, and also allows for inspection, testing and reworking of resulting solder joints.

IEC 61188-5-6:2003 is classified under the following ICS (International Classification for Standards) categories: 31.190 - Electronic component assemblies. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61188-5-6:2003 has the following relationships with other standards: It is inter standard links to IEC 61188-6-3:2024, IEC 61188-6-2:2021. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 61188-5-6:2003 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE IEC

61188-5-6

INTERNATIONAL

Première édition

STANDARD

First edition

2003-01

Cartes imprimées et cartes imprimées équipées –

Conception et utilisation –

Partie 5-6:

Considérations sur les liaisons pistes-soudures –

Composants à sorties en J sur quatre côtés

Printed boards and printed board assemblies –

Design and use –

Part 5-6:

Attachment (land/joint) considerations –

Chip carriers with J-leads on four sides

Numéro de référence

Reference number

CEI/IEC 61188-5-6:2003

Numérotation des publications Publication numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. Ainsi, la CEI 34-1 issued with a designation in the 60000 series. For

devient la CEI 60034-1. example, IEC 34-1 is now referred to as IEC 60034-1.

Editions consolidées Consolidated editions

Les versions consolidées de certaines publications de la The IEC is now publishing consolidated versions of its

CEI incorporant les amendements sont disponibles. Par publications. For example, edition numbers 1.0, 1.1

exemple, les numéros d’édition 1.0, 1.1 et 1.2 indiquent and 1.2 refer, respectively, to the base publication,

respectivement la publication de base, la publication de the base publication incorporating amendment 1 and

base incorporant l’amendement 1, et la publication de the base publication incorporating amendments 1

base incorporant les amendements 1 et 2. and 2.

Informations supplémentaires Further information on IEC publications

sur les publications de la CEI

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. Des renseignements relatifs à the content reflects current technology. Information

cette publication, y compris sa validité, sont dispo- relating to this publication, including its validity, is

nibles dans le Catalogue des publications de la CEI available in the IEC Catalogue of publications

(voir ci-dessous) en plus des nouvelles éditions, (see below) in addition to new editions, amendments

amendements et corrigenda. Des informations sur les and corrigenda. Information on the subjects under

sujets à l’étude et l’avancement des travaux entrepris consideration and work in progress undertaken by the

par le comité d’études qui a élaboré cette publication, technical committee which has prepared this

ainsi que la liste des publications parues, sont publication, as well as the list of publications issued,

également disponibles par l’intermédiaire de: is also available from the following:

• Site web de la CEI (www.iec.ch) • IEC Web Site (www.iec.ch)

• Catalogue des publications de la CEI • Catalogue of IEC publications

Le catalogue en ligne sur le site web de la CEI The on-line catalogue on the IEC web site

(www.iec.ch/catlg-f.htm) vous permet de faire des (www.iec.ch/catlg-e.htm) enables you to search

recherches en utilisant de nombreux critères, by a variety of criteria including text searches,

comprenant des recherches textuelles, par comité technical committees and date of publication. On-

d’études ou date de publication. Des informations line information is also available on recently

en ligne sont également disponibles sur les issued publications, withdrawn and replaced

nouvelles publications, les publications rempla- publications, as well as corrigenda.

cées ou retirées, ainsi que sur les corrigenda.

• IEC Just Published

• IEC Just Published

Ce résumé des dernières publications parues

This summary of recently issued publications

(www.iec.ch/JP.htm) est aussi disponible par

(www.iec.ch/JP.htm) is also available by email.

courrier électronique. Veuillez prendre contact

Please contact the Customer Service Centre (see

avec le Service client (voir ci-dessous) pour plus

below) for further information.

d’informations.

• Service clients

• Customer Service Centre

Si vous avez des questions au sujet de cette

If you have any questions regarding this

publication ou avez besoin de renseignements

publication or need further assistance, please

supplémentaires, prenez contact avec le Service

contact the Customer Service Centre:

clients:

Email: custserv@iec.ch

Email: custserv@iec.ch

Tél: +41 22 919 02 11

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

Fax: +41 22 919 03 00

.

NORME CEI

INTERNATIONALE IEC

61188-5-6

INTERNATIONAL

Première édition

STANDARD

First edition

2003-01

Cartes imprimées et cartes imprimées équipées –

Conception et utilisation –

Partie 5-6:

Considérations sur les liaisons pistes-soudures –

Composants à sorties en J sur quatre côtés

Printed boards and printed board assemblies –

Design and use –

Part 5-6:

Attachment (land/joint) considerations –

Chip carriers with J-leads on four sides

IEC 2003 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in any

utilisée sous quelque forme que ce soit et par aucun procédé, form or by any means, electronic or mechanical, including

électronique ou mécanique, y compris la photocopie et les photocopying and microfilm, without permission in writing from

microfilms, sans l'accord écrit de l'éditeur. the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

CODE PRIX

R

Commission Electrotechnique Internationale PRICE CODE

International Electrotechnical Commission

Международная Электротехническая Комиссия

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 61188-5-6 CEI:2003

SOMMAIRE

AVANT-PROPOS . 4

INTRODUCTION .8

1 Domaine d’application et objet.10

2 Références normatives .10

3 Informations générales.12

3.1 Description générale des composants .12

3.2 Marquage .12

3.3 Format de support de boîtier .12

3.4 Prise en compte des processus.12

4 QFJ (carré) .12

4.1 Remarques introductives.12

4.2 Description des composants .12

4.3 Dimension des composants.16

4.4 Conception d’excroissance de pastille de joint brasé .16

4.5 Dimensions de la zone de report .20

5 QFJ (rectangulaire) .24

5.1 Remarques introductives.24

5.2 Description des composants .24

5.3 Dimensions des composants.26

5.4 Conception d’excroissance de pastille de joint brasé .28

5.5 Dimensions de la zone de report .32

Bibliographie .36

Figure 1 – QFJ (carré) .14

Figure 2 – Dimensions de boîtier QFJ (carré).16

Figure 3 – Conception d’excroissance de pastille de joint brasé de composant QFJ

carré ayant différents niveaux (voir Tableau 5 de la CEI 61188-5-1) .20

Figure 4 – Dimensions de la zone de report pour QFJ (carré).24

Figure 5 – QFJ (rectangulaire).24

Figure 6 – Dimensions de boîtier QFJ (rectangulaire).28

Figure 7 – Conception d’excroissance de pastille de joint brasé de composant QFJ

rectangulaire ayant différents niveaux (voir Tableau 5 de la CEI 61188-5-1) .32

Figure 8 – Dimensions de la zone de report pour QFJ (rectangulaire).34

61188-5-6 IEC:2003 – 3 –

CONTENTS

FOREWORD . 5

INTRODUCTION .9

1 Scope and object .11

2 Normative references.11

3 General information .13

3.1 General component description .13

3.2 Marking .13

3.3 Carrier packaging format .13

3.4 Process considerations.13

4 QFJ (square) .13

4.1 Introductory remark .13

4.2 Component description .13

4.3 Component dimensions .17

4.4 Solder joint fillet design .17

4.5 Land pattern dimensions.21

5 QFJ (rectangular) .25

5.1 Introductory remark .25

5.2 Component description .25

5.3 Component dimensions .27

5.4 Solder joint fillet design .29

5.5 Land pattern dimensions.33

Bibliography.37

Figure 1 – QFJ (square) .15

Figure 2 – QFJ (square) dimensions .17

Figure 3 – Solder joint fillet design of QFJ square component with different levels

(see IEC 61188-5-1, Table 5) .21

Figure 4 – QFJ (square) land pattern dimensions .25

Figure 5 – QFJ (rectangular) .25

Figure 6 – QFJ (rectangular) dimensions.29

Figure 7 – Solder joint fillet design of QFJ rectangular component with different levels

(see IEC 61188-5-1, Table 5) .33

Figure 8 – QFJ (rectangular) land pattern dimensions .35

– 4 – 61188-5-6 CEI:2003

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

____________

CARTES IMPRIMÉES ET CARTES IMPRIMÉES ÉQUIPÉES –

CONCEPTION ET UTILISATION –

Partie 5-6: Considérations sur les liaisons pistes-soudures –

Composants à sorties en J sur quatre côtés

AVANT-PROPOS

1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée

de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de

favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de

l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales.

Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le

sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en

liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation

Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés

sont représentés dans chaque comité d’études.

3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés

comme normes, spécifications techniques, rapports techniques ou guides et agréés comme tels par les Comités

nationaux.

4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de

façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes

nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale

correspondante doit être indiquée en termes clairs dans cette dernière.

5) La CEI n’a fixé aucune procédure concernant le marquage comme indication d’approbation et sa responsabilité

n’est pas engagée quand un matériel est déclaré conforme à l’une de ses normes.

6) L’attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 61188-5-6 a été établie par le comité d'études 91 de la CEI:

Techniques d’assemblage des composants électroniques.

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

91/338/FDIS 91/366/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

Cette publication a été rédigée selon les directives ISO/CEI, Partie 2

Il convient que la CEI 61188-5-6 soit lue conjointement avec la CEI 61188-5-1.

61188-5-6 IEC:2003 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

PRINTED BOARDS AND PRINTED BOARD ASSEMBLIES –

DESIGN AND USE –

Part 5-6: Attachment (land/joint) considerations –

Chip carriers with J-leads on four sides

FOREWORD

1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote

international cooperation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, the IEC publishes International Standards. Their preparation is

entrusted to technical committees; any IEC National Committee interested in the subject dealt with may

participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. The IEC collaborates closely with the International

Organization for Standardization (ISO) in accordance with conditions determined by agreement between the

two organizations.

2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an

international consensus of opinion on relevant subjects since each technical committee has representation from

all interested National Committees.

3) The documents produced have the form of recommendations for international use and are published in the form

of standards, technical specifications, technical reports or guides and they are accepted by the National

Committees in that sense.

4) In order to promote international unification, IEC National Committees undertake to apply IEC International

Standards transparently to the maximum extent possible in their national and regional standards. Any

divergence between the IEC Standard and the corresponding national or regional standard shall be clearly

indicated in the latter.

5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with one of its standards.

6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject

of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61188-5-6 has been prepared by IEC technical committee 91:

Electronics assembly technology.

The text of this standard is based on the following documents:

FDIS Report on voting

91/338/FDIS 91/366/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

IEC 61188-5-6 should be read in conjunction with IEC 61188-5-1.

– 6 – 61188-5-6 CEI:2003

La CEI 61188-5 comporte les parties suivantes sous le titre général Cartes imprimées et cartes

imprimées équipées – Conception et utilisation :

Partie 5-1: Considérations sur les liaisons pistes-soudures – Prescriptions génériques

Partie 5-2: Considérations sur les liaisons pistes-soudures – Composants discrets

Partie 5-3: Considérations sur les liaisons pistes-soudures – Composants à sorties en aile de

mouette sur deux côtés

Partie 5-4: Considérations sur les liaisons pistes-soudures – Composants à sorties en J sur

deux côtés

Partie 5-5: Considérations sur les liaisons pistes-soudures – Composants à sorties en aile de

mouette sur quatre côtés

Partie 5-6: Considérations sur les liaisons pistes-soudures – Composants à sorties en J sur

quatre côtés

Partie 5-7: Considérations sur les liaisons pistes-soudures – Composants (DIP) à broches sur

deux côtés

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant 2004. A cette

date, la publication sera

• reconduite;

• supprimée;

• remplacée par une édition révisée, ou

• amendée.

___________

La plupart de ces parties sont encore à publier.

61188-5-6 IEC:2003 – 7 –

IEC 61188-5 consists of the following parts, under the general title Printed boards and printed

board assemblies – Design and use :

Part 5-1: Attachment (land/joint) considerations – Generic requirements

Part 5-2: Attachment (land/joint) considerations – Discrete components

Part 5-3: Attachment (land/joint) considerations – Gull-wing leads, two sides

Part 5-4: Attachment (land/joint) considerations – J leads, two sides

Part 5-5: Attachment (land/joint) considerations – Gull-wing leads, four sides

Part 5-6: Attachment (land/joint) considerations – Chip carriers with J-leads on four sides

Part 5-7: Attachment (land/joint) considerations – Post (DIP) leads, two sides

The committee has decided that the contents of this publication will remain unchanged

until 2004. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

———————

At the time of writing, most of these parts are still to be published.

– 8 – 61188-5-6 CEI:2003

INTRODUCTION

La présente partie de la CEI 61188 concerne les zones de report pour les composants avec

des sorties en J sur les quatre côtés. Chaque article donne des informations selon le schéma

qui suit:

Les dimensions des zones de report proposées dans cette norme sont basées sur les calculs

fondamentaux de tolérance associés aux zones de protubérance de soudure et aux excédents

de périmètre (voir la CEI 61188-5-1). Ce périmètre recouvre tout ce qui concerne les besoins

de fabrication normaux.

Les dimensions fixées des zones de report concernées dans la présente norme sont

généralement applicables pour l'application de la pâte de brasage ainsi que du processus de

soudage par refusion. Pour l'application du processus de brasage à la vague, les dimensions

des zones de report doivent être modifiées, il est préférable d'avoir une orientation parallèle à

la direction de la vague et des dispositifs d'échantillonnage de soudage convenablement

dimensionnés doivent être ajoutés.

Cette spécification présente un triple dimensionnement des zones de report (niveaux 1, 2 et 3)

sur la base de trois types de zones de protubérances et d'excédents de périmètre maximal

(max.) moyen et minimal (min.). A chaque zone de report a été assigné un identifiant pour

indiquer les caractéristiques de la robustesse spécifique des zones de report. Les utilisateurs

ont également la possibilité d'organiser les informations de façon à ce qu'elles s'adaptent le

mieux possible à leur utilisation spécifique.

La présente norme considère que les dimensions de la pastille sont toujours plus grandes que

les sorties du composant ou que leurs dimensions. Si un utilisateur a des raisons valables

d'utiliser l’épargne de brasure pour limiter le mouillage sur une puce ou pour utiliser des

pastilles de taille inférieure aux sorties du composant ou pour appliquer des concepts

différents de ceux de la CEI 61188-5-1, cette norme ne sera pas applicable.

Il est de la responsabilité de l'utilisateur de vérifier les zones de report des composants pour

montage en surface (CMS) utilisés pour mener à bien un processus de montage convenable

comportant les essais et une fiabilité assurée pour l'utilisation en conditions perturbées du

produit.

Les dimensions de composants données dans cette norme correspondent à ceux qui sont

disponibles sur le marché, et ne doivent être considérées qu’en tant que références.

61188-5-6 IEC:2003 – 9 –

INTRODUCTION

This part of IEC 61188 covers land patterns for components with J leads on four sides. Each

clause contains information in accordance with the following format:

The proposed land pattern dimensions in this standard are based upon the fundamental

tolerance calculation combined with the given land protrusions and courtyard excesses (see

IEC 61188-5-1). The courtyard covers all issues pertaining to normal manufacturing needs.

The land pattern dimensions covered in this standard are generally applicable for reflowed

solder paste processes. For immersion soldering processes (e.g. wave, jet, drag soldering),

lands may have to be modified to prevent shadowing and shorting (e.g. by extending land

length parallel to the direction of motion of the board and/or provision of solder thieves).

This specification offers a threefold land pattern dimensioning (levels 1, 2, and 3) on the basis

of a threefold set of land protrusions and courtyard excesses maximum (max.), median

(mdn.), and minimum (min.). Each land pattern has been assigned an identification number to

indicate the characteristics of the specific robustness of the land patterns. Users also have

the opportunity to organize the information to suit their particular design.

This standard assumes that land dimensions are always larger than component termination or

lead outlines. If a user has good reason to use solder resist to limit wetting on a land, or to

use lands smaller than component terminations, or to apply a concept different from that of

IEC 61188-5-1, this standard may not apply.

It is the responsibility of the user to verify the surface mounting devices (SMD) land patterns

used for achieving an undisturbed mounting process, including testing, and an ensured

reliability for the product stress conditions when in use.

Dimensions of the components listed in this standard are those available on the market, and

are for reference purposes only.

– 10 – 61188-5-6 CEI:2003

CARTES IMPRIMÉES ET CARTES IMPRIMÉES EQUIPÉES –

CONCEPTION ET UTILISATION

Partie 5-6: Considérations sur les liaisons pistes-soudures –

Composants à sorties en J sur quatre côtés

1 Domaine d’application et objet

La présente partie de la CEI 61188 donne des informations sur les géométries de zones de

report utilisées pour la fixation des composants électroniques avec des sorties en J sur les

quatre côtés.

Cette norme a pour but de fournir les dimensions, les formes et les tolérances appropriées des

zones de report de montage en surface afin de garantir une surface suffisante au raccord de

brasure approprié et de permettre également l’inspection, les essais et les retouches des

joints de brasure.

Chaque article comporte une série spécifique de critères détaillés relatifs aux composants, aux

dimensions des composants, à la conception du joint de brasure ainsi qu’aux dimensions de la

zone de report.

NOTE L’acronyme QFJ est l’appellation conventionnelle utilisée au Japon ; l’acronyme PLCC est l’appellation

conventionnelle utilisée aux Etats-Unis pour ces composants.

2 Références normatives

Les documents de référence suivants sont indispensables pour l'application du présent

document. Pour les références datées, seule l'édition citée s'applique. Pour les références non

datées, la dernière édition du document de référence s'applique (y compris les éventuels

amendements).

CEI 60068-2-58, Essais d'environnement – Partie 2-58: Essais – Essai Td – Méthodes d'essai

de la soudabilité, de la résistance de la métallisation à la dissolution et de la résistance à la

chaleur de soudage des composants pour montage en surface

CEI 60191-2, Normalisation mécanique des dispositifs à semi-conducteurs – Partie 2:

Dimensions

CEI 61188-5-1, Cartes imprimées et cartes imprimées équipées – Conception et utilisation –

Partie 5-1: Considérations sur les liaisons pistes-soudures – Prescriptions génériques

CEI 61760-1, Technique du montage en surface – Partie 1: Méthode de normalisation pour la

spécification des composants montés en surface (CMS)

61188-5-6 IEC:2003 – 11 –

PRINTED BOARDS AND PRINTED BOARD ASSEMBLIES –

DESIGN AND USE –

Part 5-6: Attachment (land/joint) considerations –

Chip carriers with J-leads on four sides

1 Scope and object

This part of IEC 61188 provides information on land pattern geometries used for the surface

attachment of electronic components with J leads on four sides.

The object of this standard is to provide the appropriate size, shape and tolerances of surface

mount land patterns so as to ensure sufficient area for the appropriate solder fillet, and also

allow for inspection, testing and reworking of resulting solder joints.

Each clause contains a specific set of criteria, setting out details on the component, the

component dimensions, the solder joint design and the land pattern dimensions.

NOTE The acronym QFJ is the naming convention used by Japan; the acronym PLCC is the naming convention

used by the USA for these components.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 60068-2-58, Environmental testing – Part 2-58: Tests – Test Td: Test methods for

solderability, resistance to dissolution of metallization and soldering heat of surface mounting

devices (SMD)

IEC 60191-2, Mechanical standardisation of semiconductor devices – Part 2: Dimensions

IEC 61188-5-1, Printed boards and printed board assemblies – Design and use – Part 5-1:

Attachment (land/joint) considerations – Generic requirements

IEC 61760-1, Surface mounting technology – Part 1: Standard method for the specification of

surface mounting components (SMDs)

– 12 – 61188-5-6 CEI:2003

3 Informations générales

3.1 Description générale des composants

Les composants sont constitués par les boîtiers de porte-puce à sorties en J dont les sorties

s’étendent par delà les encombrements de boîtier. La forme des boîtiers peut être soit carrée

soit rectangulaire. Ces bornes fournissent généralement des espaces pour le corps du boîtier

par rapport à l’encapsulation et à la structure d’interconnexion pour des raisons liées au

dégagement, au contrôle ou à la disposition des différences de dilatation thermique.

Dans les porte-puce à sorties en plastique, la distinction d’encapsulation primaire concerne le

point dans lequel une puce est incorporée dans le boîtier. Un boîtier pré-moulé est fourni en

tant que corps à sorties avec une cavité ouverte pour la fixation des puces. Une partie du

corps post-moulé possède généralement une puce fixée à une grille de connexion avec un

corps en plastique isolant moulé autour de l’assemblage.

3.2 Marquage

Les familles de produits QFJ (carrée ou rectangulaire) sont généralement marquées

conformément au marquage propre du fabricant. Y figurent le nom du fabricant ou son logo

ainsi que l’indication de la broche 1. Certains produits peuvent comporter l’indication de la

broche sur le boîtier au lieu du marquage de la broche 1. Des marquages supplémentaires

peuvent comporter la date-code du lot de fabrication et/ou la localisation de la fabrication.

3.3 Format de support de boîtier

Le support des boîtiers peut être en barrettes mais le support en bande est préférable pour

une meilleure manipulation et pour des utilisations à grand volume. Le support en plateau n’est

pas acceptable à cause de la coplanéité des broches requise pour le placement et la brasure.

3.4 Prise en compte des processus

Les boîtiers QFJ sont normalement traités par opération de brasage par fusion (voir la CEI

60068-2-58).

Les dispositifs à pas fins et à sorties nombreuses peuvent nécessiter un traitement spécial

hors de la localisation normale de la duite et des opérations en fabrication de fusion.

4 QFJ (carré)

4.1 Remarques introductives

Cet article indique les dimensions du composant et de la zone de report pour les composants à

boîtiers QFJ carrés. La construction de base est également traitée. Les Figures 2 et 3

fournissent une liste de tolérances et de dimensions prévues pour les joints de brasure

utilisées pour obtenir les dimensions des zones de report.

4.2 Description des composants

Les QFJ sont utilisés dans de nombreuses applications pour l’électronique commerciale,

industrielle ou militaire.

4.2.1 Construction de base

Voir Figure 1.

61188-5-6 IEC:2003 – 13 –

3 General information

3.1 General component description

The component consists of quad flat J-lead packages with terminations, which extend beyond

the package outlines. The shape of the packages can be either square or rectangular. These

terminations typically separate the body of the package from the packaging and interconnect

structure (P&IS) for reasons of clearing, inspecting or accommodating differences in thermal

expansion.

In plastic leaded chip carriers, the primary packaging distinction concerns the point at which a

chip is incorporated into the package. A pre-molded package is supplied as a leaded body

with an open cavity for chip attachment. A post-molded body part typically has the chip

attached to a lead frame with an insulating plastic body molded around the assembly.

3.2 Marking

The QFJ (square and rectangular) families of parts are generally marked with the

manufacturer’s part numbers, name or symbol, and a pin 1 indicator. Some parts may have a

pin 1 feature in the case shape instead of a pin 1 marking. Additional markings may include

date-code manufacturing lot and/or manufacturing location.

3.3 Carrier packaging format

The carrier packaging format may be provided in tubes but embossed carrier taping is

preferred for best handling and high volume applications. Bulk packaging is not acceptable

because of lead coplanarity required for placement and soldering.

3.4 Process considerations

QFJ packages are normally processed by reflow solder operations (see IEC 60068-2-58).

High lead-count fine pitch parts may require special processing outside the normal pick/place

and reflow manufacturing operations.

4 QFJ (square)

4.1 Introductory remark

This clause provides the component and land pattern dimensions for square QFJ (quad flat J-

lead) components. Basic construction is also covered. Figures 2 and 3 provide a listing of the

tolerances and target solder joint dimensions used to arrive at the land pattern dimensions.

4.2 Component description

QFJs are widely used in variety of applications for commercial, industrial or military

electronics.

4.2.1 Basic construction

See Figure 1.

– 14 – 61188-5-6 CEI:2003

IEC 3270/02

Figure 1 – QFJ (carré)

Les porte-puce QFJ sont utilisés lorsqu’un scellement hermétique n’est pas prescrit. D’autres

contraintes comprennent une plage de températures limitée (généralement 0 °C ou 70 °C) et

une protection environnementale nominale. L’avantage du QFJ réside dans son coût faible

comparé aux boîtiers en céramique.

4.2.2 Matériaux de sortie

La coplanéité à extrémité de sortie élevée dans les porte-puce à sorties pour montage en

surface est un facteur important pour la fiabilité des fixations brasées à la carte imprimée.

La planéité peut être mesurée à partir des trois sorties les plus faibles d’un boîtier à sorties.

La coplanéité de 0,1 mm au maximum est recommandée avec toutefois, une préférence pour

0,05 mm.

Le porte-puce en plastique pré-moulé a été conçu pour être connecté au substrat P et l

(structure d’assemblage et d’interconnexion) au moyen d’une douille. La pression de ressort

sur les deux côtés du boîtier est destinée à contraindre le mouvement, et également tenir

compte du voilement de substrat jusqu’à 0,5 %. Une fixation brasée au substrat P et l est

également possible. La conception est également destinée à utiliser la technique de

l’encapsulant en silicone pour la protection et le revêtement de puce.

Le porte-puce à sorties en plastique pré-moulé et post-moulé est composé d’un ensemble

diélectrique en métal composite qui inclut une grille de connexion à conducteur et un corps

isolant moulé. Dans les deux types de porte-puce en plastique, toutes les opérations

nécessaires de métallisation sont réalisées par le fabricant de boîtiers pour éliminer l’étamage

et la métallisation de la part de l’utilisateur.

4.2.3 Marquage

Tous les dispositifs doivent porter le marquage d’un numéro de modèle et de l’emplacement de

la «Broche 1». L’emplacement de la «Broche 1» peut être moulé dans le corps en plastique ou

marquée à l’aide d’encre.

4.2.4 Format de support de boîtier

Le support des boîtiers pour les boîtiers plats peut être en barrettes, mais dans la plupart des

cas les boîtiers plats sont fournis sur support en bande.

4.2.5 Prise en compte des processus

Il convient que les dispositifs soient en mesure de résister aux dix cycles par l’intermédiaire

d’un système de refusion normalisé fonctionnant à 235 °C. Chaque cycle doit consister en une

exposition à 235 °C pendant 60 s. Les dispositifs doivent aussi être capables de résister au

minimum à 10 s d’immersion dans la brasure fondue à 260 °C. Les composants doivent

satisfaire aux exigences de la CEI 61760-1.

61188-5-6 IEC:2003 – 15 –

IEC 3270/02

Figure 1 – QFJ (square)

QFJs (quad flat J-lead packages) are employed where a hermetic seal is not required. Other

constraints include a limited temperature range (typically 0 °C or 70 °C) and nominal

environmental protection. QFJs have the advantage of low cost as compared to ceramic

packages.

4.2.2 Termination materials

High lead-end coplanarity in surface mounted lead chip carriers is an important factor in

reliable solder attachment to the printed board. Planarity may be measured from the lowest

three leads of a leaded package. Coplanarity of 0,1 mm maximum is recommended with a

preference for 0,05 mm.

The pre-molded plastic chip carrier was designed to be connected to the packaging and

interconnection (P&l) substrate by means of a socket. Spring pressure on both sides of the

package is intended to constrain movement as well as allow for substrate warpage as high as

0,5 %. Solder attach to the P&l substrate is also possible. The design is also intended to

make use of silicone encapsulate technology for chip coverage and protection.

The pre- and post-molded plastic leaded chip carrier is composed of a composite

metal/dielectric assembly that includes a conductor lead frame and a molded insulating body.

In both types of plastic chip carriers, all necessary plating operations are performed by the

package manufacturer to eliminate tinning or plating by the user.

4.2.3 Marking

All parts shall be marked with a part number and “Pin 1” location. The “Pin 1” location may be

molded into the plastic body or marked with ink.

4.2.4 Carrier package format

The carrier package format for flat packs may be provided in tubes but, in most instances, flat

packs are delivered in embossed taping.

4.2.5 Process considerations

Parts should be capable of withstanding ten cycles through a standard reflow system

operating at 235 °C. Each cycle shall consist of a 60 s exposure at 235 °C. Parts must also be

capable of withstanding a minimum of 10 s immersion in molten solder at 260 °C. The

components shall meet the requirements of IEC 61760-1.

– 16 – 61188-5-6 CEI:2003

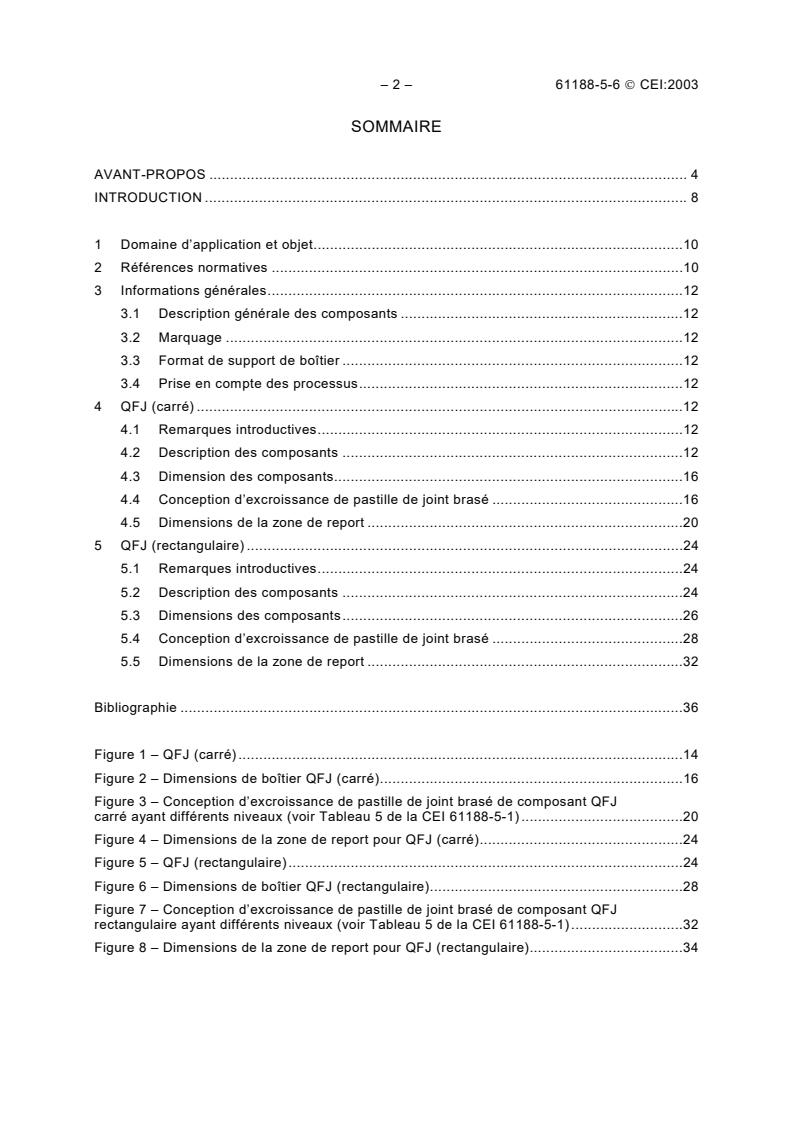

4.3 Dimensions des composants

Les Figures 2 et 4 fournissent les dimensions des composants QFJ (carré).

H

A

S J L

P

B

W

T

L

IEC 3271/02

Dimensions en millimètres

LW T A B JHP

Identificateur

de

Réfé- De base

composant Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Max.

rence

QFJ – 20 9,60 10,21 0,33 0,58 1,20 1,74 8,71 9,22 8,71 9,22 7,87 4,57 1,27

QFJ – 28 12,14 12,75 0,33 0,58 1,20 1,74 11,25 11,76 11,25 11,76 10,41 4,57 1,27

QFJ – 44 17,22 17,83 0,33 0,58 1,20 1,74 16,33 16,84 16,33 16,84 15,49 4,57 1,27

QFJ – 52 19,76 20,37 0,33 0,58 1,20 1,74 18,87 19,38 18,87 19,38 18,03 5,08 1,27

QFJ – 68 24,84 25,45 0,33 0,58 1,20 1,74 23,95 24,51 23,95 24,51 23,11 5,08 1,27

QFJ – 84 29,92 30,53 0,33 0,58 1,20 1,74 29,03 29,59 29,03 29,59 28,19 5,08 1,27

QFJ – 100 35,00 35,61 0,33 0,58 1,20 1,74 34,11 34,67 34,11 34,67 33,27 5,08 1,27

QFJ – 124 42,62 43,23 0,33 0,58 1,20 1,74 41,73 42,29 41,73 42,29 40,89 5,08 1,27

Figure 2 – Dimensions de boîtier QFJ (carré)

4.4 Conception d’excroissance de pastille de joint brasé

La Figure 3 donne les dimensions et la forme du raccord de brasure après l’opération de

brasure. Les dimensions minimales, médianes et maximales de chaque raccord du bout,

de talon et latérales sont déterminées par la prise en considération de la fiabilité du joint de

brasure et la qualité ainsi que par la productivité pendant le montage des dispositifs. La

conception des zones de report nécessite la prise en compte de trois facteurs de précision:

la précision des dimensions des dispositifs (C), la précision du montage des dispositifs sur les

circuits imprimés (P) et la précision des dimensions des puces sur les circuits imprimés (F) en

plus des dimensions des raccords. La formule nécessaire pour obtenir la tolérance résultant de

ces facteurs est la suivante:

a) Effet sur la conception pour une brasure sans auto-alignement (niveau 1):

Dans le processus de brasure à la vague, il n’y a pas d’effet d’auto-alignement. De ce fait

la formule ne peut pas être simplifiée mais reste identique comme indiqué ci-après:

2 2 2

Z = L + 2 J + T T = F + P + C

L1 L1 L

max min H max H H

61188-5-6 IEC:2003 – 17 –

4.3 Component dimensions

Figures 2 to 4 provide the component dimensions for QFJ (square) components.

H

A

S J L

P

B

W

T

L

IEC 3271/02

Dimensions in millimetres

LW T A B J H P

Component

identifier

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Ref Max. Basic

9,60 10,21 0,33 0,58 1,20 1,74 8,71 9,22 8,71 9,22 7,87 4,57 1,27

QFJ-20

QFJ-28 12,14 12,75 0,33 0,58 1,20 1,74 11,25 11,76 11,25 11,76 10,41 4,57 1,27

QFJ-44 17,22 17,83 0,33 0,58 1,20 1,74 16,33 16,84 16,33 16,84 15,49 4,57 1,27

QFJ-52 19,76 20,37 0,33 0,58 1,20 1,74 18,87 19,38 18,87 19,38 18,03 5,08 1,27

QFJ-68 24,84 25,45 0,33 0,58 1,20 1,74 23,95 24,51 23,95 24,51 23,11 5,08 1,27

QFJ-84 29,92 30,53 0,33 0,58 1,20 1,74 29,03 29,59 29,03 29,59 28,19 5,08 1,27

QFJ-100 35,00 35,61 0,33 0,58 1,20 1,74 34,11 34,67 34,11 34,67 33,27 5,08 1,27

QFJ-124 42,62 43,23 0,33 0,58 1,20 1,74 41,73 42,29 41,73 42,29 40,89 5,08 1,27

Figure 2 – QFJ (square) dimensions

4.4 Solder joint fillet design

Figure 3 shows the shape and dimensions of the solder fillet after the soldering process. The

minimum, median, and maximum dimensions of each of toe, heel, and side fillet are

determined by taking into consideration solder joint reliability, and also quality and

productivity in the parts mounting process. Designing land patterns requires consideration of

three factors concerning accuracy: part dimension accuracy (C), part mount accuracy on

PWBs (P) and land shape accuracy on PWBs (F), in addition to fillet dimensions. The

formulae to obtain the tolerance resulted from these factors are as follows:

a) Design consideration when soldered without self-alignment effect (level 1):

In the flow soldering process, there is no self-alignment effect. Thus, the formulae cannot

be simplified but remain the same as follows:

2 2 2

Z = L + 2 J + T T = F + P + C

L1 L1 L

max min H max H H

– 18 – 61188-5-6 CEI:2003

2 2 2

G = S (rms) – 2 J – T T = F + P + C

L1 L1 S

min max T max T T

2 2 2

X = W + 2 J + T T = F + P + C

L1 L1 W

max min S max S S

b) Effet sur la conception pour une brasure sans auto-alignement (niveau 2):

2 2 2

Z = L + 2 J + T T = F + P + C

L2 L2 L

max min H mdn H H

2 2 2

G = S (rms) – 2 J – T T = F + P + C

L2 L2 S

min max T mdn T T

2 2 2

X = W + 2 J + T T = F + P + C

L2 L2 W

max min S mdn S S

c) Effet sur la conception pour une brasure avec auto-alignement (niveau 3):

2 2 2

Z = L + 2 J + T T = F + P + C

max min H min H H L3 L3 L

2 2 2

G = S (rms) – 2 J – T T = F + P + C

min max T mi

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...