IEC 61163-2:1998

(Main)Reliability stress screening - Part 2: Electronic components

Reliability stress screening - Part 2: Electronic components

Provides guidance on reliability stress screening techniques and procedures for electronic components. Is intended for use of a) component manufacturers as a guideline, b) component users as a guideline to negotiate with component manufacturers on stress screening requirements or plan a stress screening process in house due to reliability requirements, c) subcontractors who provide stress screening as a service.

Déverminage sous contraintes - Partie 2: Composants électroniques

Est un guide pour les techniques et procédures du déverminage sous contraintes des composants électroniques. Est destiné à être utilisé par a) les fabricants de composants, comme guide, b) les utilisateurs de composants, comme guide pour négocier avec les fabricants de composants les conditions de déverminage sous contraintes ou planifier en interne un processus de déverminage sous contraintes pour satisfaire aux exigences de fiabilité, c) les sous-traitants qui proposent le déverminage sous contraintes comme service.

General Information

- Status

- Published

- Publication Date

- 26-Nov-1998

- Technical Committee

- TC 56 - Dependability

- Drafting Committee

- MT 12 - TC 56/MT 12

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 11-Mar-2020

- Completion Date

- 13-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 61163-2:1998, titled Reliability Stress Screening – Part 2: Electronic Components, is an international standard published by the International Electrotechnical Commission (IEC). The document provides comprehensive guidance on the techniques and procedures essential for conducting reliability stress screening (RSS) on electronic components. Developed by IEC Technical Committee 56 on Dependability, this standard targets component manufacturers, users, and subcontractors involved in stress screening activities to ensure enhanced reliability and quality of electronic components.

RSS serves as a critical methodology to identify latent defects and manufacturing faults, thereby helping achieve near-zero defect levels in new products. While traditionally used for systems operating under extreme environmental conditions, RSS has become a mainstream quality assurance practice in electronic component manufacturing and usage.

Key Topics

This standard covers key aspects of the reliability stress screening process, including but not limited to:

Scope and Definitions

Clarifies the applicability of RSS for electronic components and introduces essential terminology aligned with IEC vocabularies such as IEC 60050.Procedure for Stress Screening

Outlines step-by-step processes including:- Program definition and planning

- Establishing communication between stakeholders

- Identification of potential failure modes and defects

- Selection of appropriate stress types, levels, and sequencing designed to precipitate failures

- Determining the duration and conditions of stress application

- Mathematical analysis of test data and failure trends

- Failure mode analysis to refine processes

- Implementation of corrective action loops

- Criteria for acceptance or rejection of components

- Feedback mechanisms to component manufacturers for continuous improvement

Failure Mechanism Identification Tools

Annex A provides informative examples of tools used to analyze failure mechanisms in components.Data Analysis Techniques

Annex B discusses methods for interpreting test data acquired during RSS to draw meaningful reliability conclusions.Application Examples

Annex C illustrates practical implementations of reliability stress screening processes in various electronic component use cases.

Applications

IEC 61163-2 is invaluable for several practical scenarios:

Component Manufacturers:

Use as a guideline to design and implement stress screening procedures that detect defects early, ensure tighter quality control, and improve product reliability before market release.Component Users (OEMs and System Integrators):

Leverage the standard to negotiate stress screening requirements with suppliers or to establish in-house RSS processes aligned with system reliability goals. This helps mitigate risks associated with component failures in critical applications such as aerospace, automotive, telecommunications, and defense electronics.Third-Party Subcontractors:

Adopt this standard to provide reliability stress screening as a service compliant with international norms, ensuring credibility and quality assurance for client components.

The standard emphasizes that RSS should not be seen as a substitute for sound manufacturing controls-it is more effective as a complementary tool for improving system-level reliability and screening out weaker components. It also highlights logistics considerations for maintaining consistent component supply with similar stress screening treatments over a system’s lifetime.

Related Standards

For comprehensive understanding and implementation of IEC 61163-2, the following related IEC standards are recommended:

- IEC 60050 – International Electrotechnical Vocabulary (provides definitions and terminology pertinent to electrical and electronic engineering).

- IEC 60027 – Letter Symbols to be Used in Electrical Technology (for standard graphical and letter symbols).

- IEC 60417 – Graphical Symbols for Use on Equipment (consistent symbols for equipment markings).

- IEC 60617 – Graphical Symbols for Diagrams (used in circuit diagrams and documentation).

- Other Reliability and Dependability Standards by IEC Technical Committee 56, which covers broader dependability topics including testing and evaluation methodologies for electronic components and systems.

Keywords: IEC 61163-2, reliability stress screening, electronic components, IEC standard, component manufacturers, failure mode analysis, stress screening procedure, quality assurance, dependability, electronic device reliability, IEC 60050, stress testing, corrective action process, defect detection.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

Bureau Veritas

Bureau Veritas is a world leader in laboratory testing, inspection and certification services.

DNV

DNV is an independent assurance and risk management provider.

Sponsored listings

Frequently Asked Questions

IEC 61163-2:1998 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Reliability stress screening - Part 2: Electronic components". This standard covers: Provides guidance on reliability stress screening techniques and procedures for electronic components. Is intended for use of a) component manufacturers as a guideline, b) component users as a guideline to negotiate with component manufacturers on stress screening requirements or plan a stress screening process in house due to reliability requirements, c) subcontractors who provide stress screening as a service.

Provides guidance on reliability stress screening techniques and procedures for electronic components. Is intended for use of a) component manufacturers as a guideline, b) component users as a guideline to negotiate with component manufacturers on stress screening requirements or plan a stress screening process in house due to reliability requirements, c) subcontractors who provide stress screening as a service.

IEC 61163-2:1998 is classified under the following ICS (International Classification for Standards) categories: 03.120.01 - Quality in general; 31.020 - Electronic components in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61163-2:1998 has the following relationships with other standards: It is inter standard links to IEC 60300-3-7:1999, IEC 61163-2:2020. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 61163-2:1998 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME

CEI

INTERNATIONALE

IEC

61163-2

INTERNATIONAL

Première édition

STANDARD

First edition

1998-11

Déverminage sous contraintes –

Partie 2:

Composants électroniques

Reliability stress screening –

Part 2:

Electronic components

Numéro de référence

Reference number

CEI/IEC 61163-2:1998

Numéros des publications Numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. issued with a designation in the 60000 series.

Publications consolidées Consolidated publications

Les versions consolidées de certaines publications de Consolidated versions of some IEC publications

la CEI incorporant les amendements sont disponibles. including amendments are available. For example,

Par exemple, les numéros d’édition 1.0, 1.1 et 1.2 edition numbers 1.0, 1.1 and 1.2 refer, respectively, to

indiquent respectivement la publication de base, la the base publication, the base publication

publication de base incorporant l’amendement 1, et la incorporating amendment 1 and the base publication

publication de base incorporant les amendements 1 incorporating amendments 1 and 2.

et 2.

Validité de la présente publication Validity of this publication

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept under

constamment revu par la CEI afin qu'il reflète l'état constant review by the IEC, thus ensuring that the

actuel de la technique. content reflects current technology.

Des renseignements relatifs à la date de Information relating to the date of the reconfirmation of

reconfirmation de la publication sont disponibles dans the publication is available in the IEC catalogue.

le Catalogue de la CEI.

Les renseignements relatifs à des questions à l’étude et Information on the subjects under consideration and

des travaux en cours entrepris par le comité technique work in progress undertaken by the technical

qui a établi cette publication, ainsi que la liste des committee which has prepared this publication, as well

publications établies, se trouvent dans les documents ci- as the list of publications issued, is to be found at the

dessous: following IEC sources:

• «Site web» de la CEI* • IEC web site*

• Catalogue des publications de la CEI • Catalogue of IEC publications

Publié annuellement et mis à jour régulièrement Published yearly with regular updates

(Catalogue en ligne)* (On-line catalogue)*

• Bulletin de la CEI • IEC Bulletin

Disponible à la fois au «site web» de la CEI* et Available both at the IEC web site* and as a

comme périodique imprimé printed periodical

Terminologie, symboles graphiques Terminology, graphical and letter

et littéraux symbols

En ce qui concerne la terminologie générale, le lecteur For general terminology, readers are referred to

se reportera à la CEI 60050: Vocabulaire Electro- IEC 60050: International Electrotechnical Vocabulary

technique International (VEI). (IEV).

Pour les symboles graphiques, les symboles littéraux For graphical symbols, and letter symbols and signs

et les signes d'usage général approuvés par la CEI, le approved by the IEC for general use, readers are

lecteur consultera la CEI 60027: Symboles littéraux à referred to publications IEC 60027: Letter symbols to

utiliser en électrotechnique, la CEI 60417: Symboles be used in electrical technology, IEC 60417: Graphical

graphiques utilisables sur le matériel. Index, relevé et symbols for use on equipment. Index, survey and

compilation des feuilles individuelles, et la CEI 60617: compilation of the single sheets and IEC 60617:

Symboles graphiques pour schémas. Graphical symbols for diagrams.

* Voir adresse «site web» sur la page de titre. * See web site address on title page.

NORME

CEI

INTERNATIONALE

IEC

61163-2

INTERNATIONAL

Première édition

STANDARD

First edition

1998-11

Déverminage sous contraintes –

Partie 2:

Composants électroniques

Reliability stress screening –

Part 2:

Electronic components

IEC 1998 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in

utilisée sous quelque forme que ce soit et par aucun any form or by any means, electronic or mechanical,

procédé, électronique ou mécanique, y compris la photo- including photocopying and microfilm, without permission in

copie et les microfilms, sans l'accord écrit de l'éditeur. writing from the publisher.

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland

Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http: //www.iec.ch

CODE PRIX

Commission Electrotechnique Internationale

PRICE CODE V

International Electrotechnical Commission

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 61163-2 © CEI:1998

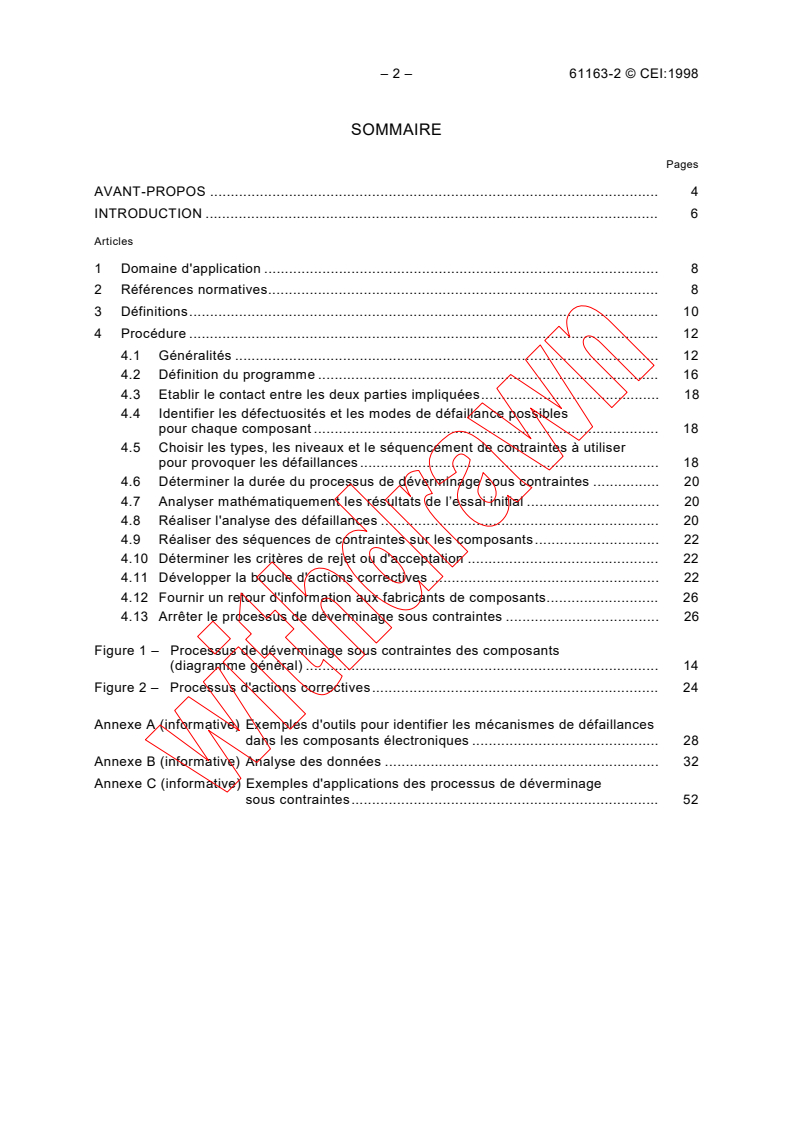

SOMMAIRE

Pages

AVANT-PROPOS . 4

INTRODUCTION . 6

Articles

1 Domaine d'application. 8

2 Références normatives. 8

3 Définitions. 10

4 Procédure. 12

4.1 Généralités. 12

4.2 Définition du programme . 16

4.3 Etablir le contact entre les deux parties impliquées. 18

4.4 Identifier les défectuosités et les modes de défaillance possibles

pour chaque composant . 18

4.5 Choisir les types, les niveaux et le séquencement de contraintes à utiliser

pour provoquer les défaillances . 18

4.6 Déterminer la durée du processus de déverminage sous contraintes . 20

4.7 Analyser mathématiquement les résultats de l’essai initial . 20

4.8 Réaliser l'analyse des défaillances . 20

4.9 Réaliser des séquences de contraintes sur les composants. 22

4.10 Déterminer les critères de rejet ou d'acceptation . 22

4.11 Développer la boucle d'actions correctives . 22

4.12 Fournir un retour d'information aux fabricants de composants. 26

4.13 Arrêter le processus de déverminage sous contraintes . 26

Figure 1 – Processus de déverminage sous contraintes des composants

(diagramme général) . 14

Figure 2 – Processus d'actions correctives. 24

Annexe A (informative) Exemples d'outils pour identifier les mécanismes de défaillances

dans les composants électroniques . 28

Annexe B (informative) Analyse des données . 32

Annexe C (informative) Exemples d'applications des processus de déverminage

sous contraintes. 52

61163-2 © IEC:1998 – 3 –

CONTENTS

Page

FOREWORD . 5

INTRODUCTION . 7

Clause

1 Scope. 9

2 Normative references. 9

3 Definitions. 11

4 Procedure. 13

4.1 General. 13

4.2 Programme definition. 17

4.3 Establish contact between the two parties involved . 19

4.4 Identify the possible flaws and failure modes for each component. 19

4.5 Select stress types, stress levels and stress sequence to be used in

order to precipitate failures. 19

4.6 Determine the duration of the reliability stress screening process . 21

4.7 Mathematically analyze initial test results. 21

4.8 Perform failure analysis. 21

4.9 Perform stress sequence on the components . 23

4.10 Determine approval or rejection criteria . 23

4.11 Develop closed-loop corrective action process. 23

4.12 Provide feedback to the component manufacturers. 27

4.13 Discontinue the reliability stress screening process . 27

Figure 1 – Component reliability screening process (general flow chart) . 15

Figure 2 – Corrective action process . 25

Annex A (informative) Examples of tools for identifying failure mechanisms

in electronic components . 29

Annex B (informative) Data analysis. 33

Annex C (informative) Examples of applications of reliability stress screening processes. 53

– 4 – 61163-2 © CEI:1998

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

___________

DÉVERMINAGE SOUS CONTRAINTES –

Partie 2: Composants électroniques

AVANT-PROPOS

1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée

de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de

favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de

l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales.

Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le

sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en

liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation

Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés

sont représentés dans chaque comité d’études.

3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés

comme normes, rapports techniques ou guides et agréés comme tels par les Comités nationaux.

4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de

façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes

nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale

correspondante doit être indiquée en termes clairs dans cette dernière.

5) La CEI n’a fixé aucune procédure concernant le marquage comme indication d’approbation et sa responsabilité

n’est pas engagée quand un matériel est déclaré conforme à l’une de ses normes.

6) L’attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 61163-2 a été établie par le comité d’études 56 de la CEI: Sûreté

de fonctionnement.

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

56/636/FDIS 56/642/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

Les annexes A, B et C sont données uniquement à titre d’information.

61163-2 © IEC:1998 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

RELIABILITY STRESS SCREENING –

Part 2: Electronic components

FOREWORD

1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, the IEC publishes International Standards. Their preparation is

entrusted to technical committees; any IEC National Committee interested in the subject dealt with may

participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization

for Standardization (ISO) in accordance with conditions determined by agreement between the two

organizations.

2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has representation

from all interested National Committees.

3) The documents produced have the form of recommendations for international use and are published in the form

of standards, technical reports or guides and they are accepted by the National Committees in that sense.

4) In order to promote international unification, IEC National Committees undertake to apply IEC International

Standards transparently to the maximum extent possible in their national and regional standards. Any

divergence between the IEC Standard and the corresponding national or regional standard shall be clearly

indicated in the latter.

5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with one of its standards.

6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject

of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61163-2 has been prepared by IEC technical committee 56:

Dependability.

The text of this standard is based on the following documents:

FDIS Report on voting

56/636/FDIS 56/642/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

Annexes A, B and C are for information only.

– 6 – 61163-2 © CEI:1998

INTRODUCTON

Bien que développé initialement comme outil d'obtention de la fiabilité pour des systèmes

fonctionnant dans des conditions d'environnement sévères, le déverminage sous contraintes a

émergé, dans la profession des fabricants de matériel électronique, comme étant une

technique permettant d'atteindre le niveau de zéro défaut pour les nouveaux produits.

Le déverminage sous contraintes a prouvé qu'il était un outil efficace pour

a) identifier et éliminer les défectuosités dues à une mauvaise conception des composants et

à des problèmes de fabrication,

b) trier les composants pour les amener à un niveau de fiabilité plus élevé que les valeurs

publiées,

c) fournir des informations permettant l’adaptation des processus dans des limites très

serrées pour minimiser la variabilité des paramètres.

Il convient de ne pas considérer le déverminage sous contraintes comme un moyen normal

pour obtenir la fiabilité des composants électroniques, parce qu'il ne peut pas améliorer la

fiabilité individuelle de chaque composant. Par contre, il peut améliorer la fiabilité d'un

système. Le coût et les risques, associés au fait que les contraintes appliquées peuvent

dégrader la durée de vie des composants, dépassent en général les bénéfices potentiels. Il est

plus avantageux de renforcer le contrôle des procédés de fabrication. Cependant, cette

méthode peut ne pas être pratique, par exemple lorsqu’il existe des composants dont la

fiabilité est plus faible que la fiabilité acceptable. Utiliser le déverminage sous contraintes pour

améliorer les caractéristiques de composants peut également poser un problème de logistique,

lorsque des composants similaires à ceux déverminés ne sont pas disponibles à une date

ultérieure.

Lorsque des composants ont été déverminés sous contraintes pour être utilisés dans un

système particulier, soit la quantité de composants nécessaire à la réparation, pour toute la

durée de vie du système, est déverminée dès le début du programme, soit l'utilisateur s'assure

que la documentation du système est suffisante pour contrôler l'approvisionnement en

composants de telle sorte que tous les composants de remplacement sont déverminés de

façon similaire.

61163-2 © IEC:1998 – 7 –

INTRODUCTION

Although first developed as a tool for designing reliability into systems that operate in harsh

environmental conditions, reliability stress screening has emerged as a technique in the

electrotechnical manufacturing community that is useful if the drive toward zero defect levels in

new products is to continue.

Reliability stress screening has proved to be an effective tool in

a) identifying and removing flaws due to poor component design and manufacturing

deficiencies,

b) screening parts to a tighter specification than those published,

c) providing feedback to enable the streamlining of processes to achieve very tight limits in

order to minimize parameter variability.

Reliability stress screening should not be considered as a normal procedure to be used in

assuring the reliability of electronic components because reliability stress screening cannot

improve the reliability of an individual component. Reliability stress screening can, however,

improve the actual reliability of a system. The cost and risks generally outweigh the potential

benefits since any applied stress may have detrimental effects on the lifetime of the

components. Greater benefits may be obtainable by tighter manufacturing process control.

However, in some cases, this may not be practical, for example with existing components with

less than acceptable reliability. Using reliability stress screening to upgrade component

specifications can also lead to a logistical problem, when similarly screened components are

not available at a later date.

When performing reliability stress screening on components for use in a particular system,

either enough components needed for the repair of the system over its entire service life need

to be screened initially or the user needs to ensure that system documentation be sufficient to

control component procurement so that all replacement components be similarly screened.

– 8 – 61163-2 © CEI:1998

DÉVERMINAGE SOUS CONTRAINTES –

Partie 2: Composants électroniques

1 Domaine d'application

La présente partie de la CEI 61163, incluant les annexes, est un guide pour les techniques et

procédures du déverminage sous contraintes des composants électroniques. Cette norme n’est

pas et ne peut pas être exhaustive en raison de la rapidité des développements dans l’industrie

électronique.

Cette norme est destinée à être utilisée par

a) les fabricants de composants, comme guide,

b) les utilisateurs de composants, comme guide pour négocier avec les fabricants de

composants les conditions de déverminage sous contraintes ou planifier en interne un

processus de déverminage sous contraintes pour satisfaire aux exigences de fiabilité,

c) les sous-traitants qui proposent le déverminage sous contraintes comme service.

Cette norme n'a pas pour but de fournir des plans d'essai pour tester des composants

électroniques spécifiques ou pour délivrer des certificats de conformité pour des lots de

composants.

2 Références normatives

Les documents normatifs suivants contiennent des dispositions qui, par suite de la référence

qui y est faite, constituent des dispositions valables pour la présente partie de la CEI 61163.

Au moment de la publication, les éditions indiquées étaient en vigueur. Tout document normatif

est sujet à révision et les parties prenantes aux accords fondés sur la présente partie de la

CEI 61163 sont invitées à rechercher la possibilité d'appliquer les éditions les plus récentes

des documents normatifs indiqués ci-après. Les membres de la CEI et de l'ISO possèdent le

registre des Normes internationales en vigueur.

CEI 60050(191):1990, Vocabulaire Electrotechnique International (VEI) – Chapitre 191: Sûreté

de fonctionnement et qualité de service

CEI 60300-1:1993, Gestion de la sûreté de fonctionnement – Partie 1: Gestion du programme

de sûreté de fonctionnement

CEI 60300-2:1995, Gestion de la sûreté de fonctionnement – Partie 2: Eléments et tâches du

programme de sûreté de fonctionnement

CEI 60300-3-7—, Gestion de la sûreté de fonctionnement – Partie 3-7: Guide d'application –

1)

Déverminage sous contraintes du matériel électronique

CEI 61163-1:1995, Déverminage sous contraintes – Partie 1: Entités réparables fabriquées en

lots

CEI 61709:1996, Composants électroniques – Fiabilité – Conditions de référence pour les taux

de défaillance et modèles d'influence des contraintes pour la conversion

___________

1)

A publier.

61163-2 © IEC:1998 – 9 –

RELIABILITY STRESS SCREENING –

Part 2: Electronic components

1 Scope

This part of IEC 61163 provides guidance on reliability stress screening techniques and

procedures for electronic components. This standard is not, and cannot be, exhaustive due to

the rapid rate of developments in the electronics industry.

This standard is intended for the use of

a) component manufacturers as a guideline,

b) component users as a guideline to negotiate with component manufacturers on stress

screening requirements or plan a stress screening process in house due to reliability

requirements,

c) subcontractors who provide stress screening as a service.

This standard is not intended to provide test plans for specific electronic components or for

delivery of certificates of conformance for batches of components.

2 Normative references

The following normative documents contain provisions which, through reference in this text,

constitute provisions of this part of IEC 61163. At the time of publication, the editions indicated

were valid. All normative documents are subject to revision, and parties to agreements based

on this part of IEC 61163 are encouraged to investigate the possibility of applying the most

recent editions of the normative documents indicated below. Members of IEC and ISO maintain

registers of currently valid International Standards.

IEC 60050(191):1990, International Electrotechnical Vocabulary (IEV) – Chapter 191:

Dependability and quality of service

IEC 60300-1:1993, Dependability management – Part 1: Dependability programme management

IEC 60300-2:1995, Dependability management Part 2: Dependability programme elements and

tasks

IEC 60300-3-7:—, Dependability management – Part 3-7: Application guide – Reliability stress

1)

screening of electronic hardware

IEC 61163-1:1995, Reliability stress screening – Part 1: Repairable items manufactured in lots

IEC 61709:1996, Electronic components – Reliability – Reference conditions for failure rates

and stress models for conversion

__________

1)

To be published.

– 10 – 61163-2 © CEI:1998

3 Définitions

Pour les besoins de la présente partie de la CEI 61163, les définitions suivantes, ainsi que

celles données dans la CEI 60050(191) et la CEI 60300-3-7 s'appliquent.

3.1

déverminage

procédé utilisé pour détecter les défectuosités, supprimer et réparer les éléments fragiles pour

atteindre le plus rapidement possible le niveau de fiabilité attendu en période de durée de vie

utile

NOTE 1 – La CEI 60050(191) définit, en 191-17-02, le terme «rodage». Ce terme, toutefois, est employé par

beaucoup de fabricants pour décrire l'essai appelé «soak-test», qui désigne seulement l'une des multiples façons

d'éliminer les éléments faibles. De plus, «rodage» peut inclure la notion de vieillissement dont le but est de

stabiliser les paramètres, sans que des défaillances n'apparaissent.

NOTE 2 – La CEI 60050(191) définit, en 191-14-09, le terme «essai de sélection». Ce terme, toutefois, a un sens

trop large pour être applicable dans le présent contexte, puisqu'il englobe l'élimination de tous les types de défauts.

De plus, le déverminage sous contraintes est une opération de fabrication et non un essai.

NOTE 3 – La réparation n'est pas applicable dans le cas de composants électroniques.

3.2

déverminage sous contraintes

procédé utilisant des contraintes d'environnement et/ou de fonctionnement comme moyens de

détecter les défectuosités, en les transformant en défaillances détectables

NOTE – Par sa conception, le déverminage sous contraintes a pour but de transformer les défectuosités en

défaillances détectables. Un traitement de vieillissement conçu spécifiquement dans le but de stabiliser les

caractéristiques n'est pas un procédé de déverminage sous contraintes et sort donc du domaine d'application de

cette norme.

3.3

entité fragile

entité dont la probabilité de défaillance est élevée dans la période de défaillance précoce par

suite de la présence d'une défectuosité (voir également 3.8: période de défaillance précoce)

3.4

fragilité

toute imperfection (connue ou non) dans une entité, pouvant provoquer une ou plusieurs

défaillances par fragilité

NOTE 1 – On admet que chaque type de fragilité est statistiquement indépendant des autres.

NOTE 2 – Une fragilité peut être soit intrinsèque, soit induite.

3.5

défaillance par fragilité

défaillance due à une fragilité de l'entité elle-même, lorsqu'elle est soumise à des contraintes

restant dans les limites fixées [VEI 191-04-06]

3.6

défectuosité

fragilité dans une entité qui provoque des défaillances par fragilité précoces

3.7

défectuosité intrinsèque

défectuosité dans une entité liée à sa constitution technologique et au processus de fabrication

61163-2 © IEC:1998 – 11 –

3 Definitions

For the purpose of this part of IEC 61163, the following definitions as well as those given in

IEC 60050(191) and IEC 60300-3-7 apply:

3.1

reliability screening (process)

a process of detection of flaws and removal and repair of weak items for the purpose of

reaching as rapidly as possible the reliability level expected during the useful life

NOTE 1 – IEC 60050(191) defines in 191-17-02, the term "burn-in". This term, however, is used by many

manufacturers to describe a so-called ‘soak-test’, which is only one of many possible ways of screening.

Furthermore ‘burn-in’ may include ageing, the purpose of which is to stabilize parameters, and where in many cases

no failures occur.

NOTE 2 – IEC 60050(191) defines, in 191-14-09, the term "screening test". This term, however, is defined too

broadly to be applicable in the present context because it encompasses screening of any types of non-conformities.

Furthermore, reliability screening is a process, not a test.

NOTE 3 – Repair is not applicable in the case of electronic components.

3.2

reliability stress screening (process)

a process using environmental and/or operational stress as a means of detecting flaws by

precipitating them as detectable failures

NOTE – Reliability screening is designed with the intention of precipitating flaws into detectable failures. An ageing

process designed specifically with the intention of stabilizing parameters is not a reliability stress screening process

and is therefore outside the scope of this standard.

3.3

weak item

an item which has a high probability of failure in the early failure period due to a flaw (see also

3.8: early failure period)

3.4

weakness

any imperfection (known or unknown) in an item, capable of causing one or more weakness

failures

NOTE 1 – Each type of weakness is assumed to be statistically independent of all other such types.

NOTE 2 – A weakness may be either inherent or induced.

3.5

weakness failure

a failure due to a weakness in the item itself when subjected to stresses within the stated

capabilities of the item [IEV 191-04-06]

3.6

flaw

a weakness in an item which gives rise to early weakness failures

3.7

inherent flaw

a flaw in an item related to its technology and manufacturing process

– 12 – 61163-2 © CEI:1998

3.8

période de défaillance précoce

période initiale éventuelle dans la vie d’une entité, commençant à un instant spécifié et

pendant laquelle l’intensité instantanée de défaillance, pour une entité réparée, ou le taux

instantané de défaillance, pour une entité non réparée, est beaucoup plus grand que pendant

la période suivante [VEI 191-10-07]

NOTE – La période de défaillance précoce est la période de défaillance des entités fragiles.

4 Procédure

4.1 Généralités

Pour définir un programme de déverminage sous contraintes, il est important de comprendre

ce à quoi ce programme est destiné, à savoir:

a) améliorer la capabilité des procédés en comprenant et en éliminant les causes de

défaillances;

b) obtenir des performances plus resserrées pour les composants déverminés, compara-

tivement aux valeurs publiées;

c) comprendre et améliorer la fiabilité des nouvelles technologies de composants;

d) éliminer les composants faibles sujets à des défaillances précoces.

Il est important de noter qu'il existe deux types de défaillances:

– défaillances dépendantes du temps; les mécanismes qui provoquent ces défaillances sont

fonction de contraintes et provoqueront, avec le temps, une dégradation du composant.

Il convient que les techniques utilisées pour accélérer ces défaillances n'affectent pas les

bons composants;

– défaillances non dépendantes du temps; ces mécanismes de défaillances sont dus à des

défauts latents qui n'affectent pas les composants en temps normal à moins qu'ils ne soient

initialisés par des événements extérieurs. Il convient de choisir avec soin les techniques

utilisées pour accélérer ces défaillances. Sans cela, il y a un risque d'endommager les

bons composants, si le déverminage sous contraintes est trop sévère.

Dans tous les cas ci-dessus, le déverminage sous contraintes sera au début exécuté à 100 %

et ensuite graduellement diminué pour finalement être supprimé après qu'une analyse des

défaillances a été réalisée et que les actions correctives ont été menées.

61163-2 © IEC:1998 – 13 –

3.8

early failure period

that early period, if any, in the lifetime of an item, beginning at a given instant of time

and during which the instantaneous failure intensity for a repaired item or the instantaneous

failure rate for a non-repaired item is considerably higher than that of the subsequent period

[IEV 191-10-07]

NOTE – The early failure period is the period where the weak items fail.

4 Procedure

4.1 General

In designing a stress programme, it is important to understand the purpose of the programme

as to whether it is:

a) to improve the process capability by understanding and eliminating causes of failures;

b) to achieve tighter performance on screened devices compared to published specifications;

c) to understand and improve reliability of new device technologies;

d) to remove weak devices which may fail early.

It is important to note that there are two types of failures:

– time-dependent failures; the mechanisms that cause these failures are stress-dependent

and will cause degradation of the device given sufficient time. The techniques used to

accelerate these failure mechanisms should not affect good devices;

– time-independent failures; these failure mechanisms are due to latent flaws that do not

affect devices in normal operation unless induced by some external events. Care should be

taken when choosing the techniques used to accelerate these failures since damage to

good components is possible if the screen is too harsh.

In all the above cases, the screening will start at 100 %, gradually reduce and finally be

eliminated after analysis of failures is made and follow-up actions are taken.

– 14 – 61163-2 © CEI:1998

Composant considéré

Déverminage initial

Non

Nombre et type

Action corrective du fabricant

de défaillances

acceptables ?

Oui

Déverminage/100 %

échantillonnage

Non

Nombre de

défaillances acceptables

après déverminage ?

Oui

Rejet ou

Expédition

déverminage permanent

IEC 1 512/98

Figure 1 – Processus de déverminage sous contraintes des composants

(diagramme général)

61163-2 © IEC:1998 – 15 –

Component of interest

Initial screening

No

Number and type

Corrective action at manufacturer

of failures acceptable ?

Yes

Screening/100 %

sample of production lots

No

Number of failures

acceptable after

screening ?

Yes

Reject or

Shipping to users

continuous screening

IEC 1 512/98

Figure 1 – Component reliability screening process

(general flow chart)

– 16 – 61163-2 © CEI:1998

Il est très important que le but du déverminage sous contraintes soit analysé avec soin. Il

convient qu’aucune procédure de déverminage sous contraintes ne soit faite d'une manière

routinière. Il devra y avoir une raison précise pour que le déverminage sous contraintes soit

choisi (par exemple des raisons économiques).

Pour obtenir les meilleurs résultats possibles d'un déverminage sous contraintes, il est

nécessaire de bien comprendre les mécanismes de défaillance des composants à déverminer

et comment l'application des contraintes affectent ces mécanismes. Il convient que le plus

grand soin soit pris pour que seules les défaillances susceptibles d'apparaître en utilisation en

clientèle soient accélérées, étant donné qu'il est facile d'induire des défaillances qui ne

risquent pas de se produire par une mauvaise application des contraintes de déverminage.

Il convient qu’un essai fonctionnel de chaque composant à déverminer soit réalisé avant et

après l'application de tout déverminage sous contraintes. Premièrement, l’essai est réalisé

pour que les composants défaillants puissent être attribués au seul déverminage sous

contraintes. Deuxièmement, le déverminage sous contraintes est appliqué à chaque

composant pendant la durée spécifiée et dans les conditions spécifiées. Troisièmement, les

composants sont essayés fonctionnellement de nouveau pour éliminer les composants

défectueux de la production déclarée bonne.

L’essai fonctionnel peut ne pas être suffisant pour des composants qui sont particulièrement

fragiles ou coûteux, tels que les lasers. Dans ce cas, un essai paramétrique peut s'avérer

nécessaire.

Le déverminage sous contraintes réalisé de cette façon peut être utilisé pour déterminer

l'efficacité du déverminage sous contraintes appliqué au lot de composants donné. Les

données obtenues peuvent être comparées aux données obtenues sans application de

déverminage sous contraintes. Ces deux types de données peuvent être aussi comparés au

rendement au niveau système, voire enfin aux résultats obtenus en exploitation. Tout cela est

fait pour contrôler l'efficacité du déverminage sous contraintes.

Pour utiliser correctement le déverminage sous contraintes des composants électroniques, il

convient de bien comprendre le type de la ou des défaillances prévues. Ce n'est qu'après cela

qu’il est recommandé de planifier les détails du programme de déverminage, y compris le type

de contrainte, ainsi que son niveau et sa durée.

La méthodologie du déverminage sous contraintes ne peut être décrite en détail dès lors

qu'elle concerne beaucoup de composants différents. Par conséquent, il n'est pas judicieux de

décrire de manière exhaustive les procédures de déverminage sous contraintes pour des types

de composants particuliers. Cependant, une procédure générale peut être recommandée pour

concevoir un plan de déverminage sous contraintes spécifique (voir 4.2). Il est important de

remarquer que toutes les étapes d'une telle procédure n'ont pas forcément besoin d'être

utilisées dans la conception de chaque plan de déverminage sous contraintes.

4.2 Définition du programme

La procédure décrite ci-après est recommandée pour définir et mettre en place un procédé de

déverminage sous contraintes:

• établir le contact entre les deux parties impliquées

• identifier les défectuosités et les modes de défaillance possibles pour chaque composant

• choisir les types, les niveaux et le séquencement des contraintes à utiliser pour provoquer

les défaillances

• déterminer la durée du processus de déverminage sous contraintes

• analyser mathématiquement les résultats de l’essai initial

• analyser les défaillances

• réaliser les séquences de contraintes sur les composants

• déterminer les critères de rejet ou d'acceptation

• développer la boucle d'actions correctives

• fournir un retour d'informations aux fabricants de composants

• arrêter le processus de déverminage sous contraintes

61163-2 © IEC:1998 – 17 –

It is important that the aim for a reliability stress screening be carefully considered. No

reliability stress screening procedure should be used routinely. There is to be a clear reason

why reliability stress screening is chosen (for example economic reasons).

In order to get the best possible results from a stress screen, it is necessary to fully understand

the failure mechanisms of the components to be screened and how the application of any

particular screen will affect these mechanisms. Care should be taken so that only the failure

mechanisms likely to occur while the component is operating in the field are accelerated by the

screen, since it is relatively easy to induce unlikely failure mechanisms by misapplication of

screening stress.

Before and after any screen is applied, functional testing of each part to be screened should be

performed. Firstly, this testing is done so that only those parts that fail as a result of the stress

screen should be recorded as failing for that reason. Secondly, the stress screen is applied

to every component for the specified period of time and under the specified conditions. Thirdly,

every component is tested functionally again, in order to remove any failed parts from the good

product population.

Functional testing may not be sufficient for components which are particularly delicate or

costly, such as lasers. In these cases, a parametric test may be necessary.

The reliability stress screening performed in this manner can be used to determine the yield of

the screen for the lot of components screened. This screen yield data may be compared to

data for yield without screen application and both these types of data may be compared in turn

to system yield data, and ultimately to system field return data, all in order that the

effectiveness of the screen may be monitored.

In order to use reliability stress screening of electronic components effectively, the type of

failure(s) expected should be understood. Then the details of the stress screen programme,

including stress levels and screen durations, should be planned.

The reliability stress screening methodology cannot be described in detail since there are many

different component types. Therefore, it is not advisable to comprehensively list reliability

screening procedures for particular component types. A general procedure, however, can be

recommended for designing a specific reliability stress screening plan (see 4.2). It is important

to note that all the steps of such a procedure need not be used in designing every reliability

stress screening plan.

4.2 Programme definition

The following procedure for setting up and running a reliability stress screening process is

recommended:

• establish contact between the two parties involved

• identify the possible flaws and failure modes for each component

• select stress types, stress levels and stress sequence to be used

in order to precipitate failures

• determine the duration of the reliability stress screening process

• mathematically analyze initial test results

• perform failure analysis

• perform stress sequence on the components

• determine approval or rejection criteria

• develop closed-loop corrective action process

• provide feedback to the component manufacturers

• discontinue the reliability stress screening process

– 18 – 61163-2 © CEI:1998

Chaque étape est décrite dans les paragraphes qui suivent. L'annexe C donne des exemples

sur la façon de déterminer les procédés de déverminage sous contraintes pour différents

composants. Ces exemples ne peuvent pas être utilisés sans discernement pour déverminer

des composants de la même famille; il convient de les considérer uniquement comme des

illustrations de la méthode pas à pas décrite dans les paragraphes suivants.

4.3 Etablir le contact entre les deux parties impliquées

Avant d'effectuer un processus de déverminage sous contraintes, il est nécessaire de

rassembler autant d'informations qu'il est possible sur le composant à déverminer. Cela peut

être réalisé en contactant le fabricant du composant. Le fabricant connaît tous les procédés

utilisés pour fabriquer le composant et sait comment ils affectent le composant final. Il sera

capable de donner un éclairage sur les modes de défaillance et les mécanismes qui peuvent

être attendus des bons composants comme des composants moins robustes. Des informations

sur les méthodes pour diagnostiquer les défectuosités sans avoir à réaliser des essais sous

contraintes peuvent aussi être disponibles.

Dans certains cas, il peut être plus économique de demander au fabricant du composant de

réaliser lui-même le déverminage sous contraintes, car il effectue déjà de tels essais inévita-

blement. Si le fabricant du composant ne peut pas, pour une raison quelconque, réaliser le

déverminage sous contraintes, il pourra, cependant, fournir des informations utiles sur la

conception et la mise en place du déverminage sous contraintes.

4.4 Identifier les défectuosités et les modes de défaillance possibles pour chaque

composant

Après consultation avec le fabricant, il convient d’ét

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...