IEC 60748-2-11:1999

(Main)Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory

Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory

Dispositifs à semiconducteurs - Circuits intégrés - Partie 2-11: Circuits intégrés numériques - Spécification particulière cadre pour mémoires mortes à circuits intégrés, à alimentation unique, effaçables et programmables électriquement

General Information

- Status

- Published

- Publication Date

- 11-Apr-1999

- Technical Committee

- SC 47A - Integrated circuits

- Drafting Committee

- WG 2 - TC 47/SC 47A/WG 2

- Current Stage

- PPUB - Publication issued

- Start Date

- 12-Apr-1999

- Completion Date

- 30-Apr-1999

Overview

IEC 60748-2-11:1999 is an international standard developed by the International Electrotechnical Commission (IEC) focusing on semiconductor devices, specifically digital integrated circuits. This part 2-11 standard provides a blank detail specification for single supply integrated circuits, particularly targeting electrically erasable and programmable read-only memory (EEPROM) devices. Established by IEC subcommittee 47A on integrated circuits under technical committee 47 (semiconductor devices), the standard aims to streamline and unify quality assurance and specification practices worldwide for these memory devices.

The key intent is to create a reference framework for manufacturers and users to specify functionalities, electrical and environmental requirements, testing procedures, and programming guidelines clearly within the EEPROM device domain. It supports standardization efforts to ensure compatibility and interchangeability across different international markets and reduces redundant testing and specification efforts.

Key Topics

Marking and Ordering Information

Specifies how semiconductor components, especially EEPROMs, should be labeled and ordered to comply with this IEC detail specification.Application Description and Functional Specification

Provides guidelines for detailing the application purpose and defining the specific function of the EEPROM integrated circuit, ensuring clarity on device roles.Limiting Values and Operating Conditions

Defines absolute maximum ratings and recommended operational parameters including temperature ranges to maintain device integrity.Electrical Characteristics

Covers electrical parameters critical to device performance, such as voltage, current limits, timing parameters, and power consumption metrics.Programming and Erasure Procedures

Describes the methods and conditions for programming and electrically erasing data within EEPROM devices, crucial for reliability and durability.Mechanical and Environmental Criteria

Includes mechanical dimensions, packaging requirements, and environmental tolerance such as temperature, humidity, and vibration resistance.Quality Assurance and Testing Procedures

Details procedures for screening, quality assessment, structural similarity validation, and comprehensive test conditions to maintain production quality.Additional Measurement Methods and Documentation

Provides extended measurement protocols and relevant documentation practices for thorough device evaluation.

Applications

IEC 60748-2-11:1999 is highly relevant for manufacturers, testing laboratories, designers, and quality assurance professionals working with single supply EEPROM integrated circuits. It applies in industries such as:

- Consumer electronics where reliable non-volatile memory is needed

- Automotive electronics requiring durable, programmable memory devices

- Telecommunications equipment requiring fast and reliable data rewrite capabilities

- Industrial control systems utilizing EEPROMs for configuration and program storage

- Any sector requiring standardized, electrically erasable and programmable memory ICs with assured quality and interoperability

Using this specification helps ensure products meet international safety, performance, and interchangeability expectations while simplifying international trade and certification processes.

Related Standards

This blank detail specification is designed to be used in conjunction with other standards within the IEC framework, including but not limited to:

IEC 60747-10 (QC 700000): Generic specification for semiconductor discrete devices and integrated circuits. This provides a foundational generic approach that complements the detailed EEPROM-specific specifications in IEC 60748-2-11.

IEC 60748-11 (QC 790100): Intermediate specification for integrated semiconductor circuits excluding hybrid circuits, ensuring coverage of integrated circuit parameters beyond EEPROM memory.

IEC 60050: International Electrotechnical Vocabulary (IEV), providing unified electrical and electronic terminology referenced throughout LED and semiconductor standards.

IEC 60027, IEC 60417, IEC 60617: Standards for letter symbols, graphical symbols, and diagrammatic representations used to ensure consistent symbolization in technical documentation.

By adhering to IEC 60748-2-11:1999, industry stakeholders promote international harmonization in the specification and quality assurance of single supply, electrically erasable, and programmable read-only memories, which plays a vital role in advancing robust, high-quality semiconductor device manufacturing and application worldwide.

Buy Documents

IEC 60748-2-11:1999 - Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory

Frequently Asked Questions

IEC 60748-2-11:1999 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory". This standard covers: Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory

Semiconductor devices - Integrated circuits - Part 2-11: Digital integrated circuits - Blank detail specification for single supply integrated circuit, electrically erasable, and programmable read-only memory

IEC 60748-2-11:1999 is classified under the following ICS (International Classification for Standards) categories: 31.200 - Integrated circuits. Microelectronics. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60748-2-11:1999 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE IEC

60748-2-11

INTERNATIONAL

QC 790108

STANDARD

Première édition

First edition

1999-04

Dispositifs à semiconducteurs –

Circuits intégrés –

Partie 2-11:

Circuits intégrés numériques –

Spécification particulière cadre pour mémoires

mortes à circuits intégrés, à alimentation unique,

effaçables et programmables électriquement

Semiconductor devices –

Integrated circuits –

Part 2-11:

Digital integrated circuits –

Blank detail specification for single supply

integrated circuit, electrically erasable, and

programmable read-only memory

Numéro de référence

Reference number

CEI/IEC 60748-2-11:1999

Numéros des publications Numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. issued with a designation in the 60000 series.

Publications consolidées Consolidated publications

Les versions consolidées de certaines publications de Consolidated versions of some IEC publications

la CEI incorporant les amendements sont disponibles. including amendments are available. For example,

Par exemple, les numéros d’édition 1.0, 1.1 et 1.2 edition numbers 1.0, 1.1 and 1.2 refer, respectively, to

indiquent respectivement la publication de base, la the base publication, the base publication incor-

publication de base incorporant l’amendement 1, et la porating amendment 1 and the base publication

publication de base incorporant les amendements 1 incorporating amendments 1 and 2.

et 2.

Validité de la présente publication Validity of this publication

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. the content reflects current technology.

Des renseignements relatifs à la date de reconfir- Information relating to the date of the reconfirmation

mation de la publication sont disponibles dans le of the publication is available in the IEC catalogue.

Catalogue de la CEI.

Les renseignements relatifs à des questions à l’étude et Information on the subjects under consideration and

des travaux en cours entrepris par le comité technique work in progress undertaken by the technical

qui a établi cette publication, ainsi que la liste des committee which has prepared this publication, as well

publications établies, se trouvent dans les documents ci- as the list of publications issued, is to be found at the

dessous: following IEC sources:

• «Site web» de la CEI* • IEC web site*

• Catalogue des publications de la CEI • Catalogue of IEC publications

Publié annuellement et mis à jour Published yearly with regular updates

régulièrement (On-line catalogue)*

(Catalogue en ligne)*

• IEC Bulletin

• Bulletin de la CEI Available both at the IEC web site* and

Disponible à la fois au «site web» de la CEI* as a printed periodical

et comme périodique imprimé

Terminology, graphical and letter

Terminologie, symboles graphiques

symbols

et littéraux

For general terminology, readers are referred to

En ce qui concerne la terminologie générale, le lecteur IEC 60050: International Electrotechnical Vocabulary

se reportera à la CEI 60050: Vocabulaire Electro- (IEV).

technique International (VEI).

For graphical symbols, and letter symbols and signs

Pour les symboles graphiques, les symboles littéraux approved by the IEC for general use, readers are

et les signes d'usage général approuvés par la CEI, le referred to publications IEC 60027: Letter symbols to

lecteur consultera la CEI 60027: Symboles littéraux à be used in electrical technology, IEC 60417: Graphical

utiliser en électrotechnique, la CEI 60417: Symboles symbols for use on equipment. Index, survey and

graphiques utilisables sur le matériel. Index, relevé et compilation of the single sheets and IEC 60617:

compilation des feuilles individuelles, et la CEI 60617: Graphical symbols for diagrams.

Symboles graphiques pour schémas.

* See web site address on title page.

* Voir adresse «site web» sur la page de titre.

NORME CEI

INTERNATIONALE IEC

60748-2-11

INTERNATIONAL

QC 790108

STANDARD

Première édition

First edition

1999-04

Dispositifs à semiconducteurs –

Circuits intégrés –

Partie 2-11:

Circuits intégrés numériques –

Spécification particulière cadre pour mémoires

mortes à circuits intégrés, à alimentation unique,

effaçables et programmables électriquement

Semiconductor devices –

Integrated circuits –

Part 2-11:

Digital integrated circuits –

Blank detail specification for single supply

integrated circuit, electrically erasable, and

programmable read-only memory

IEC 1999 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in

utilisée sous quelque forme que ce soit et par aucun procédé, any form or by any means, electronic or mechanical,

électronique ou mécanique, y compris la photo-copie et les including photocopying and microfilm, without permission in

microfilms, sans l'accord écrit de l'éditeur. writing from the publisher.

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland

Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http://www.iec.ch

CODE PRIX

Commission Electrotechnique Internationale

R

PRICE CODE

International Electrotechnical Commission

Pour prix, voir catalogue en vigueur

For price, see current catalogue

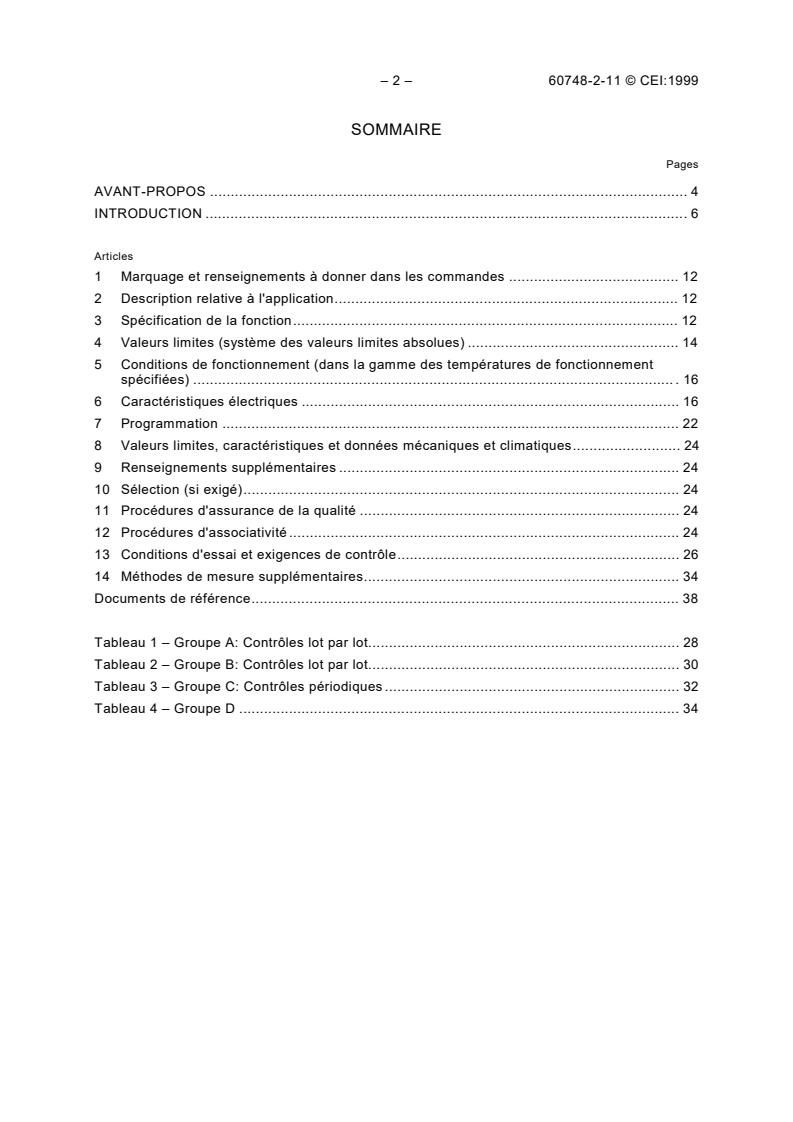

– 2 – 60748-2-11 © CEI:1999

SOMMAIRE

Pages

AVANT-PROPOS . 4

INTRODUCTION .6

Articles

1 Marquage et renseignements à donner dans les commandes . 12

2 Description relative à l'application. 12

3 Spécification de la fonction. 12

4 Valeurs limites (système des valeurs limites absolues) . 14

5 Conditions de fonctionnement (dans la gamme des températures de fonctionnement

spécifiées) .16

6 Caractéristiques électriques.16

7 Programmation.22

8 Valeurs limites, caractéristiques et données mécaniques et climatiques. 24

9 Renseignements supplémentaires.24

10 Sélection (si exigé).24

11 Procédures d'assurance de la qualité . 24

12 Procédures d'associativité.24

13 Conditions d'essai et exigences de contrôle. 26

14 Méthodes de mesure supplémentaires. 34

Documents de référence. 38

Tableau 1 – Groupe A: Contrôles lot par lot. 28

Tableau 2 – Groupe B: Contrôles lot par lot. 30

Tableau 3 – Groupe C: Contrôles périodiques . 32

Tableau 4 – Groupe D . 34

60748-2-11 © IEC:1999 – 3 –

CONTENTS

Page

FOREWORD . 5

INTRODUCTION .7

Clause

1 Marking and ordering information . 13

2 Application related description.13

3 Specification of the function. 13

4 Limiting values (absolute maximum rating system) . 15

5 Operating conditions (within the specified operating temperature range) . 17

6 Electrical characteristics.17

7 Programming.2 3

8 Mechanical and environmental ratings, characteristics and data. 25

9 Additional information.25

10 Screening (if required). 2 5

11 Quality assessment procedures. 25

12 Structural similarity procedures . 25

13 Test conditions and inspection requirements . 27

14 Additional measurement methods. 35

Reference documents. 39

Table 1 – Group A: Lot-by-lot. 29

Table 2 – Group B: Lot-by-lot. 31

Table 3 – Group C: Periodic. 33

Table 4 – Group D . 35

– 4 – 60748-2-11 © CEI:1999

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

___________

DISPOSITIFS À SEMICONDUCTEURS –

CIRCUITS INTÉGRÉS –

Partie 2-11: Circuits intégrés numériques –

Spécification particulière cadre pour mémoires mortes à circuits intégrés,

à alimentation unique, effaçables et programmables électriquement

AVANT-PROPOS

1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée

de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de

favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de

l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales.

Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le

sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en

liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation

Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés

sont représentés dans chaque comité d’études.

3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés

comme normes, rapports techniques ou guides et agréés comme tels par les Comités nationaux.

4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de

façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes

nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale

correspondante doit être indiquée en termes clairs dans cette dernière.

5) La CEI n’a fixé aucune procédure concernant le marquage comme indication d’approbation et sa responsabilité

n’est pas engagée quand un matériel est déclaré conforme à l’une de ses normes.

6) L’attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 60748-2-11 a été établie par le sous-comité 47A: Circuits

intégrés, du comité d'études 47 de la CEI: Dispositifs à semiconducteurs.

Cette norme est une spécification particulière cadre pour les mémoires mortes à circuits

intégrés à alimentation unique effaçables et programmables électriquement.

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

47A/534/FDIS 47A/548/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

Le numéro QC qui figure sur la page de couverture de la présente publication est le numéro de

spécification dans le système CEI d'assurance de la qualité des composants électroniques

(IECQ).

60748-2-11 © IEC:1999 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

INTEGRATED CIRCUITS –

Part 2-11: Digital integrated circuits – Blank detail specification

for single supply integrated circuit, electrically erasable,

and programmable read-only memory

FOREWORD

1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, the IEC publishes International Standards. Their preparation is

entrusted to technical committees; any IEC National Committee interested in the subject dealt with may

participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization

for Standardization (ISO) in accordance with conditions determined by agreement between the two

organizations.

2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has representation

from all interested National Committees.

3) The documents produced have the form of recommendations for international use and are published in the form

of standards, technical reports or guides and they are accepted by the National Committees in that sense.

4) In order to promote international unification, IEC National Committees undertake to apply IEC International

Standards transparently to the maximum extent possible in their national and regional standards. Any

divergence between the IEC Standard and the corresponding national or regional standard shall be clearly

indicated in the latter.

5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with one of its standards.

6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject

of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60748-2-11 has been prepared by subcommittee 47A: Integrated

circuits, of IEC technical committee 47: Semiconductor devices.

This standard is a blank detail specification for single supply integrated circuit electrically

erasable and programmable read-only memory.

The text of this standard is based on the following documents:

FDIS Report on voting

47A/534/FDIS 47A/548/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

The QC number that appears on the front cover of this publication is the specification number

in the IEC Quality Assessment System for Electronic Components (IECQ).

– 6 – 60748-2-11 © CEI:1999

DISPOSITIFS À SEMICONDUCTEURS –

CIRCUITS INTÉGRÉS –

Partie 2-11: Circuits intégrés numériques –

Spécification particulière cadre pour mémoires mortes à circuits intégrés,

à alimentation unique, effaçables et programmables électriquement

INTRODUCTION

Le Système CEI d'assurance de la qualité des composants électroniques fonctionne

conformément aux statuts de la CEI et sous son autorité. Le but de ce système est de définir

les procédures d'assurance de la qualité de telle façon que les composants électroniques livrés

par un pays participant comme étant conformes aux exigences d'une spécification applicable

soient également acceptables dans les autres pays participants sans nécessiter d'autres

essais.

Cette spécification particulière cadre fait partie d'une série de spécifications particulières

cadres concernant les dispositifs à semiconducteurs; elle doit être utilisée avec les publications

suivantes de la CEI:

CEI 60747-10/QC 700000:1991, Dispositifs à semiconducteurs – Dixième partie: Spécification

générique pour les dispositifs discrets et les circuits intégrés

CEI 60748-11/QC 790100:1990, Dispositifs à semiconducteurs – Circuits intégrés – Onzième

partie: Spécification intermédiaire pour les circuits intégrés à semiconducteurs à l'exclusion

des circuits hybrides

Renseignements nécessaires

Les nombres placés entre crochets sur cette page correspondent aux indications suivantes qui

doivent être portées dans les cases prévues à cet effet à la page 11 de cette spécification.

Identification de la spécification particulière

[1] Nom de l'Organisme National de Normalisation sous l'autorité duquel la spécification

particulière est établie.

[2] Numéro IECQ de la spécification particulière.

[3] Numéros de référence et d'édition des spécifications générique et intermédiaire.

[4] Numéro national de la spécification particulière, date d'édition et toute autre information

requise par le système national.

Identification du composant

[5] Fonction principale et numéro de type.

[6] Renseignements sur la construction typique (matériaux, technologie principale) et le

boîtier. Si les produits ont des variantes, elles doivent être indiquées ainsi que leurs

caractéristiques.

60748-2-11 © IEC:1999 – 7 –

SEMICONDUCTOR DEVICES –

INTEGRATED CIRCUITS –

Part 2-11: Digital integrated circuits – Blank detail specification

for single supply integrated circuit, electrically erasable,

and programmable read-only memory

INTRODUCTION

The IEC Quality Assessment System for Electronic Components is operated in accordance with

the statutes of the IEC and under the authority of the IEC. The object of this system is to define

quality assessment procedures in such a manner that electronic components released by one

participating country as conforming with the requirements of an applicable specification are

equally acceptable in all other participating countries without the need for further testing.

This blank detail specification is one of a series of blank detail specifications for semiconductor

devices and shall be used with the following IEC publications:

IEC 60747-10/QC 700000:1991, Semiconductor devices – Part 10: Generic specification for

discrete devices and integrated circuits

IEC 60748-11/QC 790100:1990, Semiconductor devices – Integrated circuits – Part 11:

Sectional specification for semiconductor integrated circuits excluding hybrid circuits

Required information

Numbers shown in brackets on this page correspond to the following items of required

information, which should be entered in the spaces provided on page 11 of this blank detail

specification.

Identification of the detail specification

[1] The name of the National Standards Organization under whose authority the detail

specification is issued.

[2] The IECQ number of the detail specification.

[3] The numbers and issue numbers of the generic and sectional specifications.

[4] The national number of the detail specification, date of issue and any further information,

if required by the national system.

Identification of the component

[5] Main function and type number.

[6] Information on typical construction (materials, the main technology) and the package. If

applicable, variants of products shall be given here, together with the variant charac-

teristics.

– 8 – 60748-2-11 © CEI:1999

La spécification particulière doit fournir une description brève comprenant les

renseignements suivants:

– technologie (N MOS, etc.);

– organisation (mots x bits);

– configuration des étages de sortie (par exemple trois états);

– fonctions essentielles.

[7] Dessin d'encombrement, identification des bornes, marquage et/ou référence aux

documents correspondants pour les encombrements.

[8] Catégories d'assurance de la qualité conformément à 2.6 de la spécification générique.

[9] Données de référence.

_______________________________________________________________________________________

[Les articles indiqués entre crochets sur la page suivante de cette norme, qui constitue la

première page de la spécification particulière, sont destinés à guider le rédacteur de la

spécification; ils ne doivent pas figurer dans la spécification particulière.]

[Lorsqu'il existe un risque d'ambiguïté quant à savoir si un paragraphe est uniquement destiné

à guider le rédacteur ou non, ce paragraphe doit être indiqué entre crochets.]

60748-2-11 © IEC:1999 – 9 –

The detail specification shall give a brief description, including the following:

– technology (N MOS, etc.);

– structure (words × bits);

– the type of output circuit (for example three state);

– major functions.

[7] Outline drawing, terminal identification, marking, and/or references to the relevant

document for outlines.

[8] Categories of assessed quality according to 2.6 of the generic specification.

[9] Reference data.

_______________________________________________________________________________________

[The clauses given in square brackets on the next page of this standard, which forms the front

page of the detail specification, are intended for guidance to the specification writer and shall

not be included in the detail specification.]

[When confusion may arise as to whether the paragraph is only an instruction to writer or not,

the paragraph shall be indicated between brackets.]

– 10 – 60748-2-11 © CEI:1999

[Nom (adresse) de l'ONH responsable [1] [N° de la spécification particulière IECQ, [2]

(et éventuellement de l'organisme auprès plus n° d'édition et/ou date]

duquel la spécification peut être obtenue)] QC 790108

COMPOSANT ÉLECTRONIQUE DE [3] [Numéro national de la spécification [4]

QUALITÉ CONTRÔLÉE particulière]

CONFORMÉMENT À:

Spécification générique: [Cette case n'a pas besoin d'être utilisée

CEI 60747-10/QC 700000 si le numéro national est identique

au numéro IECQ]

Spécification intermédiaire:

CEI 60748-11/QC 790100

[et références nationales si elles sont

différentes]

SPÉCIFICATION PARTICULIÈRE POUR LES MÉMOIRES MORTES [5]

À CIRCUITS INTÉGRÉS, À ALIMENTATION UNIQUE, EFFAÇABLES ET

PROGRAMMABLES ÉLECTRIQUEMENT

[Numéro(s) de type du ou des dispositifs]

Renseignements à donner dans les commandes: voir 1.2 de cette norme.

Description mécanique [7] Brève description [6]

Références d'encombrement:

[Références du boîtier normalisé, Application:

numéro CEI(obligatoire si disponible) Fonction:

et/ou numéro national] Construction typique:

[Si, monolithique, MOS]

Dessin d'encombrement: Encapsulation: [avec ou sans cavité]

[Peut être transféré, ou donné avec plus de [Tableau comparatif des caractéristiques

détails, à l'article 8 de cette norme] des variantes de produits]

Identification des bornes: ATTENTION: Dispositifs sensibles aux

[Dessin indiquant l'emplacement des bornes, charges électrostatiques

y compris les symboles graphiques]

Marquage: Catégories d'assurance de la qualité [8]

[Lettres et chiffres, ou code de couleurs]

(La spécification particulière doit indiquer [A choisir en 2.6

les informations à marquer sur le dispositif.] de la spécification générique]

[Voir 2.5 de la spécification générique et/ou

1.1 de cette norme]

Données de référence [9]

[Données de référence sur les propriétés les

plus importantes pour permettre la compa-

raison des types de composants entre eux]

Se reporter à la Liste des Produits Homologués en vigueur pour connaître les fabricants dont

les composants conformes à cette spécification particulière sont homologués.

60748-2-11 © IEC:1999 – 11 –

[Name (address) of responsible NAI [1] [Number of IECQ detail specification. [2]

(and possibly of body from which the plus issue number and/or date]

specification is available).] QC 790108

ELECTRONIC COMPONENTS OF [3] [National number of the detail specification] [4]

ASSESSED QUALITY IN ACCORDANCE

WITH:

Generic specification: [This box need not be used if national number

IEC 60747-10/QC 700000 repeats IECQ number]

Sectional specification:

IEC 60748-11/QC 790100

[and national reference if different]

DETAIL SPECIFICATION FOR SINGLE SUPPLY INTEGRATED CIRCUIT(S), [5]

ELECTRICALLY ERASABLE, AND PROGRAMMABLE READ-ONLY MEMORIES

[Type number(s) of the relevant device(s)]

Ordering information: see 1.2 of this standard.

Mechanical description [7] Short description [6]

Application:

Outline references:

Function:

[Standard package references should be given,

Typical construction: [Si, monolithic, MOS]

IEC number (mandatory if available) and/or

Encapsulation: [cavity or non-cavity]

national number]

[Comparison table of characteristics of

variants of the device]

Outline drawing:

[May be transferred to, or given with more

CAUTION: Electrostatic sensitive

details in clause 8 of this standard]

devices.

Terminal identification:

[Drawing showing pin assignments, including

[8]

graphical symbols] Categories of assessed quality

[From 2.6 of the generic specification]

Marking: [Letters and figures, or colour code]

[The detail specification shall prescribe the

information to be marked on the device, Reference data [9]

if any] [Reference data on the most important

properties to permit comparison between

types]

[See 2.5 of the generic specification and/or 1.1

of this standard]

Information about manufacturers who have components qualified to this detail specification is

available in the current qualified products list.

– 12 – 60748-2-11 © CEI:1999

1 Marquage et renseignements à donner dans les commandes

1.1 Marquage

Voir 2.5 de la spécification générique.

1.2 Renseignements à donner dans les commandes

[Sauf spécification contraire, les renseignements suivants constituent le minimum nécessaire

pour passer commande d'un dispositif donné:

– référence précise du modèle (et valeur de la tension nominale, si nécessaire);

– référence IECQ de la spécification particulière avec un numéro d'édition et/ou date selon le

cas;

– catégories définies à l'article 9 de la spécification intermédiaire et, si nécessaire, séquence

de sélection définie à l'article 8 de cette même spécification;

– emballage pour livraison;

– autres spécifications.]

2 Description relative à l'application

[Les caractéristiques suivantes doivent être indiquées:

– tension d'alimentation nominale;

– consommation nominale;

– consommation en mode attente (si applicable);

– modes de fonctionnement;

– compatibilité électrique (si approprié); on doit indiquer si la mémoire à circuits intégrés est

compatible électriquement avec d'autres circuits intégrés particuliers ou familles de circuits

intégrés, ou si des interfaces spéciales sont nécessaires;

– schéma synoptique global;

– résumé des conditions de programmation (voir également l'article 7 de cette norme).]

3 Spécification de la fonction

3.1 Schéma synoptique

[Le schéma synoptique doit être suffisamment détaillé pour permettre l'identification des

principales liaisons d'entrée et de sortie et des connexions extérieures (validation boîtier,

décodage d'adresse, etc.) nécessaires au fonctionnement des unités fonctionnelles

individuelles composant la mémoire.]

[Le symbole graphique de la fonction doit être indiqué. Il peut être extrait d'un catalogue de

normes de symboles graphiques ou conçu conformément aux règles de la CEI 60617-12.]

3.2 Identification et fonction des bornes

[Toutes les bornes doivent être identifiées sur le schéma synoptique (bornes d'alimentation,

bornes d'adresse, de données et de commande).]

60748-2-11 © IEC:1999 – 13 –

1 Marking and ordering information

1.1 Marking

See 2.5 of the generic specification.

1.2 Ordering information

[The following minimum information is necessary to order a specific device, unless otherwise

specified:

– precise type reference (and nominal voltage value, if required);

– IECQ reference of the detail specification with issue number and/or date, when relevant;

– categories as defined in clause 9 of the sectional specification and, if required, the screen-

ing sequence as defined in clause 8 of the sectional specification;

– packaging for delivery;

– any other particulars.]

2 Application related description

[The following characteristics shall be given:

– nominal supply voltage;

– nominal current consumption;

– stand-by current consumption (if applicable);

– operating modes;

– electrical compatibility (if appropriate); it shall be stated whether the integrated circuit

memory is electrically compatible with other particular integrated circuits or families of

integrated circuits, or whether special interfaces are required;

– overall block diagram;

– summary of the programming conditions (see also clause 7 of this standard).]

3 Specification of the function

3.1 Block diagram

[The block diagram shall be sufficiently detailed to enable the individual functional units within

the memory to be identified with their main input and output paths and the identification of their

external connections (chip enable, address decode.).]

[The graphical symbol for the function shall be given. This may be obtained from a catalogue of

standards of graphical symbols, or designed according to the rules of IEC 60617-12.]

3.2 Identification and function of terminals

[All terminals shall be identified on the block diagram (supply terminals, address, data and

control terminals).]

– 14 – 60748-2-11 © CEI:1999

[Les fonctions des bornes doivent être indiquées dans un tableau comme suit.]

Numéro Symbole Désignation Fonction Fonction de la borne

de la borne de la borne de la borne

Identification Type de circuit

entrée/sortie de sortie

3.3 Description fonctionnelle

[Les caractéristiques suivantes doivent être indiquées:

– capacité de la mémoire: nombre total d'éléments binaires pouvant être stockés dans la

mémoire;

– organisation de la mémoire: nombre d'éléments binaires par mot pouvant être stockés dans

la mémoire;

– mode opératoire (série ou parallèle);

– mode d'adressage (par exemple multiplexé, verrouillé, etc.);

– sélection boîtier* (si applicable);

– validation sortie* (si applicable);

– mode attente «standby» (si applicable);

– table de vérité (cette table doit indiquer les états de sortie en fonction des différentes

combinaisons des entrées d'adresse et de sélection);

– état logique initial de l'ensemble de la mémoire.

Le produit est conçu pour être programmé électriquement (voir 7.3).]

4 Valeurs limites (système des valeurs limites absolues)

Voir CEI 60134.

Ces valeurs s'appliquent dans la gamme des températures de fonctionnement, sauf spécifi-

cation contraire.

[Sauf spécification contraire, les valeurs limites doivent être indiquées comme suit:

– toutes les précautions à prendre relatives à un circuit intégré particulier doivent être

incluses, par exemple la manipulation des circuits MOS;

– toute interdépendance entre les valeurs limites doit être spécifiée;

– toutes les conditions pour lesquelles les valeurs limites s'appliquent doivent être indiquées;

– si des surcharges transitoires sont tolérées, leur amplitude et leur durée doivent être

spécifiées.]

___________

*

Il convient de distinguer la sélection boîtier de la validation sortie.

60748-2-11 © IEC:1999 – 15 –

[The terminal functions shall be indicated in a table as follows.]

Terminal Terminal Terminal Function Function of terminal

number symbol designation Input/output Type of output

identification circuit

3.3 Functional description

[The following characteristics shall be given:

– memory size: the total number of bits of information capable of being stored in the memory

circuit;

– memory organization: the number of bits per word capable of being stored in the memory

circuit;

– operating mode (serial or parallel);

– addressing mode (for example multiplexed, latched, etc.);

– chip select* (if applicable);

– output enable* (if applicable);

– stand-by mode (if applicable);

– truth table (this table shall show the output states versus the different combinations of the

address inputs and the select inputs);

– the initial logic state of the whole memory.

The product is designed to be electrically programmed (see 7.3).]

4 Limiting values (absolute maximum rating system)

See IEC 60134.

These values apply over the operating temperature range, unless otherwise specified.

[Unless otherwise specified, limiting values shall be given as follows:

– any cautionary statement unique to an individual integrated circuit shall be included, for

example the handling of MOS circuits;

– any interdependence of limiting values shall be specified;

– all conditions for which the limiting values apply shall be stated;

– if transient overloads are permitted, their magnitude and duration shall be specified.]

___________

* The chip select and the output enable are to be distinguished.

– 16 – 60748-2-11 © CEI:1999

Pour toutes les tensions, la référence est une borne de référence désignée.

Caractéristiques Symboles Min.* Max.* Unités

Tension d'alimentation xx V

V

CC

Tension d'entrée V xx V

I

Tension de sortie V xx V

O

Tension à l'état bloqué (voir note) V xx V

OZ

Courant de sortie I xx mA

O

Courant d'entrée I xx mA

I

Dissipation de puissance P n.a. x W

D

Température de fonctionnement T xx °C

amb

Température de stockage T xx °C

stg

NOTE – S'il y a lieu.

* Valeurs algébriques

5 Conditions de fonctionnement (dans la gamme des températures de

fonctionnement spécifiées)

Ces conditions ne sont pas destinées à être contrôlées, mais elles sont applicables à l'assu-

rance de qualité.

Caractéristiques Symboles Min.* Max.* Unités

Tension d'alimentation V xx V

CC

Tension d'entrée au niveau bas V xx V

IL

Tension d'entrée au niveau haut V xx V

IH

Température de fonctionnement T xx °C

amb

6 Caractéristiques électriques

Les caractéristiques doivent s'appliquer dans toutes les conditions de fonctionnement définies

à l'article 5, sauf spécification contraire.

[Si la performance indiquée du circuit varie dans la gamme des températures de

fonctionnement, les valeurs des tensions d'entrée et de sortie et de leurs courants associés

doivent être indiquées à 25 °C et aux deux températures extrêmes de fonctionnement. Les

valeurs de courant et de tension doivent être indiquées pour chaque type fonctionnellement

différent d'entrée et/ou de sortie.

Les caractéristiques spéciales et les exigences de temps doivent être spécifiées.]

60748-2-11 © IEC:1999 – 17 –

All voltages are referenced to a designated reference terminal.

Characteristics Symbols Min.* Max.* Unit

Supply voltage XX V

V

CC

Input voltage V XX V

I

Output voltage V XX V

O

Off-state voltage (see note) V XX V

OZ

Output current I XX mA

O

Input current XX mA

I

l

Power dissipation P n.a. X W

D

Operating temperature T XX °C

amb

Storage temperature T XX °C

stg

NOTE – Where appropriate.

* Algebraic values

5 Operating conditions (within the specified operating temperature range)

These conditions are not to be inspected but may be used for quality assessment purposes.

Characteristics Symbols Min. Max. Unit

Supply voltage V XX V

CC

Low-level input voltage V XX V

IL

High-level input voltage V XX V

IH

Operating temperature T XX °C

amb

6 Electrical characteristics

The characteristics shall apply over the full operating conditions in clause 5 unless otherwise

specified.

[Where the stated performance of the circuit varies over the operating temperature range, the

values of the input and output voltages, and their associated currents shall be stated at 25 °C

and at the extremes of the operating temperature range. Values of current and voltage shall be

given for each functionally different type of input and/or output.

Special characteristics and timing requirements shall be specified.]

– 18 – 60748-2-11 © CEI:1999

6.1 Caractéristiques statiques (note 5)

Caractéristiques Conditions Symboles Min.* Max. Unités

(note 4)

Courant(s) d'alimentation V max. I XX mA

CC CC

(note 1) (mode actif)

Courant(s) d'alimentation V max. I XX mA

CC CC

(note 1) (mise en attente)

Tension de sortie au niveau haut V min. V XX V

CC OH

I

OHA

Tension de sortie au niveau bas XX V

V min. V

CC OL

I

OLA

Courant d'entrée ou de fuite au niveau haut V max. I XX μA

CC IH(1)

V

IHB

Courant d'entrée ou de fuite au niveau haut V max. I XX μA

CC IH(2)

(note 1) V

IHA

Courant d'entrée ou de fuite au niveau bas V max. I XX μA

CC IL(1)

V

ILA

Courant d'entrée ou de fuite au niveau bas V max. I XX μA

CC IL(2)

V

ILB

Courant de sortie au niveau haut V min. I XX μA

CC OH

V

OHB

Courant de sortie au niveau bas V max. I XX mA

CC OL

V

OLA

Courant de sortie (fuite) au niveau haut V max. I XX μA

CC OHX

(note 2)

V

OHA

Courant de sortie (fuite) au niveau bas V max. I XX μA

CC OLX

(note 2)

V

OLB

Courant de sortie au niveau haut (fuite) pour les XX μA

V max. I

CC OHZ

sorties trois états

V

(si applicable) OHB

Courant de sortie au niveau bas (fuite) pour les V max. I XX μA

CC OLZ

sorties trois états

V

(si applicable) OLA

Courant de court-circuit en sortie V max. I XX mA

CC OS

(note 3)

V = 0

O

NOTE 1 – S'il y a lieu.

NOTE 2 – I et I s'appliquent uniquement aux circuits possédant des sorties à collecteur ouvert (ou

OHX OLX

source/drain ouvert) et dans ce cas ils remplacent I et I .

OH OL

NOTE 3 – Durée à spécifier et nombre maximum permis, de sorties simultanément en court-circuit à spécifier.

NOTE 4 – Les tensions d'alimentation doivent être spécifiées pour assurer que la mesure de la caractéristique

correspondante est effectuée dans les conditions de pire cas.

NOTE 5 – Le dispositif doit être programmé pour la mesure de certaines caractéristiques.

* Valeurs algébriques

60748-2-11 © IEC:1999 – 19 –

6.1 Static characteristics (note 5)

Characteristics Conditions Symbols Min.* Max.* Unit

(note 4)

Supply currents (note 1) V max. I XX mA

CC CC

(active mode)

Supply currents (note 1) V max. I XX mA

CC CC

(stand-by)

High-level output voltage V min. V XXV

CC OH

I

OHA

Low-level output voltage V min. V XXV

CC OL

I

OLA

High-level input or leakage current V max. I XX

μA

CC IH(1)

V

IHB

High-level input or leakage current (note 1) XX

V max. I μA

CC IH(2)

V

IHA

Low-level input or leakage current V max. I XX

μA

CC IL(1)

V

ILA

Low-level input or leakage current XX

V max. I μA

CC IL(2)

V

ILB

High-level output current V min. I XX

μA

CC OH

V

OHB

Low-level output current XX mA

V max. I

CC OL

V

OLA

High-level output current V max. I XX μA

CC OHX

(leakage) (note 2)

V

OHA

Low-level output current V max. I XX

μA

CC OLX

(leakage) (note 2)

V

OLB

High-level output leakage current at three-state V max. I XX μA

CC OHZ

outputs (if applicable)

V

OHB

Low-level output leakage current at three-state V max. I XX

μA

CC OLZ

outputs (if applicable)

V

OLA

Output short circuit current (note 3) V max. I XX mA

CC OS

V = 0

O

NOTE 1 – Where appropriate.

NOTE 2 – I and I apply only to circuits having open-collector (or open source/drain) outputs and in that

OHX OLX

case replace I and I .

OH OL

NOTE 3 – Duration and maximum allowable number of simultaneously short-circuited outputs to be specified.

NOTE 4 – The supply voltages shall be specified to ensure the worst case for the relevant characteristic

measurement.

NOTE 5 – For measurement of some characteristics, it may be necessary to programme the device.

* Algebraic values

– 20 – 60748-2-11 © CEI:1999

[Les valeurs suivantes doivent être indiquées s'il y a lieu; lorsque certaines bornes peuvent

jouer le rôle d'entrées ou de sorties, on doit fournir les informations dans ces deux cas.]

6.2 Caractéristiques dynamiques

Caractéristiques Conditions Symboles Min. Max. Unités

(note 1)

Temps d'accès adresse Xns

t

a(A)

Temps d'accès autorisation boîtier Xns

t

a(E)

Temps d'accès pour l'opération de lecture t . Xns

a

(note 2)

– sortie après adressage

– sortie après autorisation

– sortie après la fin du mode d'attente

Temps de maintien de validité des données Xns

t (.)

v

(note 2)

– après la fin d'autorisation

– après la fin de validité de l'adresse

– après la fin de l'autorisation de sortie

– après l'entrée du mode d'attente

Temps d'autorisation et d'inhibition (note 2) des t Xns

dis

sorties trois états au début et à la fin de l'état

t

haute impédance, mesurés sur la base du temps en

de transition approprié d'autorisation de sortie

Temps de cycle de lecture (note 2) t Xns

a(R)

Fréquence d'horloge (note 2) X X MHz

NOTE 1 – Les conditions d'essais et les circuits de charge doivent être séparés.

NOTE 2 – Si applicable.

6.3 Diagrammes des temps

[Des diagrammes des temps doivent être fournis, comportant un ensemble complet de signaux

indiquant le fonctionnement de chaque mode du circuit. Il convient d'indiquer tous les

intervalles de temps que l'utilisateur doit connaître pour assurer le fonctionnement correct de la

mémoire.

On doit indiquer sur ces diagrammes tous les paramètres spécifiés en 6.2.]

6.4 Capacités

Caractéristiques Conditions Symboles Min. Max. Unités

Capacité d'entrée V = 0 V C XpF

cc

in

Capacité de sortie (si applicable) V = 0 V C XpF

cc

out

6.5 Endurance écriture/effacement – Nombre de cycles de programmation

Caractéristiques Conditions Symboles Min. Max. Unités

Endurance écriture/effacement Voir 14.2 X Cycles

(voir

note)

NOTE – Nombre d'opérations par unités adressables (par exemple bits, multiplets, mots, pages, etc.).

60748-2-11 © IEC:1999 – 21 –

[The following shall also be stated where appropriate; where certain terminals may function as

inputs or as output, then information shall be given for both these conditions.]

6.2 Dynamic characteristics

Characteristics Conditions Symbols Min. Max. Unit

(note 1)

Address access time Xns

t

a(A)

Chip enable access time t Xns

a(E)

Read operation access time (note 2) t . Xns

a

– output after address

– output after enable

– output after leaving standby mode

Output valid times (note 2) t (.)Xns

v

(times for which data remains valid)

– after end of enabl

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...