IEC 60748-4-3:2006

(Main)Semiconductor devices - Integrated circuits - Part 4-3: Interface integrated circuits - Dynamic criteria for analogue-digital converters (ADC)

Semiconductor devices - Integrated circuits - Part 4-3: Interface integrated circuits - Dynamic criteria for analogue-digital converters (ADC)

Specifies a set of measuring methods and requirements for testing ADCs under dynamic conditions, together with associated terminology and characteristics

General Information

- Status

- Published

- Publication Date

- 28-Aug-2006

- Technical Committee

- SC 47A - Integrated circuits

- Drafting Committee

- WG 4 - TC 47/SC 47A/WG 4

- Current Stage

- PPUB - Publication issued

- Start Date

- 29-Aug-2006

- Completion Date

- 30-Nov-2006

Relations

- Effective Date

- 10-Feb-2026

Overview

IEC 60748-4-3:2006 - "Semiconductor devices - Integrated circuits - Part 4-3: Interface integrated circuits - Dynamic criteria for analogue-digital converters (ADC)" specifies measuring methods, terminology and requirements for testing ADCs under dynamic conditions. The standard defines how to obtain time-domain output records from ADCs, convert them to the frequency domain (FFT) and quantify dynamic performance including distortion, noise and spurious outputs. It covers both single-frequency (sinusoidal) and wideband test methods and explains relevant terms such as coherent sampling, equivalent-time sampling, and signal-dependent timing error.

Key topics

- Scope and purpose: dynamic testing methods and requirements for ADC characterization under realistic operating (time-varying) inputs.

- Test methods

- Sinusoidal (single-tone) testing - coherent sampling, FFT-based analysis to derive SINAD, THD, SFDR and SNR.

- Wideband testing - pseudo-random binary sequence (PRBS) or other wideband excitations to better represent typical amplitude probability density functions (APDF) and reveal APDF-dependent linearity effects.

- Measured characteristics

- Settling time, overload recovery and rise/fall times

- Linearity: total linearity error, differential linearity error (DNL)

- Dynamic distortion and noise metrics: THD, SINAD, SFDR, SNR, noise floor, effective number of bits (ENOB / Nef)

- Signal-dependent timing error and spurious frequencies

- Word error rate for non-random errors

- Measurement setup: recommended test arrangement (clock source, filters, waveform generators, ADC under test, capture buffer and computer) and guidance on record sizing and analysis (time-domain records → FFT).

Applications and users

IEC 60748-4-3 is intended for:

- ADC and semiconductor manufacturers - to qualify dynamic performance during design verification and production test.

- Test laboratories and QA teams - for standardized evaluation of ADC dynamic metrics.

- System integrators and designers - to select ADCs for communications, audio, instrumentation, medical, and data-acquisition systems where dynamic accuracy is critical.

- Standards and compliance engineers - to harmonize ADC test reporting and compare devices using common metrics (SINAD, SFDR, ENOB).

Practical benefits include more realistic performance assessment using wideband stimuli (PRBS) and clear definitions of sampling techniques (coherent and equivalent-time sampling) that directly affect measured ENOB, distortion and spurious behavior.

Related standards

- IEC 60748-4:1997 - general test methods for interface integrated circuits (Category II); referenced normative baseline.

- IEC 60268-10:1991 - sound system equipment - peak programme level meters (referenced for measurement practice).

Keywords: IEC 60748-4-3, ADC dynamic testing, analogue-digital converters, SINAD, SFDR, ENOB, SNR, THD, coherent sampling, wideband testing, APDF, pseudo-random binary sequence.

Frequently Asked Questions

IEC 60748-4-3:2006 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Integrated circuits - Part 4-3: Interface integrated circuits - Dynamic criteria for analogue-digital converters (ADC)". This standard covers: Specifies a set of measuring methods and requirements for testing ADCs under dynamic conditions, together with associated terminology and characteristics

Specifies a set of measuring methods and requirements for testing ADCs under dynamic conditions, together with associated terminology and characteristics

IEC 60748-4-3:2006 is classified under the following ICS (International Classification for Standards) categories: 31.200 - Integrated circuits. Microelectronics. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60748-4-3:2006 has the following relationships with other standards: It is inter standard links to EN 62008:2005. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60748-4-3:2006 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL IEC

STANDARD 60748-4-3

First edition

2006-08

Semiconductor devices –

Integrated circuits –

Part 4-3:

Interface integrated circuits – Dynamic criteria

for analogue-digital converters (ADC)

Reference number

Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the

60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example,

edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the

base publication incorporating amendment 1 and the base publication incorporating

amendments 1 and 2.

Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC,

thus ensuring that the content reflects current technology. Information relating to

this publication, including its validity, is available in the IEC Catalogue of

publications (see below) in addition to new editions, amendments and corrigenda.

Information on the subjects under consideration and work in progress undertaken

by the technical committee which has prepared this publication, as well as the list

of publications issued, is also available from the following:

• IEC Web Site (www.iec.ch)

• Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/searchpub) enables you to

search by a variety of criteria including text searches, technical committees

and date of publication. On-line information is also available on recently issued

publications, withdrawn and replaced publications, as well as corrigenda.

• IEC Just Published

This summary of recently issued publications (www.iec.ch/online_news/ justpub)

is also available by email. Please contact the Customer Service Centre (see

below) for further information.

• Customer Service Centre

If you have any questions regarding this publication or need further assistance,

please contact the Customer Service Centre:

Email: custserv@iec.ch

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

INTERNATIONAL IEC

STANDARD 60748-4-3

First edition

2006-08

Semiconductor devices –

Integrated circuits –

Part 4-3:

Interface integrated circuits – Dynamic criteria

for analogue-digital converters (ADC)

IEC 2006 Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or

mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

PRICE CODE

Commission Electrotechnique Internationale W

International Electrotechnical Commission

МеждународнаяЭлектротехническаяКомиссия

For price, see current catalogue

– 2 – 60748-4-3 IEC:2006(E)

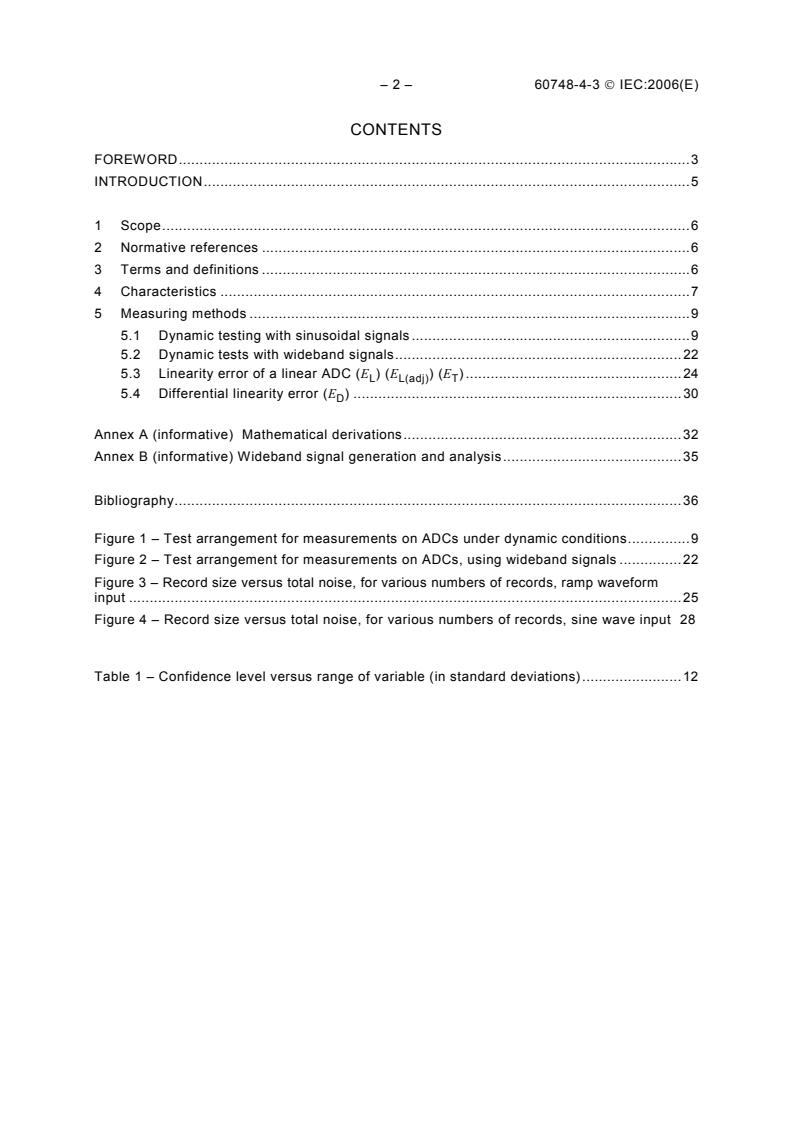

CONTENTS

FOREWORD.3

INTRODUCTION.5

1 Scope.6

2 Normative references .6

3 Terms and definitions .6

4 Characteristics .7

5 Measuring methods .9

5.1 Dynamic testing with sinusoidal signals .9

5.2 Dynamic tests with wideband signals.22

5.3 Linearity error of a linear ADC (E ) (E ) (E ) .24

L L(adj) T

5.4 Differential linearity error (E ) .30

D

Annex A (informative) Mathematical derivations.32

Annex B (informative) Wideband signal generation and analysis.35

Bibliography.36

Figure 1 – Test arrangement for measurements on ADCs under dynamic conditions.9

Figure 2 – Test arrangement for measurements on ADCs, using wideband signals .22

Figure 3 – Record size versus total noise, for various numbers of records, ramp waveform

input .25

Figure 4 – Record size versus total noise, for various numbers of records, sine wave input 28

Table 1 – Confidence level versus range of variable (in standard deviations).12

60748-4-3 IEC:2006(E) – 3 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

SEMICONDUCTOR DEVICES –

INTEGRATED CIRCUITS –

Part 4-3: Interface integrated circuits –

Dynamic criteria for analogue-digital converters (ADC)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60748-4-3 has been prepared by subcommittee 47A: Integrated

circuits, of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

FDIS Report on voting

47A/750/FDIS 47A/758/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

– 4 – 60748-4-3 IEC:2006(E)

The list of all the parts of the IEC 60748 series, under the general title Semiconductor devices

– Integrated circuits, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

60748-4-3 IEC:2006(E) – 5 –

INTRODUCTION

The use of ADCs has increased significantly in the last few years with the large increase in

the use of digital signal processing. The majority of the processing of analogue signals now

takes place in the digital domain, and this requires high precision in the conversion of signals

from the analogue to the digital form. Consequently, the characterization of ADCs is of great

importance.

IEC 60748-4 contains measuring methods for ADCs in which the test conditions are either

static or change very slowly. However, some of the characteristics of an ADC can change to

some degree with the rate of change of the input signal, and there are other characteristics

that cannot be measured except under dynamic conditions. Consequently, a set of dynamic

tests is required in order to obtain the response of an ADC when operated under dynamic

conditions.

The output of a dynamic test consists of the set of output code values obtained during the

test. This record, being the sequence in time of a set of values, gives information in the “time-

domain”. The result of applying the Fourier Transform to the record is information that is in the

“frequency domain”, and this contains the spectrum of the output over the range of

frequencies of interest. In particular, distortion, noise and spurious output frequencies can

then be evaluated.

This International Standard introduces a set of dynamic methods, which are now coming into

use in industry and which rely mostly on measurements made with sinusoidal input signals,

and of which the results are suitable for analysis in the frequency domain. It also includes a

further dynamic method that uses a wide-band input signal. For the reasons explained below,

industry has shown great interest in this particular method.

Linearity errors of an ADC are dependent on the amplitude of the input signal and its rate of

change. Not so well known is that linearity errors also depend on the instantaneous amplitude

distribution, i.e. amplitude probability density function (APDF) of the input signal. This source

of error is usually a result of localized heating effects in the integrated circuit and is

dependent on ADC architecture and internal circuit layout.

Single-frequency signals have an APDF concentrated at the extremes and therefore

exaggerate the effect of errors at the ends of the input range compared to those nearer the

centre. Conversely, a wide-band signal has an APDF concentrated more around the centre of

the input range. A wide-band signal is much closer to the typical input signal in the majority of

ADC applications than a single-frequency signal. Therefore, measurements made with such a

signal will give more realistic error estimates.

A wide-band signal can be generated from a pseudo-random binary sequence. Although such

a signal appears to be noisy, it contains only a set of defined frequencies and is therefore

suitable for measuring errors.

– 6 – 60748-4-3 IEC:2006(E)

SEMICONDUCTOR DEVICES –

INTEGRATED CIRCUITS –

Part 4-3: Interface integrated circuits –

Dynamic criteria for analogue-digital converters (ADC)

1 Scope

This part of IEC 60748 specifies a set of measuring methods and requirements for testing

ADCs under dynamic conditions, together with associated terminology and characteristics.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 60748-4:1997, Semiconductor devices – Integrated circuits – Part 4: Interface integrated

circuits

IEC 60268-10:1991, Sound system equipment – Part 10: Peak programme level meters

3 Terms and definitions

For the purposes of this document, the following definitions, in addition to those found in

Chapter II, Clause 2, Terms for category II of IEC 60748-4:1997, apply.

3.1

coherent sampling

process in which the output record contains samples taken from an integral number of input

cycles of a repetitive waveform

NOTE In general, this process is limited to the case where the number of input cycles and the number of samples

in the record have no common factors.

3.2

equivalent-time sampling

coherent sampling in which consecutive samples of a repetitive waveform, acquired from

multiple repetitions of the waveform, are assembled and re-arranged to produce a single

record of samples that represent a single repetition of the waveform

NOTE This process is normally used only when the spectrum of the input waveform contains significant amounts

of energy at frequencies above half the sampling frequency. It has the result that each frequency in the input

appears in the output divided by the number of repetitions. For each successive input cycle, the set of samples is

delayed (or advanced) relative to the previous set by a fixed amount.

3.3

(code) transition value

boundary between two adjacent steps

3.4

signal-to-noise-and-distortion ratio

for a pure sine-wave input, ratio of the r.m.s. amplitude of the output signal at the input

frequency to the r.m.s. amplitude of all other signals in the output

60748-4-3 IEC:2006(E) – 7 –

3.5

(spurious-free) dynamic range

for a pure sine-wave input, ratio of the r.m.s. amplitude of the output signal at the input

frequency to the largest r.m.s. amplitude of the output at any other single frequency

3.6

effective number of bits

N

ef

practical limit of the resolution of an ADC due to inherent noise and errors

3.7

signal-dependent timing error

effect equivalent to the delay of the instant of sampling, in an ADC, that is proportional to the

rate of change of input voltage

NOTE This effect is caused by the inherent voltage-dependent non-linearity of circuit elements in semiconductors.

3.8

spurious frequency

persistent sine wave in the output that is not considered to be a harmonic of the input

frequency

3.9

word error rate

probability of an output code having an error not attributable to random noise or to offset,

gain, and linearity errors

4 Characteristics

The following characteristics shall be included as characteristics applicable to ADCs and

should be read with reference to Chapter III, Section 2, Category II, Clause 4 of IEC 60748-

4:1997.

– 8 – 60748-4-3 IEC:2006(E)

Conditions at 25 °C Requirements

Letter

Ref. Characteristic unless specified Notes

Symbol

Max. Min.

otherwise

4.1 Settling time Supply voltages X

t

tot

Input step amplitude

4.2 Long-term settling error X

E

LT

Specified levels for

4.3 Rise and fall times X

transition time

t ; t

r f

Clock frequency, as

4.4 Limiting rate of change of (Δv/Δt) , X

max

appropriate

output (slew rate)

SR

Conditions at other

terminals

Tolerance for settling time

4.5 Overload recovery times

4.5.1 Input overload recovery time, Supply voltages X

t

or

where appropriate

Input signal frequency, as

appropriate t X

ord

4.5.2 Differential-mode input

overload recovery time,

Input signal amplitude

where appropriate

Overload signal amplitude

and duration

t X

orc

4.5.3 Common-mode input

overload recovery time,

Clock frequency, as

where appropriate

appropriate

Conditions at other

terminals

4.6 Differential gain, where Supply voltages A X

dif

appropriate

Input signal frequency, as

appropriate

4.7 Differential phase, where X

φ

dif

appropriate

Input signal amplitude

Clock frequency, as

appropriate

DC input levels

Conditions at other

terminals

Desired accuracy

4.8 Total harmonic distortion Supply voltages THD X

Input signal frequency, as

4.9 Spurious-free dynamic range SFDR X

appropriate

4.10 Signal-to-noise-and- SINAD X

Input signal amplitude

distortion ratio

Clock frequency, as

N

4.11 Effective number of bits ef X

appropriate

4.12 Signal-to-noise ratio SNR X

Highest harmonic

4.13 Noise floor NF X

excluded from noise, if

not 10th

4.14 Signal-dependent timing X

E

SDT

error Conditions at other

terminals

60748-4-3 IEC:2006(E) – 9 –

5 Measuring methods

5.1 Dynamic testing with sinusoidal signals

The following methods are to be read with reference to Chapter IV, Section 3, Category II,

Group I of IEC 60748-4:1997. All references below to IEC 60748-4:1997 apply to this clause.

5.1.1 Dynamic testing of ADCs – General requirements

5.1.1.1 Purpose

To specify the general requirements for measuring the characteristics of an ADC under

dynamic conditions.

5.1.1.2 Circuit diagram

Clock

Filter

generator

Sine wave

generator(s)

Frequency ADC Latch/ Buffer

Filter Computer

Sum

synthesizer under test demux memory

Square wave

generator

Ramp

generator

DC

voltage

IEC 1503/06

Figure 1 – Test arrangement for measurements on ADCs under dynamic conditions

Optional elements are shown in broken outline.

5.1.1.3 Circuit description and requirements

– Case a) sine wave input

The input voltage generator shall provide an accurate sinusoidal waveform with adjustable

and stable amplitude and frequency.

– Case b) step input

The input voltage generator shall provide a stepped wave, usually a square wave, without

droop, and with adjustable and stable levels, duty-cycle and periodicity.

– Case c) linear input ramp

The input voltage generator shall provide an accurate linear rising and/or falling waveform

with adjustable and stable amplitude, duty-cycle and periodicity.

– 10 – 60748-4-3 IEC:2006(E)

– All cases:

Precautions shall be taken to avoid coupling between the sampling clock and the input

circuits, and between the output and input circuits, and the networks used to combine input

signals shall be designed to minimize any stray reactive elements that could affect the

bandwidth of applied signals.

Noise at the input should be small compared with the output noise that is generated within the

ADC, and preferably no larger in magnitude than the noise that results from the quantization

process, i.e. significantly less than 1 LSB in magnitude. When necessary, and normally only

for sine waves, input noise can be reduced by passing the signal through a low-pass or band-

pass filter. The latter may also be used to reduce any frequency instability in the signal.

Any impurity in the signal waveform and instability in its frequency should be low enough not

to affect the accuracy of the measurements. Similarly, any instability in the frequency (jitter)

of the clock signal should be equally low. Ideally, the input signal and the clock signal should

be synchronized from a common source.

The adjustment range of the input voltage should be such that, at its maximum excursion, the

most positive and most negative peaks exceed the working range of the ADC, but do not

exceed its limiting input voltages.

Equipment shall be included for the adjustment of offset and gain points of adjustable

converters.

For some measurements, both step and sinusoidal inputs are applied together to the ADC.

The recording equipment should be capable of storing each output code obtained during the

test duration. In cases where this is physically not possible, or accuracy is reduced in a long

test duration due to frequency instability, then the test may be divided into a set of segments

of equal length, where the record of each segment is analysed separately, provided that for

each segment the phase of the input signal at its start is either randomly chosen or uniformly

distributed within the range 0.2π.

For analysis of the histogram of the ADC output, the recording equipment shall count the

number of occurrences of each individual output code value during the test. The test duration

should be such that each output code value appears enough times to achieve the required

accuracy (see Figures 3 and 4 and also Annex A) to determine a suitable number.

For analysis of the spectrum of the ADC output, the recording equipment shall record the

code value of each individual sample during the test.

5.1.1.4 Special precautions regarding accuracy

Note the comments above regarding signal purity, frequency stability, and input noise.

In order that each test is carried out with coherent sampling, the duration of each segment of

the test shall be set to an integral number of input cycles. However, the periodicity or

frequency of the input waveform and that of the sampling clock shall not have a common

factor, thus

f = f · J/M (1)

i s

where

f is the input frequency;

i

f is the sampling frequency;

s

60748-4-3 IEC:2006(E) – 11 –

M is the number of samples in a test record;

J is the number of input periods in a test record, an integer,

the fraction J/M shall be irreducible.

If the requirement for J to be an integer is not met, then the method of analysis will give large

errors. Although there is a mathematical procedure that can extract reasonably accurate

results when J is not an integer, its use is outside the scope of this standard.

In general, J will be an odd number greater than 1, and M an even number. For certain cases,

detailed below (see 5.1.1.5), M should be a power of 2.

Ideally for analysis of the spectrum, each output code should appear at least once in the

output record. There are 2N possible output codes, when N is the number of bits. In the case

of sine-wave input (and a linear ADC), for each output code to appear at least once, it is

required that

M ≥ π⋅2N (2)

When it is required that the input frequency should be very close to a particular input

frequency (f ), then proceed as follows: find an integer, r, near to f /f , let J equal the integral

i s i

part of M/r, then

fi = fs⋅J/(r⋅J – 1) (3)

and = r⋅J – 1 (4)

5.1.1.4.1 Histogram testing

For tests that determine the transfer characteristic, and thereby the linearity errors, the

dynamic method involves obtaining a histogram of output codes. Provided that the input

signal is sufficiently free from error, accuracy increases with the number of samples recorded

for each code value. Specific requirements to achieve the required accuracy are given in the

corresponding method.

5.1.1.4.2 Spectral analysis

For spectral analysis, provided that M is sufficient to give at least one sample for each code

value, the accuracy increases with M , but the error due to frequency instability increases

with the product of both J and M, thus J should not be large. Where an increase in accuracy is

desired, then multiple records, starting at different points in the input waveform, may be used

to give an improvement proportional to R , where R is the number of records. In this case, it

is usual to compute the required terms separately for each record and take the average over

all the records of each term.

To take account of variations in actual step width, frequency instability and jitter, the value of

M should be increased from the theoretical minimum, so that

N

π ⋅2

M ≥

11−⋅KEσ ⋅ −

()

()φ Dmax

(5)

where

N is the number of bits of the ADC;

K is the number of standard deviations that give the required confidence level (see

Table 1);

σ is the r.m.s. value of combined phase jitter, referred to the clock period;

φ

E is the maximum value of differential linearity error.

Dmax

– 12 – 60748-4-3 IEC:2006(E)

Table 1 – Confidence level versus range of variable (in standard deviations)

Confidence level

80 90 95 98 99 99,5

p (%)

Range multiplier

1,282 1,645 1,960 2,326 2,576 2,807

K

5.1.1.5 Calculations using the Fourier Transform

The Discrete Fourier Transform (DFT) of the set of samples in a record is given by

M −1

(j−2π.n.k/M)

Xn[]=⋅x[k] e

∑

k =0

(6)

where

M is the number of samples in the record;

x[k] is the sample number k;

X[n] is the spectral line number n of the transform, representing the frequency given by

f ⋅n /M .

s

The frequency f of a spectral line is given by

f = f ⋅n/M (7)

s

To choose the spectral line corresponding to the input frequency F , set n = J (see 5.1.1.4).

i

See Annex A for details on evaluating the DFT.

The spectrum of interest normally ranges from n = 0 (d.c.) to n = M/2 – 1 (where M/2 is the

Nyquist frequency). The range from M/2 + 1 to M is a mirror of the lower half and should be

ignored. In general, the particular frequencies of interest are the fundamental and the 2nd to

10th harmonics for the case of a single input frequency, or the two fundamentals and the

lower intermodulation products for the case of two input frequencies.

Any frequencies in the input signal that are above the Nyquist frequency will also appear in

the range 0.M/2 – 1 and, therefore, shall be excluded from the input.

For the case where M is a power of 2, but only in this case, the Fast Fourier Transform (FFT)

can be used to obtain the full spectrum very rapidly. This version of the procedure reduces

the number of computations by the factor of M/log (M). Thus when M = 4 096, this factor is

approximately 340.

It follows that where the full spectrum is required, and particularly when determining noise

power, M should be an exact power of 2 so that the FFT may be used, whereas for the

evaluation of a small number of individual frequencies, M may be chosen otherwise and the

DFT used.

5.1.2 Differential gain and phase (A , φ

dif dif)

5.1.2.1 Purpose

To measure the change of gain and phase with change of mean d.c. input level to an ADC.

5.1.2.2 Circuit diagram

See Figure 1.

60748-4-3 IEC:2006(E) – 13 –

5.1.2.3 Circuit description and requirements

The circuit description and requirements given in 5.1.1.3 are applicable for this measurement.

The input to the ADC being measured shall be a sinusoidal signal superimposed on a d.c.

voltage. The d.c. voltage shall be capable of being set to any specified value within the full-

scale range of the ADC, either manually or automatically with a pre-set waveform generator.

The actual d.c. levels and signal amplitude used should be chosen so as to avoid peak

clipping.

For one particular application, d.c. levels of 1/7, 2/7, 3/7, 4/7, 5/7, and 6/7 of full scale are

used with the sinusoidal signal having a peak amplitude of 1/7 full scale.

5.1.2.4 Special precautions

The amplitude and phase of the a.c. component of the input signal shall be kept constant

during the measurement and shall be independent of the value of the d.c. component of the

input signal.

5.1.2.5 Measurement procedure

The number of samples in a record necessary to achieve the desired accuracy is calculated

as explained in the general requirements, and the exact value of either (or both) the input and

clock frequencies, as appropriate, is calculated for the chosen record length.

The temperature of the integrated circuit being measured is set to the specified value.

The input and output terminals, as well as the remaining terminals, are connected as

specified. The power supplies and any other additional networks are connected as specified.

Unless otherwise specified, adjustments shall be made to minimize the offset and gain errors

as described in 15.1.4 of IEC 60748-4:1997.

The a.c. component of the input signal is set to the specified amplitude and frequency, and

the clock frequency is set as specified.

All relevant control input signals shall be applied.

The d.c. input voltage is set to the first of the specified values, and the record of the resulting

output codes is stored for subsequent analysis. This action is then repeated for each of the

remaining specified d.c. values, ensuring, where possible, that each record starts at the same

point on the input sine wave.

Each record is processed using the Fourier Transform to obtain the amplitude and phase of

the component at the fundamental input frequency. If the phase of the input signal at the

starting point of a subsequent record is not the same as for the first record, then the

calculated phase shall be corrected by the amount of its difference before being used as

follows.

The differential gain is given by the absolute maximum of the differences in gain between any

two records.

The differential phase is similarly given by the absolute maximum of the differences in phase

between any two records.

– 14 – 60748-4-3 IEC:2006(E)

5.1.2.6 Specified conditions

• Ambient or reference point temperature.

• Supply voltages.

• Input signal frequency, as appropriate.

• Input signal amplitude.

• DC input levels.

• Clock frequency, as appropriate.

• Conditions at other terminals.

• Desired accuracy.

5.1.3 Signal-to-noise-and-distortion ratio, signal-to-noise ratio, noise floor, effective

number of bits (N )

ef

5.1.3.1 Purpose

To measure the ratio of signal power to residual power, to measure the ratio of signal power

to noise power, after excluding harmonically-related components, to measure the mean noise

amplitude, in the output of an ADC, and to determine its effective resolution when taking

account of inherent noise and error.

5.1.3.2 Circuit diagram

See Figure 1.

5.1.3.3 Circuit description and requirements

The circuit description and requirements given in 5.1.1.3 are applicable for this measurement.

The input to the ADC being measured shall be a sinusoidal signal.

5.1.3.4 Special precautions

Any inaccuracy in the input signal or the clock period due to noise, frequency or amplitude

instability, etc. will contribute to the output noise and should therefore be minimized. The use

of filters is recommended to reduce the effect of such sources of error.

5.1.3.5 Measurement procedure

The number of samples in a record and, if required, the number of records needed to achieve

the desired accuracy are calculated as explained in the general requirements, and the exact

value of either (or both) the input and clock frequencies, as appropriate, is calculated for the

chosen record length.

The temperature of the integrated circuit being measured is set to the specified value.

The input and output terminals, as well as the remaining terminals, are connected as

specified. The power supplies and any other additional networks are connected as specified.

Unless otherwise specified, adjustments shall be made to minimize the offset and gain errors

as described in 15.1.4 of IEC 60748-4:1997.

60748-4-3 IEC:2006(E) – 15 –

The input signal is set to the specified amplitude and frequency, and the clock frequency is

set as specified.

All relevant control input signals shall be applied.

The record of the resulting output codes is stored for subsequent analysis. Where

appropriate, further records are obtained and stored for analysis. With multiple records,

accuracy is improved by using, for each frequency, the root mean square of the set of terms

for that frequency obtained from the Fourier Transform of each record.

5.1.3.5.1 Signal-to-noise-and-distortion ratio

The value of the signal-to-noise-and-distortion ratio is given by r.m.s. output signal/r.m.s.

residual signals.

X[]J

= (8)

SINAD

M

n= −1

X[]n

∑

n=2J

It is usually expressed as the ratio of their powers (output signal power/residual power),

where the signal power is obtained as below, and the residual power is calculated by one of

the methods below.

5.1.3.5.1.1 Signal power measurement

The amplitude and phase of the output at the input frequency (f) are obtained from the

i

Fourier Transform of the record(s) (see formulae given earlier). The r.m.s. output signal is

given by the amplitude of this component at f .

i

5.1.3.5.1.2 Residual power measurement – Method a

The instantaneous value of the output at the input frequency is calculated for each successive

sample in the record and subtracted from it.

The residual power is given by the mean of the squares of these differences.

5.1.3.5.1.3 Residual power measurement – Method b

The amplitude of each frequency is obtained from the Fourier Transform. The residual power

is given by the sum of the squares of all the terms after excluding the d.c. term and the term

for the input frequency (f ).

i

5.1.3.5.2 Signal-to-noise ratio

The value of signal-to-noise ratio is given by r.m.s. output signal/r.m.s. noise.

X[]J

SNR = (9)

M

n= −1

X[]n

∑

n=11.J

It is usually expressed as the ratio of their powers, where the noise power is obtained by one

of the methods below.

– 16 – 60748-4-3 IEC:2006(E)

5.1.3.5.2.1 Signal power measurement

The amplitude of the input frequency is obtained from the Fourier Transform and used to give

the value of signal power, as in 5.1.3.5.1.1, above.

5.1.3.5.2.2 Noise power measurement – Method a

The amplitude of each frequency is obtained from the Fourier Transform. The d.c. component,

the fundamental (f ) and the 2nd to 10th harmonics (unless otherwise specified) are excluded.

i

The noise power is given by the sum of the squares of all the remaining terms.

Harmonics higher than the 10th should also be excluded if their values are included in total

harmonic distortion (see 5.1.4.4.1).

5.1.3.5.2.3 Noise power measurement – Method b

The amplitude and phase of the fundamental and significant harmonic frequencies are

obtained from the Fourier Transform. Using the values given by the transform, these

frequencies are removed from the record by subtracting the instantaneous value of each from

each sample in the record to give the effective noise in each sample.

The noise power is given by the mean of the sum of the squares of these effective noise

samples.

5.1.3.5.2.4 Noise power measurement, Method c

Two separate records are obtained under identical conditions. The effective noise is the

difference, sample by sample, between the two records.

The noise power is given by the mean of the sum of the squares of the differences.

5.1.3.5.3 Noise floor

The noise floor may be obtained by either of the methods below. It is usually expressed as a

power relative to the power of a full-scale sine wave.

5.1.3.5.3.1 Noise floor – Method a

The noise spectrum in the output record is obtained by the method described in 5.1.3.5.2.2.

The noise floor, as a power, is given by the mean value of the sum of the squares of the noise

terms.

M

n= −1

X[]n

∑

n=11

NF = (10)

M

− 12

5.1.3.5.3.2 Noise floor – Method b

The effective noise in each sample of the record is obtained by the method in either

5.1.3.5.2.3 or 5.1.3.5.2.4, above, and the noise power is calculated.

The noise floor is given by the noise power divided by the square root of the number of

frequencies in the Fourier Transform that contribute to the noise power, i.e. the number of

samples less the number of significant components in the output spectrum.

60748-4-3 IEC:2006(E) – 17 –

M

[]x[]k − x[]k

∑ 1

k=1

NF =

M

−12

(11)

5.1.3.5.4 Effective number of bits

The effective number of bits should be obtained from the signal-to-noise-and-distortion ratio

with a full-scale input signal. However, it is usually measured with a smaller input signal and

the resulting ratio is then corrected by the ratio of the r.m.s. signal amplitude to the full-scale

range.

N is given by (signal-to-noise-and-distortion ratio – r.m.s. signal to full-scale ratio - crest

ef

factor of quantizing error + crest factor of test signal)/6.02,

where all the quantities are expressed in dB.

V

in

SINAD − − CF[]error + CF[signal]

V

FS

N = (12)

ef

6.02

5.1.3.6 Specified conditions

• Ambient or reference point temperature.

• Supply voltages.

• Input signal frequency, as appropriate.

• Input signal amplitude.

• Clock frequency, as appropriate.

• Highest harmonic excluded from noise, if not 10th.

• Conditions at other terminals.

5.1.4 Total harmonic distortion, spurious-free dynamic range, signal-dependent

timing error

5.1.4.1 Purpose

To measure the relative power of the harmonics caused by distortion of an input signal, to

determine the ratio of the output signal at the fundamental frequency to the largest signal at

any other single frequency, in the output of an ADC, and to determine the amount of error

related to the rate of change of the input.

5.1.4.2 Circuit diagram

See Figure 1.

5.1.4.3 Circuit description and requirements

The circuit description and requirements given in 5.1.1.3 are applicable for this measurement.

The input to the ADC being measured shall be a sinusoidal signal.

– 18 – 60748-4-3 IEC:2006(E)

5.1.4.4 Measurement procedure

The procedure in 5.1.3.5 is followed, and one or more output records obtained.

5.1.4.4.1 Total harmonic distortion

From the Fourier Transform of the output record, or the average of the transforms of multiple

records, the amplitude of the output signal at the fundamental frequency is obtained. The total

harmonic distortion is given by the square root of the sum of the squares of the amplitude of

each harmonic from the 2nd to the 10th (unless otherwise specified). See also 5.1.3.5.2.2 for

the exclusions.

The total harmonic distortion is given by r.m.s. harmonic components/r.m.s. signal.

X[]h

∑

h=2

THD = (13)

X[]1

5.1.4.4.2 Spurious-free dynamic range

The spectrum is analysed over the full range of interest to determine if there are spurious

frequencies present, i.e. at a level not attributable to noise alone.

From the Fourier Transform of the output record, or the average of the transforms of multiple

records, the amplitude of the output signal at the fundamental frequency is obtained. From all

the other frequencies present, the amplitude of the largest is noted.

The spurious-free dynamic range is given by the r.m.s. signal/r.m.s. largest single other

component.

X[]J

SFDR = (14)

M

n= −1

Max []X[]n

n=2

5.1.4.4.3 Signal-dependent timing error

The spurious-free dynamic range is measured over a range of frequencies in the region of the

cut-off frequency, using a constant input amplitude. The value of spurious-free dynamic range

divided by the frequency of measurement is recorded and the frequency at which this value is

a minimum is noted.

The signal-dependent timing error is given by the inverse of this frequency.

5.1.4.5 Specified conditions

• Ambient or reference point temperature.

• Supply voltages.

• Input signal frequency, as appropriate.

• Input signal amplitude.

• Clock frequency, as appropriate.

• Conditions at other terminals.

• Highest harmonic included, if not 10th.

60748-4-3 IEC:2006(E) – 19 –

5.1.5 Input overload recovery time, common-mode input overload recovery time

5.1.5.1 Purpose

To measure the time interval needed, after the removal of a signal input overload or a

common-mode input overload, for the ADC to return to its normal operating characteristics.

5.1.5.2 Circuit diagram

See Figure 1.

5.1.5.3 Circuit description and requirements

The circuit description and requirements given in 5.1.1.3 are applicable for this measurement.

The input to the ADC being measured shall be a sinusoidal signal, together with a step signal

for the overload pulse. For measurement of input overload recovery time, the step signal is

superimposed on the sinusoidal signal as a single-ended input signal and, for the common-

mode input recovery time, it is superimposed as a common-mode input signal.

The amplitude of the overload pulse shall not exceed the limiting value.

5.1.5.4 Measurement procedure

The number of samples in a record necessary to achieve the desired accuracy is calculated

as explained in the general requirements, and the exact value of either (or both) the input

frequency or the clock frequency, as appropriate, is calculated for the chosen record length.

The temperature of the integrated circuit being measured is set to the specified value.

The input and output terminals, as well as the remaining terminals, are connected as

specified. The power supplies and any other additional networks are connected as specified.

Unless otherwise specified, adjustments shall be made to minimize the offset and gain errors

as described in 15.1.4 of IEC 60748-4:1997.

The input signal is set to the specified amplitude and frequency, and the clock frequency is

set as specified. The amplitude and duration of the overload pulse are set as specified. All

relevant control input signals are then applied.

The overload pulse is applied part of the way through the test record.

Using the Fourier Transform, or otherwise, the best-fit amplitude and phase of the output at

the fundamental frequency are obtained from that part of the record before the overload pulse

is applied. The resulting sine wave is then extrapolated to the end of the record.

If the noise in the output could affect the accuracy, then the average, sample by sample, of

several records should be used for comparison with the extrapolated sine wave.

The input overload recovery time or the common-mode input overload recovery time, as

appropriate, is given by the time period from the end of the overload pulse to the point in the

record where the output samples no longer deviate from the extrapolated wave by more than

the specified tolerance.

– 20 – 60748-4-3 IEC:2006(E)

To check on the accuracy obtainable, the procedure above is repeated but without the

overload pulse. The deviation of the output samples from the extrapolated sine wave gives

the limit to the accuracy that may be obtained.

5.1.5.5 Specified conditions

• Ambient or reference point temperature.

• Supply voltages.

• Input signal frequency, as appropriate.

• Input signal amplitude.

• Overload signal amplitude.

• Overload signal duration.

• Clock frequency, as appropriate.

• Conditions at other terminals.

• Tolerance.

5.1.6 Limiting rate of change of output (slew rate), output transition times,

overshoot, settling time, settling error

5.1.6.1 Purpose

To measure the response of an ADC to a step input, i.e. to measure the maximum rate of

transition of the output, the output rise and/or fall time, the overshoot, the se

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...