IEC 61943:1999

(Main)Integrated circuits - Manufacturing line approval application guideline

Integrated circuits - Manufacturing line approval application guideline

Defines how to apply the principles and requirements given in IEC 61739 to monolithic integrated circuits. The standard is applicable to those manufacturers of integrated circuits (ICs) who apply for manufacturing line approval. The objective is to establish consistency in the requirements used by manufacturers and auditors for techniques related to integrated circuit manufacturing. Each manufacturer may use his own methods for satisfying the requirements of this standard, provided that the required level of control in the manufacturing line is reached.

Circuits intégrés - Guide d'application pour l'agrément des lignes de fabrication

Définit de quelle façon les principes et les exigences de la CEI 61739 sont appliqués aux circuits intégrés monolithiques. Elle est applicable aux fabricants de circuits intégrés (CI) qui demandent l'agrément d'une ligne de fabrication. L'objet de ce guide est d'établir la cohérence des exigences utilisées par les fabricants et les auditeurs pour les technologies liées à la fabrication de circuits intégrés. Chaque fabricant peut avoir ses propres méthodes pour satisfaire au contenu de la présente norme, pourvu que le niveau requis de contrôle de la ligne de fabrication soit atteint.

General Information

- Status

- Published

- Publication Date

- 18-Mar-1999

- Technical Committee

- SC 47A - Integrated circuits

- Drafting Committee

- WG 6 - TC 47/SC 47A/WG 6

- Current Stage

- PPUB - Publication issued

- Start Date

- 19-Mar-1999

- Completion Date

- 31-Mar-1999

Overview

IEC 61943:1999, titled Integrated Circuits - Manufacturing Line Approval Application Guideline, is an international standard developed by the International Electrotechnical Commission (IEC). This guideline specifies how to apply the principles and requirements set out in IEC 61739 specifically to monolithic integrated circuits (ICs). Its primary focus is providing a consistent framework for manufacturers applying for manufacturing line approval. The standard supports manufacturers and auditors by establishing uniform techniques and controls essential for maintaining high-quality integrated circuit production processes.

This standard offers a structured approach allowing each manufacturer flexibility in meeting the requirements, provided they achieve the necessary level of control in their manufacturing line. It ensures that manufacturing lines meet quality and procedural benchmarks critical for producing reliable integrated circuits.

Key Topics

IEC 61943:1999 covers comprehensive aspects of integrated circuit manufacturing with a detailed breakdown of tasks and procedures including:

- Scope and Definitions: Clarifies the application domain, terminologies, and normative references essential for understanding the guideline.

- Qualified Manufacturer List (QML) Approval Principles: Establishes criteria and procedures for manufacturers to qualify and be approved for manufacturing integrated circuits.

- Process and Design Tasks: Detailed descriptions of competencies, activities, interfaces, and subcontracting protocols across manufacturing line stages:

- Process design

- Integrated circuit design

- Wafer fabrication

- Process characterization

- Assembly and packaging

- Testing procedures

- Validation and Verification Procedures: Outlines methods for design verification, integration, validation, and quality control to ensure consistency and reliability.

- Interfaces and Subcontracting: Defines responsibilities and communication standards between different manufacturing stages and external partners.

- Quality Control Measures: Emphasizes adherence to strict quality guidelines as per IEC 61739 to maintain production integrity.

The standard features a modular structure reflecting the multifaceted nature of IC manufacturing, promoting systematic approval of each process stage.

Applications

IEC 61943:1999 is primarily targeted toward:

- Integrated Circuit Manufacturers: Assists manufacturers seeking approval of their production lines with clear-quality control and approval guidelines.

- Auditors and Quality Assurance Teams: Provides a consistent framework for auditing IC manufacturing lines ensuring compliance with international quality standards.

- Supply Chain Stakeholders: Facilitates effective subcontracting and ensures that subcontractors meet approved standards for various fabrication and assembly stages.

- Equipment and Process Designers: Guides design and validation activities central to wafer fabrication, packaging, and testing operations.

- Regulatory Bodies and Quality Certification Organizations: Use the standard as a benchmark for certification and qualification of IC manufacturing processes globally.

By adopting IEC 61943, manufacturers improve product quality, ensure regulatory compliance, and enhance customer confidence through approved manufacturing line processes.

Related Standards

- IEC 61739 – Integrated Circuits – Quality assessment of manufacturing lines: Provides the foundational principles and requirements that IEC 61943 applies specifically to monolithic ICs.

- IEC 60050 – International Electrotechnical Vocabulary: Defines general terminology relevant in electrotechnology and integrated circuit manufacturing.

- IEC 60027, 60417, 60617 – Standards for graphical and letter symbols used in electrical and electronic schematics, ensuring consistency in documentation and communication.

- IECQ System – IEC Quality Assessment System for Electronic Components, where IEC 61943 serves as a certification reference for quality assurance in IC manufacturing.

Conclusion

IEC 61943:1999 is a vital reference for integrated circuit manufacturers aiming to obtain manufacturing line approval consistent with internationally recognized quality and process standards. By providing detailed guidelines across design, fabrication, assembly, and test stages, it ensures manufacturing excellence and promotes worldwide standardization in IC production. Adherence to this standard results in enhanced quality control, process validation, and harmonized industry practices that benefit manufacturers and clients alike.

Frequently Asked Questions

IEC 61943:1999 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Integrated circuits - Manufacturing line approval application guideline". This standard covers: Defines how to apply the principles and requirements given in IEC 61739 to monolithic integrated circuits. The standard is applicable to those manufacturers of integrated circuits (ICs) who apply for manufacturing line approval. The objective is to establish consistency in the requirements used by manufacturers and auditors for techniques related to integrated circuit manufacturing. Each manufacturer may use his own methods for satisfying the requirements of this standard, provided that the required level of control in the manufacturing line is reached.

Defines how to apply the principles and requirements given in IEC 61739 to monolithic integrated circuits. The standard is applicable to those manufacturers of integrated circuits (ICs) who apply for manufacturing line approval. The objective is to establish consistency in the requirements used by manufacturers and auditors for techniques related to integrated circuit manufacturing. Each manufacturer may use his own methods for satisfying the requirements of this standard, provided that the required level of control in the manufacturing line is reached.

IEC 61943:1999 is classified under the following ICS (International Classification for Standards) categories: 31.200 - Integrated circuits. Microelectronics. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61943:1999 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE IEC

INTERNATIONAL

QC 211001

STANDARD

Première édition

First edition

1999-03

Circuits intégrés –

Guide d'application pour l'agrément

des lignes de fabrication

Integrated circuits –

Manufacturing line approval

application guideline

Numéro de référence

Reference number

CEI/IEC 61943:1999

Numéros des publications Numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60 000. issued with a designation in the 60 000 series.

Publications consolidées Consolidated publications

Les versions consolidées de certaines publications de Consolidated versions of some IEC publications

la CEI incorporant les amendements sont disponibles. including amendments are available. For example,

Par exemple, les numéros d’édition 1.0, 1.1 et 1.2 edition numbers 1.0, 1.1 and 1.2 refer, respectively, to

indiquent respectivement la publication de base, la the base publication, the base publication incor-

publication de base incorporant l’amendement 1, et porating amendment 1 and the base publication

la publication de base incorporant les amendements 1 incorporating amendments 1 and 2.

et 2.

Validité de la présente publication Validity of this publication

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. the content reflects current technology.

Des renseignements relatifs à la date de re- Information relating to the date of the reconfirmation

confirmation de la publication sont disponibles dans of the publication is available in the IEC catalogue.

le Catalogue de la CEI.

Les renseignements relatifs à des questions à l’étude et Information on the subjects under consideration and

des travaux en cours entrepris par le comité technique work in progress undertaken by the technical com-

qui a établi cette publication, ainsi que la liste des mittee which has prepared this publication, as well as

publications établies, se trouvent dans les documents the list of publications issued, is to be found at the

ci-dessous: following IEC sources:

• «Site web» de la CEI*

• IEC web site*

• Catalogue des publications de la CEI

• Catalogue of IEC publications

Publié annuellement et mis à jour

Published yearly with regular updates

régulièrement

(On-line catalogue)*

(Catalogue en ligne)*

• IEC Bulletin

• Bulletin de la CEI

Available both at the IEC web site* and

Disponible à la fois au «site web» de la CEI*

as a printed periodical

et comme périodique imprimé

Terminologie, symboles graphiques Terminology, graphical and letter

et littéraux symbols

En ce qui concerne la terminologie générale, le lecteur For general terminology, readers are referred to

se reportera à la CEI 60050: Vocabulaire Electro- IEC 60 050: International Electrotechnical Vocabulary

technique International (VEI). (IEV).

Pour les symboles graphiques, les symboles littéraux For graphical symbols, and letter symbols and signs

et les signes d'usage général approuvés par la CEI, le approved by the IEC for general use, readers are

lecteur consultera la CEI 60027: Symboles littéraux à referred to publications IEC 60027: Letter symbols to

utiliser en électrotechnique, la CEI 60417: Symboles be used in electrical technology, IEC 60417: Graphical

graphiques utilisables sur le matériel. Index, relevé et symbols for use on equipment. Index, survey and

compilation of the single sheets and IEC 60617:

compilation des feuilles individuelles, et la CEI 60617:

Symboles graphiques pour schémas. Graphical symbols for diagrams.

* Voir adresse «site web» sur la page de titre. * See web site address on title page.

NORME CEI

INTERNATIONALE IEC

INTERNATIONAL

QC 211001

STANDARD

Première édition

First edition

1999-03

Circuits intégrés –

Guide d'application pour l'agrément

des lignes de fabrication

Integrated circuits –

Manufacturing line approval

application guideline

IEC 1999 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in

utilisée sous quelque forme que ce soit et par aucun procédé, any form or by any means, electronic or mechanical,

électronique ou mécanique, y compris la photo-copie et les including photocopying and microfilm, without permission in

microfilms, sans l'accord écrit de l'éditeur. writing from the publisher.

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland

Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http://www.iec.ch

CODE PRIX

Commission Electrotechnique Internationale

T

PRICE CODE

International Electrotechnical Commission

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 61943 CEI:1999

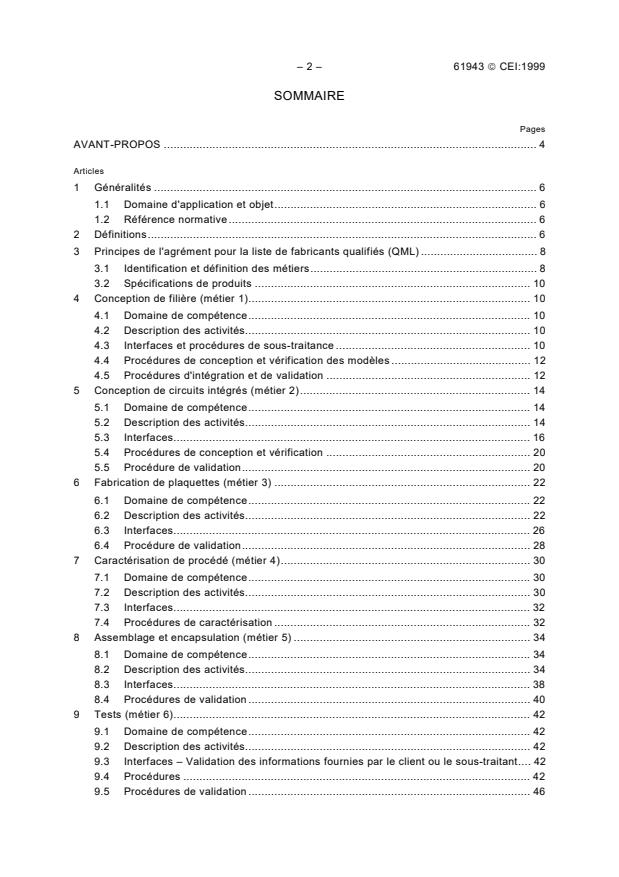

SOMMAIRE

Pages

AVANT-PROPOS . 4

Articles

1 Généralités . 6

1.1 Domaine d'application et objet. 6

1.2 Référence normative. 6

2 Définitions. 6

3 Principes de l'agrément pour la liste de fabricants qualifiés (QML) . 8

3.1 Identification et définition des métiers. 8

3.2 Spécifications de produits . 10

4 Conception de filière (métier 1). 10

4.1 Domaine de compétence. 10

4.2 Description des activités. 10

4.3 Interfaces et procédures de sous-traitance . 10

4.4 Procédures de conception et vérification des modèles . 12

4.5 Procédures d'intégration et de validation . 12

5 Conception de circuits intégrés (métier 2). 14

5.1 Domaine de compétence. 14

5.2 Description des activités. 14

5.3 Interfaces. 16

5.4 Procédures de conception et vérification . 20

5.5 Procédure de validation. 20

6 Fabrication de plaquettes (métier 3) . 22

6.1 Domaine de compétence. 22

6.2 Description des activités. 22

6.3 Interfaces. 26

6.4 Procédure de validation. 28

7 Caractérisation de procédé (métier 4). 30

7.1 Domaine de compétence. 30

7.2 Description des activités. 30

7.3 Interfaces. 32

7.4 Procédures de caractérisation . 32

8 Assemblage et encapsulation (métier 5) . 34

8.1 Domaine de compétence. 34

8.2 Description des activités. 34

8.3 Interfaces. 38

8.4 Procédures de validation . 40

9 Tests (métier 6). 42

9.1 Domaine de compétence. 42

9.2 Description des activités. 42

9.3 Interfaces – Validation des informations fournies par le client ou le sous-traitant. 42

9.4 Procédures . 42

9.5 Procédures de validation . 46

61943 IEC:1999 – 3 –

CONTENTS

Page

FOREWORD . 5

Clause

1 General. 7

1.1 Scope and object . 7

1.2 Normative reference. 7

2 Definitions. 7

3 Principles for qualified manufacturer list (QML) approval. 9

3.1 Identification and definition of tasks. 9

3.2 Product specifications . 11

4 Process design (task 1). 11

4.1 Field of application . 11

4.2 Description of activities . 11

4.3 Interfaces and subcontracting procedures . 11

4.4 Procedures for design and verification of models. 13

4.5 Procedures for integration and validation. 13

5 Integrated circuits design (task 2). 15

5.1 Field of application . 15

5.2 Description of activities . 15

5.3 Interfaces. 17

5.4 Procedures for design and verification. 21

5.5 Validation procedure . 21

6 Wafer fabrication (task 3) . 23

6.1 Field of application . 23

6.2 Description of activities . 23

6.3 Interfaces. 27

6.4 Validation procedure . 29

7 Process characterization (task 4). 31

7.1 Field of application . 31

7.2 Description of activities . 31

7.3 Interfaces. 33

7.4 Characterization procedures. 33

8 Assembly and packaging (task 5) . 35

8.1 Field of application . 35

8.2 Description of activities . 35

8.3 Interfaces. 39

8.4 Validation procedures. 41

9 Tests (task 6).43

9.1 Field of application . 43

9.2 Description of activities . 43

9.3 Interfaces – Validation of information provided by the customer or subcontractor . 43

9.4 Procedures . 43

9.5 Validation procedures. 47

– 4 – 61943 CEI:1999

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

___________

CIRCUITS INTÉGRÉS – GUIDE D'APPLICATION POUR L'AGRÉMENT

DES LIGNES DE FABRICATION

AVANT-PROPOS

1) La CEI (Commission Electrotechnique Internationale) est une organisation mondiale de normalisation composée

de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a pour objet de

favoriser la coopération internationale pour toutes les questions de normalisation dans les domaines de

l'électricité et de l'électronique. A cet effet, la CEI, entre autres activités, publie des Normes internationales.

Leur élaboration est confiée à des comités d'études, aux travaux desquels tout Comité national intéressé par le

sujet traité peut participer. Les organisations internationales, gouvernementales et non gouvernementales, en

liaison avec la CEI, participent également aux travaux. La CEI collabore étroitement avec l'Organisation

Internationale de Normalisation (ISO), selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible un accord international sur les sujets étudiés, étant donné que les Comités nationaux intéressés

sont représentés dans chaque comité d’études.

3) Les documents produits se présentent sous la forme de recommandations internationales. Ils sont publiés

comme normes, rapports techniques ou guides et agréés comme tels par les Comités nationaux.

4) Dans le but d'encourager l'unification internationale, les Comités nationaux de la CEI s'engagent à appliquer de

façon transparente, dans toute la mesure possible, les Normes internationales de la CEI dans leurs normes

nationales et régionales. Toute divergence entre la norme de la CEI et la norme nationale ou régionale

correspondante doit être indiquée en termes clairs dans cette dernière.

5) La CEI n’a fixé aucune procédure concernant le marquage comme indication d’approbation et sa responsabilité

n’est pas engagée quand un matériel est déclaré conforme à l’une de ses normes.

6) L’attention est attirée sur le fait que certains des éléments de la présente Norme internationale peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 61943 a été établie par le sous-comité 47A: Circuits intégrés, du

comité d'études 47 de la CEI: Dispositifs à semiconducteurs.

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

47A/533/FDIS 47A/546/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

Le numéro QC qui figure sur la page de couverture de la présente publication est le numéro de

spécification dans le Système CEI d'assurance de la qualité des composants électroniques

(IECQ).

61943 IEC:1999 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

INTEGRATED CIRCUITS – MANUFACTURING LINE APPROVAL

APPLICATION GUIDELINE

FOREWORD

1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, the IEC publishes International Standards. Their preparation is

entrusted to technical committees; any IEC National Committee interested in the subject dealt with may

participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization

for Standardization (ISO) in accordance with conditions determined by agreement between the two

organizations.

2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has representation

from all interested National Committees.

3) The documents produced have the form of recommendations for international use and are published in the form

of standards, technical reports or guides and they are accepted by the National Committees in that sense.

4) In order to promote international unification, IEC National Committees undertake to apply IEC International

Standards transparently to the maximum extent possible in their national and regional standards. Any

divergence between the IEC Standard and the corresponding national or regional standard shall be clearly

indicated in the latter.

5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with one of its standards.

6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject

of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61943 has been prepared by subcommittee 47A: Integrated circuits,

of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

FDIS Report on voting

47A/533/FDIS 47A/546/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

The QC number that appears on the front cover of this publication is the specification number

in the IEC Quality Assessment System for Electronic Components (IECQ).

– 6 – 61943 CEI:1999

CIRCUITS INTÉGRÉS – GUIDE D'APPLICATION POUR L'AGRÉMENT

DES LIGNES DE FABRICATION

1 Généralités

1.1 Domaine d'application et objet

La présente norme internationale définit de quelle façon les principes et les exigences de la

CEI 61739 sont appliqués aux circuits intégrés monolithiques. Elle est applicable aux

fabricants de circuits intégrés (CI) qui demandent l'agrément d'une ligne de fabrication.

L'objet de ce guide est d'établir la cohérence des exigences utilisées par les fabricants et les

auditeurs pour les technologies liées à la fabrication de circuits intégrés.

Chaque fabricant peut avoir ses propres méthodes pour satisfaire au contenu de la présente

norme, pourvu que le niveau requis de contrôle de la ligne de fabrication soit atteint.

1.2 Référence normative

Le document normatif suivant contient des dispositions qui, par suite de la référence qui y est

faite, constitue des dispositions valables pour la présente Norme internationale. Pour les

références datées, les amendements ultérieurs ou les révisions de ces publications ne

s’appliquent pas. Toutefois, les parties prenantes aux accords fondés sur la présente Norme

internationale sont invitées à rechercher la possibilité d'appliquer l'édition la plus récente du

document normatif indiqué ci-après. Pour les références non datées, la dernière édition

du document normatif en référence s’applique. Les membres de la CEI et de l'ISO possèdent

le registre des Normes internationales en vigueur.

CEI 61739:1996, Circuits intégrés – Procédures pour l'agrément d'une ligne de fabrication et la

gestion de la qualité

2 Définitions

Pour les besoins de la présente norme, les définitions suivantes, tirées de la CEI 61739,

s'appliquent:

2.1

véhicule de démonstration

produit ordinaire ou produit spécialement conçu pour démontrer que tous les paramètres

critiques du process sont sous contrôle et reproductibles dans la technologie considérée

2.2

moniteur paramétrique (PM)

structure pour mesurer les paramètres électriques

2.3

liste de fabricants qualifiés (QML)

liste utilisée pour la procédure associée à l'Agrément de Ligne de Fabrication tel que défini

dans la CEI 61739

61943 IEC:1999 – 7 –

INTEGRATED CIRCUITS – MANUFACTURING LINE APPROVAL

APPLICATION GUIDELINE

1 General

1.1 Scope and object

This International Standard defines how to apply the principles and requirements given in

IEC 61739 to monolithic integrated circuits. The standard is applicable to those manufacturers

of integrated circuits (ICs) who apply for manufacturing line approval.

The objective of this applicators guideline is to establish consistency in the requirements used

by manufacturers and auditors for techniques related to integrated circuit manufacturing.

Each manufacturer may use his own methods for satisfying the requirements of this standard,

provided that the required level of control in the manufacturing line is reached.

1.2 Normative reference

The following normative document contains provisions which, through reference in this text,

constitute provisions of this International Standard. For dated references, subsequent

amendments to, or revisions of, this publication do not apply. However, parties to agreements

based on this International Standard are encouraged to investigate the possibility of applying

the most recent editions of the normative document indicated below. For undated references,

the latest edition of the normative document referred to applies. Members of IEC and ISO

maintain registers of currently valid International Standards.

IEC 61739:1996, Integrated circuits – Procedures for manufacturing line approval and quality

management

2 Definitions

For the purpose of this Guideline the following definitions apply (see 1.4 of IEC 61739):

2.1

demonstration vehicle

normal product or product specifically designed to demonstrate that all critical process

parameters are under control and repeatable within the defined technology

2.2

parametric monitor (PM)

structure for measuring electrical parameters

2.3

qualified manufacturer list QML

list used for the procedure associated with manufacturing line approval as defined in

IEC 61739

– 8 – 61943 CEI:1999

2.4

composant d'évaluation standard (SEC)

structure utilisée pour piloter le procédé de fabrication, et pour servir de produit de substitution

pour les essais de fiabilité et l'évaluation du taux de défaillance. Il peut être un produit normal

de la technologie considérée

2.5

tâche

activité ou suite d'activités qui forme une étape dans la fabrication du produit

2.6

véhicule technologique (TV)

structure hybride qui démontre la reproductibilité du procédé et des caractéristiques associées

2.7

véhicule de caractérisation technologique (TCV)

structure pour étudier les mécanismes de défaillance intrinsèque et leur répartition

2.8

bureau de révision technologique (TRB) ou organisation équivalente

organisation fondamentale pour la ligne de fabrication ou la tâche. Un TRB sera formé de

représentants de toutes les fonctions décrites dans le plan de gestion totale de la qualité (TQM, total

quality management) telles que le marketing, les ventes, la conception, le développement de

technologie, la fabrication, les essais et l'assurance de la qualité, quand elles s'appliquent

3 Principes de l'agrément pour la liste de fabricants qualifiés (QML)

Les fabricants figurant dans la liste de fabricants qualifiés (QML) doivent être capables de

produire des produits issus d'une ligne de fabrication agréée, sans qu'il soit nécessaire

d'effectuer des essais de qualification approfondis, et des inspections de conformité à la

qualité en fin de fabrication sur chaque produit.

L'organisation initiale de contrôle de la ligne de fabrication qualifiée doit être le bureau de

révision technologique (TRB) ou toute organisation équivalente.

Le fabricant en cours de qualification doit certifier et avoir les documents prouvant que tout

métier exécuté par un sous-traitant est conforme aux exigences de la CEI 61739.

Au fur et à mesure de l'évolution de la technologie et que les données de qualité et de fiabilité

sont accumulées, le fabricant, à travers le plan TQM et le TRB, peut modifier, substituer ou

supprimer des essais et/ou des sélections. L'organisme national de surveillance (ONS) doit

être prévenu de telles actions par le rapport statutaire.

3.1 Identification et définition des métiers

Ce guide identifie six métiers avec les interfaces qui détaillent les exigences spécifiques pour

les cycles de conception et de fabrication des circuits intégrés (CI).

3.1.1 Conception de filière (voir article 4)

Il s'agit de la conception d'une filière de semiconducteur comprenant les modifications et la

publication des paramètres de la filière, ainsi que des règles correspondantes de conception

de la filière, transcrits sous forme de textes écrits ou de fichiers informatiques.

61943 IEC:1999 – 9 –

2.4

standard evaluation component (SEC)

structure used to monitor the fabrication process and to serve as a surrogate product for

reliability testing and failure rate evaluation. It can be an actual device of the technology under

consideration

2.5

task

activity or sequence of activities that form a stage in manufacturing the product

2.6

technological vehicle (TV)

hybrid structure that demonstrates process repeatability and involved characteristics

2.7

technology characterization vehicle (TCV)

structure to study intrinsic failure mechanisms and their distribution

2.8

technology review board (TRB) or equivalent organization

primary organization for the manufacturing line or task. A TRB will consist of representatives of

all functions described in total quality management (TQM) Plan, such as marketing, sales,

design, technology development, fabrication, testing and quality assurance as applicable

3 Principles for qualified manufacturer list (QML) approval

QML listed manufacturers shall be able to produce products utilizing an approved manu-

facturing line without the need for extensive qualification testing and end-of-manufacturing

quality conformance inspections on each product.

The primary organization for control of the qualified manufacturing line shall be the TRB or

equivalent organization.

The qualifying manufacturer shall ensure and document that any tasks to be performed by a

subcontractor meet the requirements of IEC 61739.

As the technology matures and reliability and quality data are accumulated, the manufacturer,

through the total quality management (TQM) plan and technology review board (TRB) may

modify, substitute or delete tests and/or screens. The national supervising inspectorate (NSI)

shall be notified of such actions through the status report.

3.1 Identification and definition of tasks

This guideline identifies six tasks with interfaces which detail the specific requirements for the

design and manufacturing of ICs.

3.1.1 Process design (see clause 4)

This is the design of the semiconductor process including modification and publication of the

process parameters and related process design rules in the form of written text and/or

computer files.

– 10 – 61943 CEI:1999

3.1.2 Conception de CI (voir article 5)

Il s'agit de la conception de circuits intégrés conformément aux exigences des clients, comme

défini par les spécifications de produit ou autres.

3.1.3 Fabrication des plaquettes (voir article 6)

Il s'agit de la réalisation physique de CI sur des substrats sous TQM.

3.1.4 Caractérisation de procédé (voir article 7)

La caractérisation de procédé est l'extraction de toutes les informations nécessaires pour

confirmer la conception de filière.

3.1.5 Assemblage et encapsulation (voir article 8)

Cela inclut les opérations depuis la réception des plaquettes (ou des puces) jusqu'à la livraison

de produits encapsulés.

3.1.6 Essais (voir article 9)

Ce sont les essais de conformité aux spécifications.

3.2 Spécifications de produits

Pour les produits standard ou catalogue, les fabricants doivent publier les spécifications

établissant les procédés de fabrication utilisés. Ils doivent également conserver un

enregistrement des produits avec leur ONS. De telles spécifications peuvent être des

spécifications particulières enregistrées par la CEI ou des feuilles de fabricant publiées.

La spécification CI du client ne peut être publiée que lorsqu'elle est approuvée conjointement

par le fournisseur et le client.

4 Conception de filière (métier 1)

4.1 Domaine de compétence

Le système de gestion de la qualité doit être totalement décrit. Le centre de conception de

filière doit être responsable de la gestion de la qualité, et doit avoir mis en place l'organisation

nécessaire, y compris la mise en place d'un TRB et des outils nécessaires. Le fabricant doit

être capable de prouver cela à la satisfaction de l'ONS avec des résultats objectifs.

4.2 Description des activités

Le fabricant doit définir et documenter les procédures et les activités du centre de conception

de filière, y compris les règles de conception et les sorties, l'archivage, la vérification et la

validation.

4.3 Interfaces et procédures de sous-traitance

4.3.1 Interfaces avec le client

Les exigences sur les interfaces avec le client et les procédures doivent être décrites.

61943 IEC:1999 – 11 –

3.1.2 IC design (see clause 5)

This is the design of integrated circuits in accordance with customer requests as defined by

product or other specifications.

3.1.3 Wafer fabrication (see clause 6)

This is the physical realization of ICs on substrates under TQM.

3.1.4 Process characterization (see clause 7)

Process characterization is the extraction of all the information required to confirm the process

design.

3.1.5 Assembly and packaging (see clause 8)

This includes a series of operations from receipt of wafers or chips to supply of packaged

products.

3.1.6 Test (see clause 9)

This is verification of conformance to specifications.

3.2 Product specifications

For standard or catalog products, manufacturers shall publish specifications stating what

processes are employed. They shall also maintain a register of products with their NSI. Such

specifications may be any registered IEC detail specification (DS) or any published

manufacturer’s data sheet.

A custom IC specification may be published only upon agreement between the supplier and

customer.

4 Process design (task 1)

4.1 Field of application

The system of process design quality management shall be fully documented. The process

design center shall be responsible for the management of quality and shall have established

the necessary organization, including a TRB and tools for this purpose. The supplier shall be

able to so demonstrate to the satisfaction of the NSI with objective results.

4.2 Description of activities

The manufacturer shall define and document procedures and activities of the process design

center, including design rules and outputs, archiving, verification and validation.

4.3 Interfaces and subcontracting procedures

4.3.1 Customer interfaces

Customer interface requirements and procedures shall be documented.

– 12 – 61943 CEI:1999

4.3.2 Sous-traitance

La sous-traitance d'une quelconque activité doit être conforme aux exigences de la QML.

4.3.3 Fabrication de masques ou activité équivalente (si applicable)

Tous les fabricants de masques approuvés par le centre de conception de filière doivent être

identifiés.

4.3.4 Laboratoires d'essai

Lorsque des laboratoires d'essai extérieurs sont employés, leur identification, le domaine

d'activité et les limites de capabilité, ainsi que les qualifications doivent être décrites.

4.3.5 Fonderies de fabrication de plaquettes

Le centre de conception de filière doit établir la liste de toutes les fonderies pour lesquelles il

conçoit une filière, ainsi que l'identification des filières pour chacune d'entre elles.

Leurs qualifications doivent être détaillées, ainsi que les procédures, spécifications et

exigences d'interface, y compris l'identification des règles de conception correspondantes, les

véhicules de test, la caractérisation de filière et les méthodes de contrôle et les résultats, les

dimensions critiques ainsi que les spécifications de transfert de filière.

4.3.6 Assemblage/encapsulation

Toutes les exigences particulières pour l'assemblage et l'encapsulation doivent être détaillées

dans les règles de conception.

4.4 Procédures de conception et vérification des modèles

Les procédures pour la création, la vérification et la validation, aussi bien que l'intégration des

règles de conception et des éléments de librairie, doivent être établies pour chaque outil

qualifié.

4.4.1 Création

Les descriptions des filières pour la création et l'installation de nouveaux éléments de librairies

(et de blocs, cellules, réseaux, etc.) doivent être documentés dans les manuels de conception

applicables pour les librairies, la topologie et la conception de circuit.

4.4.2 Vérification

Les procédures utilisées pour la vérification et la validation des caractéristiques, ainsi que les

règles d'application pour les éléments de librairies doivent être spécifiées.

4.5 Procédures d'intégration et de validation

4.5.1 Intégration

La méthodologie mise en oeuvre pour vérifier, valider et intégrer un nouvel élément de librairie

doit être spécifiée. Elle précise les outils, le mode opératoire, et les procédures d'assurance de

la qualité associées au procédé décrit.

61943 IEC:1999 – 13 –

4.3.2 Subcontracting

Subcontracting of any work shall comply with the requirements of the QML.

4.3.3 Mask making or equivalent activity (if applicable)

All mask makers approved by the process design center shall be identified.

4.3.4 Test laboratories

Where external test laboratories are employed, their identification, scope and limits of

capability and qualifications shall be documented.

4.3.5 Wafer-fabricant

The process design center shall list all wafer-fabricants for which they design processes,

together with identification of the processes for each of these.

The qualifications of each wafer-fabricant shall be documented together with the procedures,

specifications and interface requirements. This shall include identification of the relevant

design rules, test vehicles, process characterization and control methods and results, critical

dimensions, and process transfer specifications.

4.3.6 Assembly/packaging

All requirements for assembly/packaging shall be detailed in the design rules.

4.4 Procedures for design and verification of models

The procedures for creation, verification and validation, as well as the integration of design

rules and library elements, shall be stated for each tool qualified.

4.4.1 Creation

Descriptions of the processes for creation and installation of new library elements (and blocks,

cells, arrays, etc.) shall be documented in the applicable design manuals for library, layout, and

circuit design.

4.4.2 Verification

The procedures employed for verification and validation of characteristics and application rules

for library elements shall be specified.

4.5 Procedures for integration and validation

4.5.1 Integration

The methodology used to verify, validate and integrate a new library element shall be specified.

It identifies the tools, the operating mode and the quality assurance procedures related to the

described process.

– 14 – 61943 CEI:1999

4.5.2 Validation

Le centre de conception doit spécifier la méthode et les outils qui permettent de comparer les

résultats de la simulation du schéma extrait du routage (simulation de transfert) à ceux de la

simulation logique de l'élément de librairie en réponse aux vecteurs de test.

Enfin, il doit être précisé comment et sur quels éléments est vérifiée l'exactitude des

caractéristiques temporelles, et comment sont recoupés les résultats de simulations analo-

giques sur chemins critiques, avec ceux des simulations logico-temporelles après routage.

5 Conception de circuits intégrés (métier 2)

5.1 Domaine de compétence

Le métier 2 inclut l'ensemble des informations qui définissent le savoir-faire revendiqué et

définit le type de circuits pour lesquels le centre de conception s'estime compétent, en

précisant:

– la classe de circuits réalisables (analogique, logique, mixte);

– le ou les matériaux semi-conducteurs: silicium, AsGa;

– les filières technologiques: MOS, MOS/SOS, bipolaire;

– les technologies: analogique, I2L, logique à émetteur couplé (ECL);

– les méthodes d'assemblage;

– les encapsulations.

Le centre de conception définit les documents qui initialisent son activité et qui indiquent

comment les résultats sont décrits et documentés, ainsi que les métiers qui doivent être sous-

traîtés.

5.2 Description des activités

Le présent paragraphe comprend un ou plusieurs diagrammes de cheminement décrivant

toutes les étapes de l'activité du centre de conception, y compris:

– la spécification technique de besoin;

– le dossier de spécification des blocs;

– le dossier d'étude de blocs;

– le dossier d'intégration précisant les contraintes de placement et de routage;

– les simulations;

– les schémas et la liste de liens;

– le résultat des extractions des topologies;

– les simulations après routage;

– le dossier de justification;

– le dossier de conception comprenant les documents et outillages utiles à:

• la fabrication des masques pour le circuit intégré;

• l'assemblage et l'encapsulation;

• l'ingénierie et la réalisation des essais;

• l'évaluation des prototypes;

61943 IEC:1999 – 15 –

4.5.2 Validation

The design center shall specify the methods and tools used to compare the simulation results

of the schematic issued from layout (switch simulation) with the logic simulation results of the

library element, in response to the test vectors.

It shall also describe how and which elements are used to check the accuracy of the dynamic

characteristics, and how they are compared and correlated to the analog simulation results on

critical paths with the logical dynamic simulations after layout.

5 Integrated circuits design (task 2)

5.1 Field of application

Task 2 involves all information which defines the claimed capability and defines the type of

circuits for which the center claims competence. Details are given on:

– class of circuits covered (analog, digital, mixed function);

– semiconductor material(s): GaAs, Si;

– process: MOS, MOS/SOS, bipolar;

– technologies (analog, I2L, emitter coupled logic (ECL));

– assembly methods;

– packaging.

The design center defines the documents which initialize the activity and which show how the

results are described and documented as well as what tasks are to be subcontracted.

5.2 Description of activities

This subclause describes one or more flows covering all the steps of the design work

undertaken by the design center, including:

– the technical need specification;

– the blocks specification file;

– the blocks study file;

– the integration file describing the place and route constraints;

– simulations;

– schematics and netlist;

– layout extraction results;

– postrouting simulation;

– the justification file;

– the design file which includes documents and tools dedicated to:

• mask/reticle tooling for the IC;

• assembly and packaging;

• engineering and test production;

• prototype evaluation;

– 16 – 61943 CEI:1999

• la validation du programme d'essai;

• les enregistrements de résultats de test;

• les procédures d'analyse de défaillance;

• les procédures d'analyse de non-conformité;

• la spécification technique du produit;

• les procédures de mise à disposition;

• les procédures d'archivage et de suivi;

• les procès-verbaux de revues de spécification, de conception et de fin de conception.

5.3 Interfaces

5.3.1 Interface avec la conception CAO de filière

L'accent est mis sur les points suivants:

– gestion de la mise à jour de la configuration logicielle et des librairies;

– compatibilité ascendante;

– documentation;

– traçabilité;

– limites d'utilisation (précision des modèles);

– utilisation des outils de vérification: contrôle des règles de dessin (DRC), contrôle des

règles électriques (ERC), vérification de l'implantation par rapport au schéma (LVS).

5.3.2 Interface avec le client

Le centre de conception définit sa politique quant à la participation du client aux diverses

phases suivantes de l'activité de conception:

– rédaction de la spécification technique de besoin;

– conception;

– simulation fonctionnelle;

– simulation orientée test;

– placement et routage;

– caractérisation et évaluation des prototypes.

Il est de la responsabilité du centre de conception de s'assurer que les règles de conception et

de réalisation propres à la filière concernée sont bien respectées. Il est pareillement de la

responsabilité du centre de conception de vérifier que la méthodologie d'essai mise en oeuvre

permet de satisfaire à toutes les exigences de la spécification technique de besoin.

5.3.3 Masques/outillage

Le centre de conception établit la liste des fabricants de masques. Pour chacun des fabricants

de masques, le centre fournira les informations suivantes:

– le nom,

– l’adresse, et

– le type d'outillage fabriqué.

61943 IEC:1999 – 17 –

• test program validation;

• test results records;

• failure analysis procedures;

• nonconformance analysis procedure;

• the technical specification of the product;

• release procedures;

• recording and f

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...