IEC 60749-29:2003

(Main)Semiconductor devices - Mechanical and climatic test methods - Part 29: Latch-up test

Semiconductor devices - Mechanical and climatic test methods - Part 29: Latch-up test

Covers the I-test and the overvoltage latch-up testing of integrated circuits. The purpose of this test is to establish a method for determining integrated circuit latch-up characteristics and to define latch-up failure criteria. Latch-up characteristics are used in determining product reliability and minimizing "No Trouble Found" and "Electrical Overstress" failures due to latch-up.

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques - Partie 29: Essai de verrouillage

Couvre l'essai I et les essais de verrouillage de surtension des circuits intégrés. L'objet de cet essai est d'établir une méthode pour déterminer les caractéristiques de verrouillage des circuits intégrés et définir les critères de défaillance de verrouillage. Les caractéristiques de verrouillage sont utilisées dans la détermination de la fiabilité de produit et la minimisation des défaillances en rapport avec «l'absence d'observation de problèmes» et la «contrainte électrique excessive» du fait du verrouillage.

General Information

- Status

- Published

- Publication Date

- 03-Nov-2003

- Technical Committee

- TC 47 - Semiconductor devices

- Drafting Committee

- WG 2 - TC 47/WG 2

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 07-Apr-2011

- Completion Date

- 14-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 60749-29:2003 - Semiconductor devices - Mechanical and climatic test methods - Part 29: Latch-up test is an international standard developed by the International Electrotechnical Commission (IEC). This standard provides a systematic method for performing latch-up tests on integrated circuits (ICs), specifically focusing on I-test and overvoltage latch-up testing. Its primary goal is to determine integrated circuit latch-up characteristics and establish latch-up failure criteria. The results from this testing are crucial for assessing product reliability, reducing "No Trouble Found" (NTF) events, and minimizing "Electrical Overstress" (EOS) failures caused by latch-up effects.

This test method is especially applicable to CMOS devices but can be applied to other semiconductor technologies after establishing suitability.

Key Topics

- Latch-up Phenomenon: Latch-up is an unwanted, low-impedance path in a semiconductor device resulting from electrical overstress, potentially leading to device failure.

- Test Classifications:

- Class I: Testing at room temperature.

- Class II: Testing at the device's maximum rated ambient temperature.

- I-test and Overvoltage Test: Procedures for subjecting device input, output, and power supply pins to current or voltage pulses, in order to induce and detect latch-up.

- Test Equipment: Specification for latch-up testers and test setups, including requirements for dynamic device testing, appropriate timing signals, and logic vectors.

- Failure Criteria: Defines conditions under which a device is considered to have failed the latch-up test, with Level A based on standard criteria and Level B allowing for application-specific definitions.

- Test Conditions & Definitions: Clarifies terminology such as device under test (DUT), supply currents, trigger pulses, and test parameters essential for repeatable and reliable latch-up testing.

Applications

The practical value of IEC 60749-29:2003 extends across several aspects of semiconductor device development and manufacturing:

- Reliability Qualification: Ensures that ICs can withstand latch-up under specified electrical conditions, critical for devices in demanding or sensitive applications.

- Failure Prevention: By defining clear criteria and systematic testing methods, the standard helps manufacturers minimize latent failures due to latch-up, thereby lowering warranty returns and field failures.

- Design Validation: Device designers use IEC 60749-29 results to improve latch-up immunity in future product generations, leading to more robust electronics.

- Quality Assurance in Production: Production test departments incorporate latch-up testing as part of quality checks for outgoing semiconductor components.

- Customer Confidence and Regulatory Compliance: Conformance to recognized IEC standards facilitates market access and customer acceptance, especially in automotive, industrial, and high-reliability sectors.

Related Standards

For a comprehensive approach to semiconductor device reliability and testing, consider the following related standards:

- IEC 60749 Series: Covers a range of mechanical and climatic test methods for semiconductor devices.

- IEC 60749-1: General guidance and definitions for the 60749 semiconductor test series.

- IEC/PAS 62181: The predecessor to IEC 60749-29, now replaced by this standard.

- JEDEC JESD78: An industry-recognized standard for latch-up testing of CMOS devices.

- IEC 60068 Series: General test procedures for environmental testing of electronic equipment.

Conclusion

IEC 60749-29:2003 delivers an internationally harmonized method for evaluating the latch-up resistance of integrated circuits, offering standardized guidance to manufacturers, designers, and test engineers. Consistent application of this standard ensures improved product reliability and supports both compliance and competitive advantage in the global semiconductor marketplace. For more information, or to acquire the full standard, visit the IEC website or the relevant national standards organization.

Frequently Asked Questions

IEC 60749-29:2003 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Mechanical and climatic test methods - Part 29: Latch-up test". This standard covers: Covers the I-test and the overvoltage latch-up testing of integrated circuits. The purpose of this test is to establish a method for determining integrated circuit latch-up characteristics and to define latch-up failure criteria. Latch-up characteristics are used in determining product reliability and minimizing "No Trouble Found" and "Electrical Overstress" failures due to latch-up.

Covers the I-test and the overvoltage latch-up testing of integrated circuits. The purpose of this test is to establish a method for determining integrated circuit latch-up characteristics and to define latch-up failure criteria. Latch-up characteristics are used in determining product reliability and minimizing "No Trouble Found" and "Electrical Overstress" failures due to latch-up.

IEC 60749-29:2003 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60749-29:2003 has the following relationships with other standards: It is inter standard links to IEC 60749-29:2011. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60749-29:2003 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE IEC

60749-29

INTERNATIONAL

Première édition

STANDARD

First edition

2003-11

Dispositifs à semiconducteurs –

Méthodes d'essais mécaniques et climatiques –

Partie 29:

Essai de verrouillage

Semiconductor devices –

Mechanical and climatic test methods –

Part 29:

Latch-up test

Numéro de référence

Reference number

CEI/IEC 60749-29:2003

Numérotation des publications Publication numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. Ainsi, la CEI 34-1 issued with a designation in the 60000 series. For

devient la CEI 60034-1. example, IEC 34-1 is now referred to as IEC 60034-1.

Editions consolidées Consolidated editions

Les versions consolidées de certaines publications de la The IEC is now publishing consolidated versions of its

CEI incorporant les amendements sont disponibles. Par publications. For example, edition numbers 1.0, 1.1

exemple, les numéros d’édition 1.0, 1.1 et 1.2 indiquent and 1.2 refer, respectively, to the base publication,

respectivement la publication de base, la publication de the base publication incorporating amendment 1 and

base incorporant l’amendement 1, et la publication de the base publication incorporating amendments 1

base incorporant les amendements 1 et 2. and 2.

Informations supplémentaires Further information on IEC publications

sur les publications de la CEI

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. Des renseignements relatifs à the content reflects current technology. Information

cette publication, y compris sa validité, sont dispo- relating to this publication, including its validity, is

nibles dans le Catalogue des publications de la CEI available in the IEC Catalogue of publications

(voir ci-dessous) en plus des nouvelles éditions, (see below) in addition to new editions, amendments

amendements et corrigenda. Des informations sur les and corrigenda. Information on the subjects under

sujets à l’étude et l’avancement des travaux entrepris consideration and work in progress undertaken by the

par le comité d’études qui a élaboré cette publication, technical committee which has prepared this

ainsi que la liste des publications parues, sont publication, as well as the list of publications issued,

également disponibles par l’intermédiaire de: is also available from the following:

• Site web de la CEI (www.iec.ch) • IEC Web Site (www.iec.ch)

• Catalogue des publications de la CEI • Catalogue of IEC publications

Le catalogue en ligne sur le site web de la CEI The on-line catalogue on the IEC web site

(www.iec.ch/searchpub) vous permet de faire des (www.iec.ch/searchpub) enables you to search by a

recherches en utilisant de nombreux critères, variety of criteria including text searches,

comprenant des recherches textuelles, par comité technical committees and date of publication. On-

d’études ou date de publication. Des informations en line information is also available on recently

ligne sont également disponibles sur les nouvelles issued publications, withdrawn and replaced

publications, les publications remplacées ou retirées, publications, as well as corrigenda.

ainsi que sur les corrigenda.

• IEC Just Published • IEC Just Published

Ce résumé des dernières publications parues This summary of recently issued publications

(www.iec.ch/online_news/justpub) est aussi dispo- (www.iec.ch/online_news/justpub) is also available

nible par courrier électronique. Veuillez prendre by email. Please contact the Customer Service

contact avec le Service client (voir ci-dessous) Centre (see below) for further information.

pour plus d’informations.

• Service clients • Customer Service Centre

Si vous avez des questions au sujet de cette If you have any questions regarding this

publication ou avez besoin de renseignements publication or need further assistance, please

supplémentaires, prenez contact avec le Service contact the Customer Service Centre:

clients:

Email: custserv@iec.ch Email: custserv@iec.ch

Tél: +41 22 919 02 11 Tel: +41 22 919 02 11

Fax: +41 22 919 03 00 Fax: +41 22 919 03 00

.

NORME CEI

INTERNATIONALE IEC

60749-29

INTERNATIONAL

Première édition

STANDARD

First edition

2003-11

Dispositifs à semiconducteurs –

Méthodes d'essais mécaniques et climatiques –

Partie 29:

Essai de verrouillage

Semiconductor devices –

Mechanical and climatic test methods –

Part 29:

Latch-up test

IEC 2003 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in any

utilisée sous quelque forme que ce soit et par aucun procédé, form or by any means, electronic or mechanical, including

électronique ou mécanique, y compris la photocopie et les photocopying and microfilm, without permission in writing from

microfilms, sans l'accord écrit de l'éditeur. the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

CODE PRIX

S

Commission Electrotechnique Internationale PRICE CODE

International Electrotechnical Commission

Международная Электротехническая Комиссия

Pour prix, voir catalogue en vigueur

For price, see current catalogue

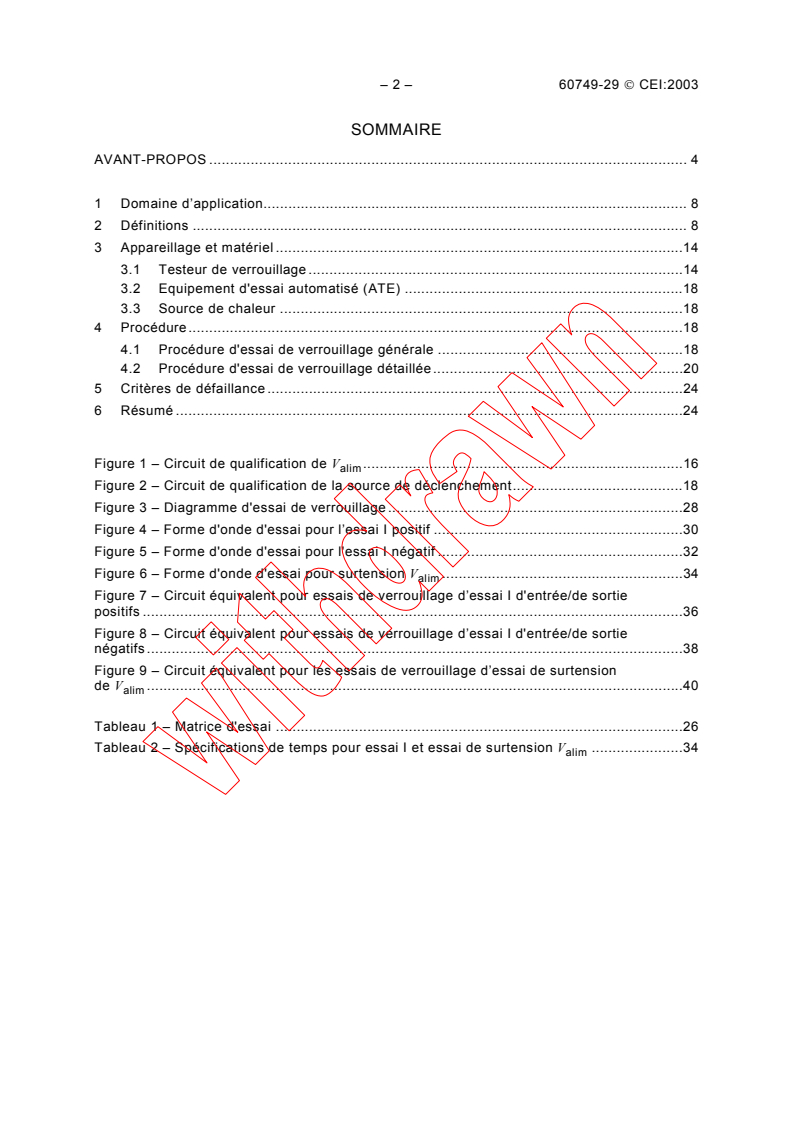

– 2 – 60749-29 CEI:2003

SOMMAIRE

AVANT-PROPOS . 4

1 Domaine d’application. 8

2 Définitions . 8

3 Appareillage et matériel .14

3.1 Testeur de verrouillage .14

3.2 Equipement d'essai automatisé (ATE) .18

3.3 Source de chaleur .18

4 Procédure.18

4.1 Procédure d'essai de verrouillage générale .18

4.2 Procédure d'essai de verrouillage détaillée.20

5 Critères de défaillance .24

6 Résumé .24

Figure 1 – Circuit de qualification de V .16

alim

Figure 2 – Circuit de qualification de la source de déclenchement.18

Figure 3 – Diagramme d'essai de verrouillage.28

Figure 4 – Forme d'onde d'essai pour l’essai I positif .30

Figure 5 – Forme d'onde d'essai pour l'essai I négatif .32

Figure 6 – Forme d'onde d'essai pour surtension V .34

alim

Figure 7 – Circuit équivalent pour essais de verrouillage d’essai I d'entrée/de sortie

positifs .36

Figure 8 – Circuit équivalent pour essais de verrouillage d’essai I d'entrée/de sortie

négatifs.38

Figure 9 – Circuit équivalent pour les essais de verrouillage d’essai de surtension

de V .40

alim

Tableau 1 – Matrice d'essai .26

Tableau 2 – Spécifications de temps pour essai I et essai de surtension V .34

alim

60749-29 IEC:2003 – 3 –

CONTENTS

FOREWORD . 5

1 Scope . 9

2 Definitions . 9

3 Apparatus and material.15

3.1 Latch-up tester .15

3.2 Automated test equipment (ATE) .19

3.3 Heat source .19

4 Procedure.19

4.1 General latch-up test procedure.19

4.2 Detailed latch-up test procedure .21

5 Failure criteria .25

6 Summary .25

Figure 1 – V qualification circuit .17

supply

Figure 2 – Trigger source qualification circuit .19

Figure 3 – Latch-up test flow .29

Figure 4 – Test waveform for positive I-test.31

Figure 5 – Test waveform for negative I-test .33

Figure 6 – Test waveform for V overvoltage .35

supply

Figure 7 – Equivalent circuit for positive input/output I-test latch-up testing.37

Figure 8 – Equivalent circuit for negative input/output I-test latch-up testing.39

Figure 9 – Equivalent circuit for V overvoltage test latch-up testing .41

supply

Table 1 – Test matrix .27

Table 2 — Timing specifications for I-test and V overvoltage test .35

supply

– 4 – 60749-29 CEI:2003

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

____________

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 29: Essai de verrouillage

AVANT-PROPOS

1) La Commission Electrotechnique Internationale (CEI) est une organisation mondiale de normalisation

composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a

pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les

domaines de l'électricité et de l'électronique. A cet effet, la CEI – entre autres activités – publie des Normes

internationales, des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au

public (PAS) et des Guides (ci-après dénommés "Publication(s) de la CEI"). Leur élaboration est confiée à des

comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les

organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent

également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO),

selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux de la CEI

intéressés sont représentés dans chaque comité d’études.

3) Les Publications de la CEI se présentent sous la forme de recommandations internationales et sont agréées

comme telles par les Comités nationaux de la CEI. Tous les efforts raisonnables sont entrepris afin que la CEI

s'assure de l'exactitude du contenu technique de ses publications; la CEI ne peut pas être tenue responsable

de l'éventuelle mauvaise utilisation ou interprétation qui en est faite par un quelconque utilisateur final.

4) Dans le but d'encourager l'uniformité internationale, les Comités nationaux de la CEI s'engagent, dans toute la

mesure possible, à appliquer de façon transparente les Publications de la CEI dans leurs publications

nationales et régionales. Toutes divergences entre toutes Publications de la CEI et toutes publications

nationales ou régionales correspondantes doivent être indiquées en termes clairs dans ces dernières.

5) La CEI n’a prévu aucune procédure de marquage valant indication d’approbation et n'engage pas sa

responsabilité pour les équipements déclarés conformes à une de ses Publications.

6) Tous les utilisateurs doivent s'assurer qu'ils sont en possession de la dernière édition de cette publication.

7) Aucune responsabilité ne doit être imputée à la CEI, à ses administrateurs, employés, auxiliaires ou

mandataires, y compris ses experts particuliers et les membres de ses comités d'études et des Comités

nationaux de la CEI, pour tout préjudice causé en cas de dommages corporels et matériels, ou de tout autre

dommage de quelque nature que ce soit, directe ou indirecte, ou pour supporter les coûts (y compris les frais

de justice) et les dépenses découlant de la publication ou de l'utilisation de cette Publication de la CEI ou de

toute autre Publication de la CEI, ou au crédit qui lui est accordé.

8) L'attention est attirée sur les références normatives citées dans cette publication. L'utilisation de publications

référencées est obligatoire pour une application correcte de la présente publication.

9) L’attention est attirée sur le fait que certains des éléments de la présente Publication de la CEI peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 60749-29 a été établie par le comité d'études 47 de la CEI:

Dispositifs à semiconducteurs.

La présente norme annule et remplace l'IEC/PAS 62181 publiée en 2000. Cette première

édition constitue une révision technique.

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

47/1713/FDIS 47/1724/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

60749-29 IEC:2003 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 29: Latch-up test

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-29 has been prepared by IEC technical committee 47:

Semiconductor devices.

This standard cancels and replaces IEC/PAS 62181 published in 2000. This first edition

constitutes a technical revision.

The text of this standard is based on the following documents:

FDIS Report on voting

47/1713/FDIS 47/1724/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

– 6 – 60749-29 CEI:2003

Cette publication a été rédigée selon les Directives ISO/CEI, Partie 2.

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant 2007. A

cette date, la publication sera

• reconduite;

• supprimée;

• remplacée par une édition révisée, ou

• amendée.

60749-29 IEC:2003 – 7 –

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until

2007. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

– 8 – 60749-29 CEI:2003

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 29: Essai de verrouillage

1 Domaine d’application et objet

La présente partie de la CEI 60749 couvre l'essai I et les essais de verrouillage de surtension

des circuits intégrés.

L'essai est considéré comme destructif.

L'objet de cet essai est d'établir une méthode pour déterminer les caractéristiques de

verrouillage des circuits intégrés (CI) et pour définir les critères de défaillance de verrouillage.

Les caractéristiques de verrouillage sont utilisées dans la détermination de la fiabilité de

produit et la minimisation des défaillances en rapport avec «l'absence d'observation de

problèmes» (NTF) et la «contrainte électrique excessive» (EOS) du fait du verrouillage.

Cette méthode d'essai est essentiellement applicable aux CMOS. Il faut établir l’applicabilité à

d’autres technologies.

Tel qu'il est utilisé dans cette partie de la CEI 60749, le verrouillage n'est pas lié à un

mécanisme spécifique mais il constitue une caractéristique de défaillance électrique qui se

produit lorsqu'un dispositif est soumis à cette méthode d'essai.

La classification du verrouillage comme étant fonction de la température est définie en 2.1 et

les niveaux de critères de défaillance sont définis en 2.10.

2 Termes et définitions

Pour les besoins de ce document, les termes et définitions suivants s'appliquent.

2.1

classification

la classification définit la température d'essai de verrouillage. Les classifications d'essai de

verrouillage sont définies de la façon suivante:

Classe I – Essai de verrouillage réalisé à température ambiante.

Classe II – Essai de verrouillage réalisé à la température assignée ambiante maximale pour

le dispositif.

Si aucune classification n'est spécifiée, l'essai de Classe I doit être réalisé.

NOTE La température élevée réduit la résistance au verrouillage et l'essai de Classe II est recommandé pour des

dispositifs qui fonctionnent nécessairement à température élevée.

2.2

temps de refroidissement

période de temps entre les applications successives d'impulsions de déclenchement ou la

période de temps entre la suppression de la tension d'alimentation V et l'application de

alim

l'impulsion de déclenchement suivante (voir Figures 4, 5 et 6 ainsi que le Tableau 2.)

60749-29 IEC:2003 – 9 –

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 29: Latch-up test

1 Scope and object

This part of IEC 60749 covers the I-test and the overvoltage latch-up testing of integrated

circuits.

This test is classified as destructive.

The purpose of this test is to establish a method for determining integrated circuit (IC) latch-

up characteristics and to define latch-up failure criteria. Latch-up characteristics are used in

determining product reliability and minimizing "No Trouble Found" (NTF) and "Electrical

Overstress" (EOS) failures due to latch-up.

This test method is primarily applicable to CMOS devices. Applicability to other technologies

must be established.

In this part of IEC 60749 latch-up is not related to a specific mechanism but is an electrical

failure characteristic that occurs when a device is subjected to this test method.

The classification of latch-up as a function of temperature is defined in 2.1 and the failure

level criteria are defined in 2.10

2 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

2.1

classification

the classification defines the latch-up test temperature. Latch-up testing classifications are

defined as follows:

Class I – Latch-up testing performed at room temperature.

Class II – Latch-up testing performed at the maximum ambient rated temperature for the

device.

If no classification is specified, Class I testing shall be performed.

NOTE Elevated temperature will reduce latch-up resistance and Class II testing is recommended for devices that

are required to operate at elevated temperature.

2.2

cool-down time

period of time between successive applications of trigger pulses or the period of time between

the removal of the V voltage and the application of the next trigger pulse (See Figures 4,

supply

5, and 6 and Table 2.)

– 10 – 60749-29 CEI:2003

2.3

DEE

dispositif en essai

2.4

GND (terre)

broche(s) commune(s) ou à potentiel zéro du DEE

NOTE 1 Les broches de terre ne font pas l'objet d'un essai de verrouillage.

NOTE 2 Une broche de terre est parfois désignée V .

ss

2.5

broches d'entrée

toutes les broches d'adresse, de contrôle de données entrée, V et similaires

réf

2.6

broches d'E/S (bi-directionnelles)

broches de dispositif qui peuvent être conçues pour fonctionner en tant qu'entrée ou en tant

que sortie ou encore dans un état de haute impédance

2.7

I

alim

courant d'alimentation total dans chaque broche d'alimentation V (ou groupe de broches)

alim

en polarisant le DEE comme indiqué dans le Tableau 1

2.8

essai I

essai de verrouillage qui fournit des impulsions de courant positives et négatives à la broche

en essai

2.9

phénomène de verrouillage

état dans lequel un chemin conducteur de faible impédance, résultant d'un excès de

contrainte qui déclenche une structure parasite de thyristor, persiste après retrait ou

cessation de la condition de déclenchement

NOTE 1 L'excès de contrainte peut être une tension de choc ou une surintensité, un taux excessif de variation de

courant ou de tension ou toute autre condition anormale qui entraîne le fait que la structure parasite de thyristor

devient régénératrice.

NOTE 2 Le verrouillage n'endommage pas le dispositif, à condition que le courant à travers le chemin conducteur

de faible impédance soit suffisamment limité en amplitude ou durée.

2.10

niveau

définit les critères de défaillance utilisés pendant l'essai de verrouillage. Les catégories de

défaillance de verrouillage sont définies de la façon suivante:

Niveau A – Critères de défaillance définis dans le Tableau 1

Niveau B – Critères de défaillance spéciaux. Il convient que le fournisseur donne la définition

des critères de défaillance utilisés

2.11

logique à l'état haut

niveau dans la plus positive (moins négative) des deux gammes de niveaux logiques choisis

pour représenter les états logiques

NOTE 1 Pour des dispositifs numériques, un niveau de tension égal à V est utilisé pour les essais de

alim

verrouillage sauf indication contraire dans la spécification du dispositif.

60749-29 IEC:2003 – 11 –

2.3

DUT

device under test

2.4

GND (ground)

common or zero-potential pin(s) of the DUT

NOTE 1 Ground pins are not latch-up tested.

NOTE 2 A ground pin is sometimes called V .

ss

2.5

input pins

all address, data-in control, V and similar pins

ref

2.6

I/O (bi-directional) pins

device pins that can be made to operate as an input or output or in a high-impedance state

2.7

I

supply

total supply current in each V pin (or pin group) with the DUT biased as indicated in

supply

Table 1

2.8

I-test

latch-up test that supplies positive and negative current pulses to the pin under test

2.9

latch-up

state in which a low-impedance path resulting from an overstress that triggers a parasitic

thyristor structure, persists after removal or cessation of the triggering condition

NOTE 1 The overstress can be a voltage or current surge, an excessive rate of change of current or voltage, or

any other abnormal condition that causes the parasitic thyristor structure to become regenerative.

NOTE 2 Latch-up will not damage the device provided that the current through the low-impedance path is

sufficiently limited in magnitude or duration.

2.10

level

defines the failure criteria used during latch-up testing. Latch-up failure grades are defined as

follows:

Level A – The failure criteria as defined in Table 1

Level B – Special failure criteria. Supplier should provide definition of failure criteria used

2.11

logic-high

level within the more positive (less negative) of the two ranges of logic levels chosen to

represent the logic states

NOTE 1 For digital devices, a voltage level equal to V is used for latch-up testing, except where otherwise

supply

specified in the relevant specification.

– 12 – 60749-29 CEI:2003

NOTE 2 Pour les dispositifs non numériques, le niveau de tension V ou la tension de fonctionnement maximale

alim

qui peut être appliquée à la broche telle que définie dans la spécification du dispositif peut être utilisé pour l'essai

de verrouillage.

2.12

logique à l'état bas

niveau dans la plus négative (moins positive) des deux gammes de niveaux logiques choisis

pour représenter les états logiques

NOTE 1 Pour des dispositifs numériques, le niveau de tension de masse est utilisé pour les essais de verrouillage

sauf indication dans la spécification du dispositif.

NOTE 2 Pour les dispositifs non numériques, le niveau de tension de masse ou la tension de fonctionnement

minimale qui peut être appliquée à la broche telle que définie dans la spécification du dispositif peut être utilisé

pour l'essai de verrouillage.

2.13

V maximale

alim

tension de fonctionnement maximale pour un fonctionnement au sein des spécifications de

performance

NOTE 1 La tension maximale n'est pas la tension maximale absolue au-dessus de laquelle un dommage

permanent est probable.

NOTE 2 Le qualificatif 'maximale' se réfère à l'amplitude de la tension V et peut être soit positive soit négative.

alim

2.14

broche sans connexion

broche qui peut être sans connexion interne et peut être utilisée en tant que support pour le

câblage externe sans perturber la fonction du dispositif

NOTE Il convient que toutes les broches «sans connexion» soient laissées à l'état ouvert (flottantes) pendant les

essais de verrouillage.

2.15

I nominale (I )

alim nom

courant d'alimentation c.c. mesuré pour chaque broche d'alimentation V (ou groupe de

alim

broches) en polarisant le DEE à la température d'essai définie à l'Article 4 et au Tableau 1

2.16

broche de sortie

broche d'un dispositif qui génère un niveau de signal ou de tension comme fonction normale

pendant le fonctionnement normal du dispositif

NOTE Les broches de sortie, bien que laissées dans un état ouvert (flottant) pendant l'essai d'autres types de

broche, font l'objet d'essais de verrouillage.

2.17

broche préconditionnée

broche d'un dispositif qui a été placée dans un état ou une condition défini(e) (impédance

d'entrée, de sortie, haute impédance, etc.) en appliquant les vecteurs de commande au DEE

2.18

essai de dispositifs dynamiques

essai de déclenchement de verrouillage d'un dispositif dans un état stable connu, à la

fréquence d'horloge assignée minimale appliquée au dispositif (voir 4.2.3 pour les conditions

spécifiées)

2.19

conditions d'essai

la température d'essai, la tension d'alimentation, les limites de courant, les limites de tension,

la fréquence d'horloge, les tensions de polarisation d'entrée et les vecteurs de précondition-

nement appliqués au DEE pendant l'essai de verrouillage

60749-29 IEC:2003 – 13 –

NOTE 2 For non-digital devices, V voltage level or the maximum operating voltage that can be applied to that

supply

pin as defined in the relevant specification may be used for latch-up testing.

2.12

logic-low

level within the more negative (less positive) of the two ranges of logic levels chosen to

represent the logic states

NOTE 1 For digital devices, ground voltage level is used for latch-up testing, except where specified in the

relevant specification.

NOTE 2 For non-digital devices, ground voltage level or the minimum operating voltage that can be applied to that

pin as defined in the relevant specification may be used for latch-up testing.

2.13

maximum V

supply

maximum operating voltage for operation within performance specifications

NOTE 1 The maximum voltage is not the absolute maximum voltage beyond which permanent damage is

likely.

NOTE 2 Maximum refers to the magnitude of V and can be either positive or negative.

supply

2.14

no connect pin

pin that has no internal connection and that can be used as a support for external wiring

without disturbing the function of the device

NOTE All “no connect” pins should be left in an open (floating) state during latch-up testing.

2.15

nominal I (I )

supply nom

measured dc supply current for each V pin (or pin group) with the DUT biased at the test

supply

temperature as defined in Clause 4 and Table 1

2.16

output pin

device pin that generates a signal or voltage level as a normal function during the normal

operation of the device

NOTE Output pins, though left in an open (floating) state during testing of other pin types, are latch-up tested.

2.17

preconditioned pin

device pin that has been placed in a defined state or condition (input, output, high impedance,

etc.) by applying control vectors to the DUT

2.18

testing of dynamic devices

latch-up trigger testing of a device in a known stable state, at the minimum-rated clock

frequency applied to the device (see 4.2.3 for specified conditions)

2.19

test condition

test temperature, supply voltage, current limits, voltage limits, clock frequency, input bias

voltages, and preconditioning vectors applied to the DUT during the latch-up test

– 14 – 60749-29 CEI:2003

2.20

broche d'entrée liée au temps

broche telle qu'un oscillateur de cristal d'horloge, un circuit de pompe de charge, etc., exigée

pour placer le DEE en mode de fonctionnement normal

NOTE Le cas échéant, les signaux de rythmes nécessaires peuvent être appliqués par le testeur de verrouillage,

l'équipement externe et/ou les composants externes.

2.21

impulsion de déclenchement

impulsion positive ou négative de courant (essai I) ou impulsion positive ou négative de

tension (essai de surtension d'alimentation V ) appliquée à toute broche en essai pour

alim

essayer d'induire le verrouillage (voir les Figures 4, 5 et 6)

2.22

durée de déclenchement

durée d'une impulsion appliquée à partir d'une source de déclenchement (voir Figures 4, 5 et

6 ainsi que le Tableau 2)

2.23

broche V (ou groupe de broches)

alim

toutes les broches d'alimentation électrique du DEE et de source de tension externe (à

l'exclusion des broches de terre), y compris les broches de potentiel tant positif que négatif

NOTE 1 Généralement, il est permis de traiter les broches de source de tension de potentiel égal comme une

broche V (ou un groupe de broches) et de les connecter à une alimentation électrique.

alim

NOTE 2 Lorsque l'on forme les broches V (ou les groupes de broches), la combinaison des broches V avec

alim alim

des niveaux de courant d'alimentation largement différents n'est pas recommandée car cela rendrait difficile la

détection des variations de courant significatives sur les broches de courant d'alimentation faible.

2.24

essai de surtension V

alim

essai de verrouillage qui fournit des impulsions de surtension ou un niveau de surtension c.c.

à la broche V en essai

alim

2.25

niveau de tension V

alim

niveau de tension applicable de la broche stipulée V dans la spécification du dispositif. Le

alim

niveau de tension V est utilisé pour l’essai de verrouillage comme niveau logique typique à

alim

l’état haut, sauf spécification contraire (voir 2.11)

2.26

niveau de tension de masse

niveau de masse utilisé pour l’essai de verrouillage comme niveau logique typique à l’état

bas, sauf spécification contraire (voir 2.12)

3 Appareillage et matériel

L'appareillage nécessaire à cette méthode d'essai inclut les éléments qui suivent.

3.1 Testeur de verrouillage

Equipement d'essai capable de réaliser les essais spécifiés dans cette norme. Pour les

dispositifs exigeant des essais dynamiques, l'équipement d'essai doit être en mesure de

fournir des signaux de synchronisation et des vecteurs de montages logiques nécessaires

pour commander les états de sortie de broches d'E/S, comme spécifié en 4.2.3. Les signaux

de synchronisation et les vecteurs logiques nécessaires peuvent être appliqués par le testeur

de verrouillage lui-même, l'équipement externe, et/ou les composants externes appropriés.

60749-29 IEC:2003 – 15 –

2.20

timing-related input pin

pin such as clock crystal oscillator, charge pump circuit, etc., required to place the DUT in a

normal operating mode

NOTE Required timing signals may be applied by the latch-up tester, external equipment, and/or external

components as appropriate.

2.21

trigger pulse

positive or negative current pulse (I-Test) or voltage pulse (V overvoltage test) applied to

supply

any pin under test in an attempt to induce latch-up (see Figures 4, 5 and 6)

2.22

trigger duration

duration of an applied pulse from the trigger source (see Figures 4, 5 and 6 and Table 2)

2.23

V pin (or pin group)

supply

all DUT power supply and external voltage source pins (excluding ground pins), including both

positive- and negative-potential pins

NOTE 1 Generally, it is permissible to treat equal potential voltage source pins as one V pin (or pin group)

supply

and connect them to one power supply.

NOTE 2 When forming V pins (or pin groups), the combination of V pins with significantly different

supply supply

supply current levels is not recommended as this would make it difficult to detect significant current changes on

low supply current pins.

2.24

V overvoltage test

supply

latch-up test that supplies overvoltage pulses or overvoltage d.c. level to the V pin under

supply

test

2.25

V voltage level

supply

applicable voltage level of the V pin specified in the relevant specification. The V

supply supply

voltage level is used for latch-up testing as the typical logic high level unless otherwise

specified (see 2.11)

2.26

ground voltage level

ground potential used for latch-up testing as the typical logic low level, unless otherwise

specified (see 2.12)

3 Apparatus and material

The apparatus required for this test method includes the following.

3.1 Latch-up tester

Test equipment capable of performing the tests as specified in this standard. For devices

requiring dynamic testing, the test equipment shall be capable of supplying timing signals and

logic setup vectors required to control the I/O pin output states as specified in 4.2.3. The

required timing signals and logic vectors may be applied by the latch-up tester itself, external

equipment, and/or external components as appropriate.

– 16 – 60749-29 CEI:2003

3.1.1 V et leurs méthodes de qualification

alim

Pour l’essai I, les tensions d’alimentation de type réception doivent être connectées à toutes

les broches V comme indiqué dans la Figure 7 et la Figure 8 et les caractéristiques

alim

transitoires doivent être qualifiées comme indiqué à la Figure 1. Les étapes de qualification

sont les suivantes:

a) Connecter la tension d’alimentation (par exemple 5 V, 3,3 V) à la broche V . La valeur

alim

de la tension peut être stipulée dans la spécification du dispositif.

b) Appliquer les impulsions positive et négative d’une source de déclenchement de 200 mA

et mesurer leur effet sur la forme d’onde de tension apparaissant sur l’oscilloscope.

c) La tension mesurée par l’oscilloscope doit être comprise entre 90 % et 110 % de la

tension d’alimentation.

I

source

Broche V

alim

Source de déclenchement

Sonde de

R

tension

+

Broche en essai

V 1

alim

Support de DEE

ou équivalent

–

Vers l’oscilloscope

Broche de terre

La valeur de R (par exemple 50 Ω) est spécifiée dans le document d’approvisionnement.

L’impédance d’entrée de la sonde de tension et de l’oscilloscope est > 10 kΩ.

IEC 2483/03

Figure 1 – Circuit de qualification de V

alim

3.1.2 Méthode de qualification de la source de déclenchement

Les caractéristiques électriques de la source de déclenchement, y compris ses caracté-

ristiques transitoires, doivent être qualifiées comme indiqué à la Figure 2. Les étapes de

qualification sont les suivantes:

a) Le commutateur S1 étant fermé, appliquer des impulsions positives et négatives d’une

source de déclenchement de 200 mA et mesurer sa forme d’onde stabilisée. La forme

d’onde stabilisée doit satisfaire aux exigences du Tableau 1.

b) Après établissement du niveau de tension et ouverture de S1, appliquer les impulsions

positives et négatives de la source de déclenchement de 100 mA et mesurer la forme

d’onde de tension. La forme d’onde de tension pendant l’établissement du niveau de

tension doit être comprise entre 90 % et 110 % du niveau d’établissement du niveau de

tension.

60749-29 IEC:2003 – 17 –

3.1.1 V and their qualification method

supply

For the I-test, sink type voltage power supplies shall be connected to all V pins as shown

supply

in Figure 7 and Figure 8, and the transient characteristics shall be qualified as shown in

Figure 1. The qualification steps are as follows:

a) Connect the supply voltage (e.g. 5 V, 3,3 V) to the V pin. The value of voltage may

supply

be specified in the relevant specification.

b) Apply positive and negative pulses from the 200 mA trigger source, and measure their

effect on the voltage waveform shown on the oscilloscope.

c) The voltage measured by the oscilloscope shall be within 90 % to 110 % of the supply

voltage.

I

source

V pin

supply

Trigger source

Voltage

R

probe

+

Pin under test

V 1

supply

DUT socket

or equivalent

–

To oscilloscope

GND pin

Value of R (e.g. 50 Ω) is specified in the applicable procurement document.

Input impedance of voltage probe and oscilloscope is over 10 kΩ.

IEC 2483/03

Figure 1 – V qualification circuit

supply

3.1.2 Trigger source qualification method

The electrical characteristics of the trigger source including its transient characteristics shall

be qualified as shown in Figure 2. The qualification steps are as follows:

a) With switch S1 closed, apply positive and negative pulses from the 200 mA trigger source,

and measure its current waveform. The current waveform shall satisfy the requirements of

Table 1.

b) After setting the voltage clamp level and opening S1, apply positive and negative pulses

from the 100 mA trigger source and measure its voltage waveform. The voltage waveform

during the working voltage clamp shall be within 90 % to 110 % of the voltage clamp

setting level.

– 18 – 60749-29 CEI:2003

Source de déclenchement

Sonde de

tension

Support de DEE

ou équivalent

S1

Broche en essai

R

Vers l’oscilloscope

Broche de terre

La valeur de R (par exemple 50 Ω) est spécifiée dans le document d’approvisionnement.

L’impédance d’entrée de la sonde de tension et de l’oscilloscope est > 10 kΩ.

IEC 2484/03

Figure 2 – Circuit de qualification de la source de déclenchement

3.2 Equipement d'essai automatisé (ATE)

Testeur de dispositif capable de réaliser des essais fonctionnels et paramétriques complets

du dispositif selon les exigences de la spécification du dispositif.

3.3 Source de chaleur

Equipement capable de chauffer et de maintenir le DEE à la température de fonctionnement

maximale stipulée dans la spécification du dispositif pendant l'essai de verrouillage.

4 Procédure

4.1 Procédure d'essai de verrouillage générale

Un groupe d'échantillons de plusieurs dispositifs (par exemple six) doit être soumis aux

essais de verrouillage en utilisant l’essai I et l'essai de surtension V . L'utilisation d'un

alim.

nouveau groupe d'échantillons pour chaque type d'essai de verrouillage (essai I et/ou essai

de surtension V ) est également acceptable. Tous les dispositifs devant être soumis à

alim

l'essai de verrouillage doivent avoir réussi les essais paramétriques et fonctionnels.

Avant les essais de verrouillage, il convient de vérifier la continuité du dispositif dans le

support pour éviter de fausses défaillances de verrouillage. Le diagramme d'essai de

verrouillage doit être conforme à la Figure 3. Les dispositifs à essayer doivent être soumis

aux conditions d'essai du Tableau 1 et du Tableau 2. On doit laisser ouvertes (flottantes)

toutes les broches «sans connexion» sur le DEE

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...