IEC 60749-44:2016

(Main)Semiconductor devices - Mechanical and climatic test methods - Part 44: Neutron beam irradiated single event effect (SEE) test method for semiconductor devices

Semiconductor devices - Mechanical and climatic test methods - Part 44: Neutron beam irradiated single event effect (SEE) test method for semiconductor devices

IEC 60749-44:2016 establishes a procedure for measuring the single event effects (SEEs) on high density integrated circuit semiconductor devices including data retention capability of semiconductor devices with memory when subjected to atmospheric neutron radiation produced by cosmic rays. The single event effects sensitivity is measured while the device is irradiated in a neutron beam of known flux. This test method can be applied to any type of integrated circuit.

NOTE 1 - Semiconductor devices under high voltage stress can be subject to single event effects including SEB, single event burnout and SEGR single event gate rupture, for this subject which is not covered in this document, please refer to IEC 62396-4.

NOTE 2 - In addition to the high energy neutrons some devices can have a soft error rate due to low energy (<1 eV) thermal neutrons. For this subject which is not covered in this document, please refer to IEC 62396-5.

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques - Partie 44: Méthode d'essai des effets d'un événement isolé (SEE) irradié par un faisceau de neutrons pour des dispositifs à semiconducteurs

L'IEC 60749-44:2016 établit une procédure pour mesurer les effets d'un événement isolé (SEE: Single Event Effect) sur des dispositifs à semiconducteurs pour circuits intégrés haute densité incluant l'aptitude des dispositifs à semiconducteurs à mémoire à conserver les données lorsqu'ils sont soumis à un rayonnement neutronique atmosphérique produit par des rayons cosmiques. La sensibilité des effets d'un événement isolé est mesurée pendant que le dispositif est irradié par un faisceau de neutrons dont le flux est connu. Cette méthode d'essai peut être appliquée à n'importe quel type de circuit intégré.

NOTE 1 - Les dispositifs à semiconducteurs soumis à des contraintes de tension élevée peuvent être sujets aux effets d'un événement isolé, y compris un événement isolé de claquage (SEB: Single Event Burnout) et un événement isolé de claquage de grille (SEGR: Single Event Gate Rupture). Se reporter à l'IEC 62396-4 pour plus d'informations sur ce phénomène qui n'est pas couvert par le présent document.

NOTE 2 - Outre les neutrons d'énergie élevée, certains dispositifs peuvent avoir un taux d'erreurs logicielles en raison des neutrons thermiques de faible énergie (<1 eV). Se reporter à l'IEC 62396-5 pour plus d'informations sur ce phénomène qui n'est pas couvert par le présent document.

General Information

- Status

- Published

- Publication Date

- 20-Jul-2016

- Technical Committee

- TC 47 - Semiconductor devices

- Drafting Committee

- WG 2 - TC 47/WG 2

- Current Stage

- PPUB - Publication issued

- Start Date

- 21-Jul-2016

- Completion Date

- 15-Sep-2016

Overview

IEC 60749-44:2016 is an international standard issued by the International Electrotechnical Commission (IEC) that specifies test methods for evaluating the effects of neutron radiation on semiconductor devices. This standard is part 44 of the IEC 60749 series, which focuses on mechanical and climatic test methods for semiconductor devices. Specifically, IEC 60749-44 defines a neutron beam irradiated single event effect (SEE) test method intended to assess the sensitivity of high-density integrated circuit semiconductor devices-including memory components prone to data retention issues-to atmospheric neutron radiation generated by cosmic rays.

The test method measures single event effects (SEEs) by irradiating a device under test using a neutron beam of known flux and analyzing the induced soft errors or logic state changes. It is applicable to various types of integrated circuits and is essential for understanding device vulnerability to neutrons, which can cause transient faults or permanent damage during normal operation.

Key Topics

Single Event Effects (SEEs): Transient phenomena induced in semiconductor devices due to interactions with atmospheric neutrons. Includes single-event upsets (SEUs), multiple bit upsets (MBUs), and other soft errors affecting data integrity.

Neutron Beam Irradiation: Controlled exposure of devices to a neutron flux that simulates cosmic ray neutrons encountered at ground level or at altitude. The test method outlines procedures for beam characterization, flux measurement, and device irradiation.

Measurement Procedure: The standard details important parameters such as surface preparation, power supply voltage, core cycle time, data patterns, ambient temperature control, number of measurement samples, and time calculation for neutron beam exposure.

Evaluation and Failure Rate: The method includes guidelines for estimating failure rates, determining cross sections for SEU and MBU, and calculating device failure in terms of FIT (Failures In Time) based on measured cross sections.

Device Scope: Applicable to all integrated circuit semiconductor devices, with exclusions noted for devices under high voltage stress prone to single event burnout or gate rupture-referenced to IEC 62396-4 for those cases.

Applications

Reliability Testing: Semiconductor manufacturers and quality control engineers use IEC 60749-44 procedures to evaluate and validate the robustness of ICs against neutron-induced SEEs before product release.

Design Verification: IC designers utilize SEE test results to improve radiation hardness in semiconductor devices, ensuring reliability for aerospace, automotive, and ground-level applications sensitive to soft errors.

Safety-Critical Electronics: Systems operating in avionics, space applications, telecommunications, and nuclear environments benefit from testing semiconductor components per IEC 60749-44 to avoid unexpected failures caused by neutrons.

Soft Error Rate (SER) Analysis: The standard supports predictive modeling of SER in integrated circuits by providing measured cross sections under neutron beam irradiation, enabling more accurate reliability assessments.

Related Standards

IEC 62396-4: Covers single event effects testing on devices under high voltage stress, including single event burnout (SEB) and single event gate rupture (SEGR), which are not within IEC 60749-44’s scope.

IEC 62396-5: Addresses the effects of low energy (thermal) neutrons (<1 eV) on semiconductor device soft error rates, extending the neutron radiation testing spectrum beyond what IEC 60749-44 covers.

IEC 60749 Series: Other parts of this series provide additional mechanical and climatic test methods relevant to overall semiconductor device reliability and characterization.

Keywords: IEC 60749-44, single event effects, SEE test method, neutron beam irradiation, semiconductor devices reliability, integrated circuit testing, single event upset, multiple bit upset, neutron radiation, soft error rate, semiconductor device testing, radiation hardness, IEC standards.

Frequently Asked Questions

IEC 60749-44:2016 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Mechanical and climatic test methods - Part 44: Neutron beam irradiated single event effect (SEE) test method for semiconductor devices". This standard covers: IEC 60749-44:2016 establishes a procedure for measuring the single event effects (SEEs) on high density integrated circuit semiconductor devices including data retention capability of semiconductor devices with memory when subjected to atmospheric neutron radiation produced by cosmic rays. The single event effects sensitivity is measured while the device is irradiated in a neutron beam of known flux. This test method can be applied to any type of integrated circuit. NOTE 1 - Semiconductor devices under high voltage stress can be subject to single event effects including SEB, single event burnout and SEGR single event gate rupture, for this subject which is not covered in this document, please refer to IEC 62396-4. NOTE 2 - In addition to the high energy neutrons some devices can have a soft error rate due to low energy (<1 eV) thermal neutrons. For this subject which is not covered in this document, please refer to IEC 62396-5.

IEC 60749-44:2016 establishes a procedure for measuring the single event effects (SEEs) on high density integrated circuit semiconductor devices including data retention capability of semiconductor devices with memory when subjected to atmospheric neutron radiation produced by cosmic rays. The single event effects sensitivity is measured while the device is irradiated in a neutron beam of known flux. This test method can be applied to any type of integrated circuit. NOTE 1 - Semiconductor devices under high voltage stress can be subject to single event effects including SEB, single event burnout and SEGR single event gate rupture, for this subject which is not covered in this document, please refer to IEC 62396-4. NOTE 2 - In addition to the high energy neutrons some devices can have a soft error rate due to low energy (<1 eV) thermal neutrons. For this subject which is not covered in this document, please refer to IEC 62396-5.

IEC 60749-44:2016 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60749-44:2016 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 60749-44 ®

Edition 1.0 2016-07

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 44: Neutron beam irradiated single event effect (SEE) test method for

semiconductor devices

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 44: Méthode d'essai des effets d'un événement isolé (SEE) irradié par un

faisceau de neutrons pour des dispositifs à semiconducteurs

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

IEC Catalogue - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

The stand-alone application for consulting the entire The world's leading online dictionary of electronic and

bibliographical information on IEC International Standards, electrical terms containing 20 000 terms and definitions in

Technical Specifications, Technical Reports and other English and French, with equivalent terms in 15 additional

documents. Available for PC, Mac OS, Android Tablets and languages. Also known as the International Electrotechnical

iPad. Vocabulary (IEV) online.

IEC publications search - www.iec.ch/searchpub IEC Glossary - std.iec.ch/glossary

The advanced search enables to find IEC publications by a 65 000 electrotechnical terminology entries in English and

variety of criteria (reference number, text, technical French extracted from the Terms and Definitions clause of

committee,…). It also gives information on projects, replaced IEC publications issued since 2002. Some entries have been

and withdrawn publications. collected from earlier publications of IEC TC 37, 77, 86 and

CISPR.

IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published IEC Customer Service Centre - webstore.iec.ch/csc

details all new publications released. Available online and If you wish to give us your feedback on this publication or

also once a month by email. need further assistance, please contact the Customer Service

Centre: csc@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Catalogue IEC - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

Application autonome pour consulter tous les renseignements

Le premier dictionnaire en ligne de termes électroniques et

bibliographiques sur les Normes internationales,

électriques. Il contient 20 000 termes et définitions en anglais

Spécifications techniques, Rapports techniques et autres

et en français, ainsi que les termes équivalents dans 15

documents de l'IEC. Disponible pour PC, Mac OS, tablettes

langues additionnelles. Egalement appelé Vocabulaire

Android et iPad.

Electrotechnique International (IEV) en ligne.

Recherche de publications IEC - www.iec.ch/searchpub

Glossaire IEC - std.iec.ch/glossary

La recherche avancée permet de trouver des publications IEC 65 000 entrées terminologiques électrotechniques, en anglais

en utilisant différents critères (numéro de référence, texte, et en français, extraites des articles Termes et Définitions des

comité d’études,…). Elle donne aussi des informations sur les publications IEC parues depuis 2002. Plus certaines entrées

projets et les publications remplacées ou retirées. antérieures extraites des publications des CE 37, 77, 86 et

CISPR de l'IEC.

IEC Just Published - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications IEC. Just

Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur cette

Disponible en ligne et aussi une fois par mois par email. publication ou si vous avez des questions contactez-nous:

csc@iec.ch.

IEC 60749-44 ®

Edition 1.0 2016-07

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 44: Neutron beam irradiated single event effect (SEE) test method for

semiconductor devices

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 44: Méthode d'essai des effets d'un événement isolé (SEE) irradié par un

faisceau de neutrons pour des dispositifs à semiconducteurs

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.080.01 ISBN 978-2-8322-3541-6

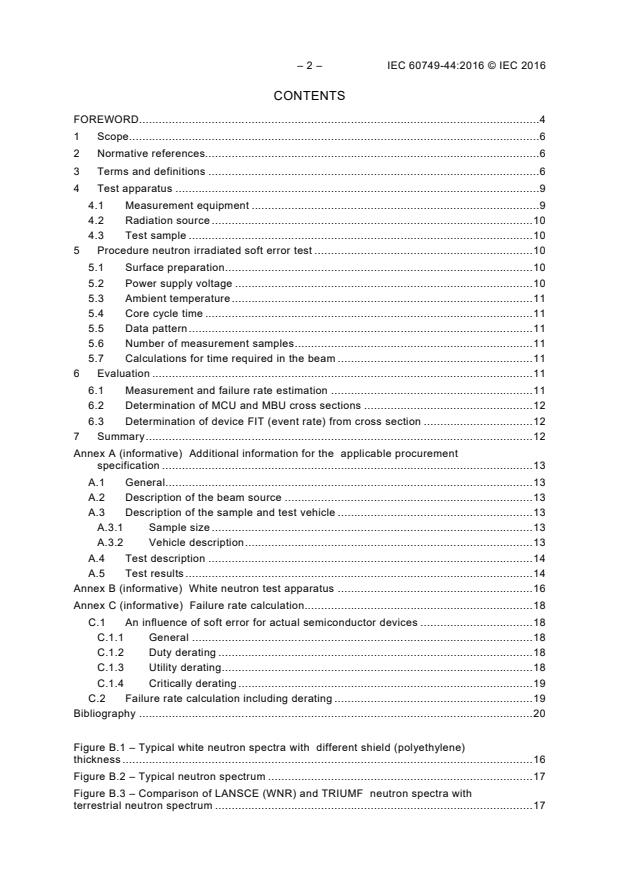

– 2 – IEC 60749-44:2016 © IEC 2016

CONTENTS

FOREWORD . 4

1 Scope . 6

2 Normative references. 6

3 Terms and definitions . 6

4 Test apparatus . 9

4.1 Measurement equipment . 9

4.2 Radiation source . 10

4.3 Test sample . 10

5 Procedure neutron irradiated soft error test . 10

5.1 Surface preparation . 10

5.2 Power supply voltage . 10

5.3 Ambient temperature . 11

5.4 Core cycle time . 11

5.5 Data pattern . 11

5.6 Number of measurement samples . 11

5.7 Calculations for time required in the beam . 11

6 Evaluation . 11

6.1 Measurement and failure rate estimation . 11

6.2 Determination of MCU and MBU cross sections . 12

6.3 Determination of device FIT (event rate) from cross section . 12

7 Summary . 12

Annex A (informative) Additional information for the applicable procurement

specification . 13

A.1 General . 13

A.2 Description of the beam source . 13

A.3 Description of the sample and test vehicle . 13

A.3.1 Sample size . 13

A.3.2 Vehicle description . 13

A.4 Test description . 14

A.5 Test results . 14

Annex B (informative) White neutron test apparatus . 16

Annex C (informative) Failure rate calculation . 18

C.1 An influence of soft error for actual semiconductor devices . 18

C.1.1 General . 18

C.1.2 Duty derating . 18

C.1.3 Utility derating . 18

C.1.4 Critically derating . 19

C.2 Failure rate calculation including derating . 19

Bibliography . 20

Figure B.1 – Typical white neutron spectra with different shield (polyethylene)

thickness . 16

Figure B.2 – Typical neutron spectrum . 17

Figure B.3 – Comparison of LANSCE (WNR) and TRIUMF neutron spectra with

terrestrial neutron spectrum . 17

Figure C.1 – Schematic image of duty derating . 18

Figure C.2 – Schematic image of memory effective area for utility derating . 19

– 4 – IEC 60749-44:2016 © IEC 2016

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 44: Neutron beam irradiated single event effect (SEE)

test method for semiconductor devices

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-44 has been prepared by IEC technical committee 47:

Semiconductor devices.

The text of this standard is based on the following documents:

FDIS Report on voting

47/2303/FDIS 47/2312/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all the parts in the IEC 60749 series, published under the general title Semiconductor

devices – Mechanical and climatic test methods, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct

understanding of its contents. Users should therefore print this document using a

colour printer.

– 6 – IEC 60749-44:2016 © IEC 2016

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 44: Neutron beam irradiated single event effect (SEE)

test method for semiconductor devices

1 Scope

This part of IEC 60749 establishes a procedure for measuring the single event effects (SEEs)

on high density integrated circuit semiconductor devices including data retention capability of

semiconductor devices with memory when subjected to atmospheric neutron radiation produced

by cosmic rays. The single event effects sensitivity is measured while the device is irradiated in a

neutron beam of known flux. This test method can be applied to any type of integrated circuit.

NOTE 1 Semiconductor devices under high voltage stress can be subject to single event effects including SEB,

single event burnout and SEGR single event gate rupture, for this subject which is not covered in this document,

please refer to IEC 62396-4 [2].

NOTE 2 In addition to the high energy neutrons some devices can have a soft error rate due to low energy (<1 eV)

thermal neutrons. For this subject which is not covered in this document, please refer to IEC 62396-5 [3].

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

None.

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

3.1

critical charge

Qcrit

smallest charge that will cause a SEE if injected or deposited in the sensitive volume

3.2

single-event upset

SEU

in a semiconductor device when the radiation absorbed by the device is sufficient to change a

cell’s logic state

Note 1 to entry: After a new write cycle, the original state can be recovered.

3.3

multiple bit upset

MBU

energy deposited in the silicon of an electronic component by a single ionising particle

causing more than one bit in the same word to be upset

Note 1 to entry: The definition of MBU has been updated due to the introduction of the definition of MCU.

3.4

multiple cell upset

MCU

energy deposited in the silicon of an electronic component by a single ionising particle

inducinges several bits in an integrated circuit (IC) to be upset at one time

3.5

soft error

erroneous output signal from a latch or memory cell that can be corrected by performing one

or more normal functions of the device containing the latch or memory cell

Note 1 to entry: As commonly used, the term refers to an error caused by radiation or electromagnetic pulses and

not to an error associated with a physical defect introduced during the manufacturing process.

Note 2 to entry: Soft errors can be generated from SEU, SEFI, MBU, MCU, and or SET. The term SER has been

adopted by the commercial industry while the more specific terms SEU, SEFI, etc. are typically used by the

avionics, space and military electronics communities.

Note 3 to entry: The term “soft error” was first introduced (for DRAMs and ICs) by May and Woods of Intel in their

April 1978 paper at the IRPS and the term “single event upset” was introduced by Guenzer, Wolicki and Allas of

NRL in their 1979 NSREC paper (SEU of DRAMs by neutrons and protons).

3.6

single event effect

SEE

response of a component caused by the impact of a single energetic particle

Note 1 to entry: Examples of energetic particle include galactic cosmic rays, solar energetic particles, energetic

neutrons and protons

Note 2 to entry: The range of responses can include both non-destructive (for example upset) and destructive (for

example latch-up or gate rupture) phenomena.

3.7

single-event hard error

SHE

single event induced hard error

irreversible change in operation from a single radiation event that is typically associated with

permanent damage to one or more of the device elements

Note 1 to entry: Examples include permanently stuck-bit in the device and gate oxide rupture.

3.8

soft error, power cycle

PCSE

soft error that is not corrected by repeated reading or writing but can be corrected by the

removal of power

3.9

flux

time rate of flow of particle energy emitted from or incident on a surface,

divided by the area of that surface

Note 1 to entry: The flux is usually expressed in particles per square centimetre second (N/cm s) or particles per

square centimetre hour (N/cm h).

3.10

soft error rate

SER

rate at which soft errors are occurring

– 8 – IEC 60749-44:2016 © IEC 2016

3.11

failure in time

FIT

failure in 10 device-hours

3.12

firm fault

failure that cannot be reset other than by rebooting the system or by cycling the power to the

relevant functional element

3.13

hard fault

at the aircraft function level, permanent failure of a component within an LRU

Note 1 to entry: A hard fault results in the removal of the LRU affected and the replacement of the permanently

damaged component before a system/system architecture can be restored to full functionality. Such a fault can

impact the value for the MTBF of the LRU repaired.

3.14

single event burnout

SEB

burnout of a powered electronic component or part thereof as a result of the energy

absorption triggered by an individual radiation event

3.15

single event functional interrupt

SEFI

occurrence of an upset, usually in a complex device, such that a control path is corrupted,

leading the part to cease to function properly

Note 1 to entry: Examples of a complex device include microprocessors.

Note 2 to entry: This effect has sometimes been referred to as lockup, indicating that sometimes the part can be

put into a “frozen” state.

3.16

single event gate rupture

SEGR

event in the gate of a powered insulated gate component when the radiation charge absorbed

by the device is sufficient to cause gate rupture, which is destructive

3.17

single event latch up

SEL

event in a four layer semiconductor device when the radiation absorbed by the device is

sufficient to cause a node within the powered semiconductor device to be held in a fixed state

whatever input is applied until the device is de-powered

Note 1 to entry: Such latch up can be destructive or non-destructive

3.18

single event transient

SET

momentary voltage excursion (voltage spike) at a node in an integrated circuit caused by a

single energetic particle strike

Note 1 to entry: The specific terms ASET analogue single event transient and DSET digital single event transient

can be used.

3.19

analogue single event transient

ASET

spurious signal or voltage produced at the output of an analogue device by the deposition of

charge by a single particle

3.20

digital single event transient

DSET

spurious digital signal or voltage, induced by the deposition of charge by a single particle that

can propagate through the circuit path during one clock cycle

3.21

multiple bit upset

MBU

energy deposited in the silicon of an electronic component by a single ionising particle

causing upset of more than one bit in the same word

3.22

cross section

σ

combination of a sensitive area and probability of an interaction depositing the critical charge

for a SEE

The cross section (σ) is calculated using the following formula:

σ = N / Ф

Where N, is the number of errors and Ф, the particle fluence

Note 1 to entry: The units for cross section are cm per device or per bit.

3.23

multiple-cell upset

MCU

event that induces several bits to fail at one time

Note 1 to entry: MCU consists of multiple-cell error bits which are usually but not always adjacent.

3.24

single bit upset

SBU

in a semiconductor device when the radiation absorbed by the device is sufficient to change a

single cell’s logic state

Note 1 to entry: After a new write cycle, the original state can be recovered.

4 Test apparatus

4.1 Measurement equipment

The equipment shall be capable of measuring the functions of the integrated circuit devices,

and capable of measuring the time taken for the change of stored data or other events by the

exposure to energetic particles, such as neutrons, protons and alpha radiation to take place

(i.e. the generation of a soft error). Alternatively, the test equipment (memory tester, etc.)

shall have the capability of counting the number of soft errors in unit time. The equipment

shall be capable of identifying when hard or firm faults occur; although these events are in

general less frequent, their impact is higher.

– 10 – IEC 60749-44:2016 © IEC 2016

NOTE The standard IEC 60749-38 contains a non-accelerated real-time soft error test.

4.2 Radiation source

In order to perform accelerated terrestrial SER measurements, a radiation source(s) is

required that is similar to the energy spectrum of terrestrial cosmic rays. This can be

accomplished by a broad spectrum beam or by using multiple mono-energetic beams. The

radiation beam or beams should cover the whole spectrum of atmospheric radiation taking

into account the energy differences in the various beams. Special attention is to be taken with

respect to the effects of scattered radiation from the beam on the test setup. Technical

personnel operating the facility are to be consulted in terms of the relative flux of the forward

and backward scattering distribution of the beam. They shall also be consulted on

effectiveness of shielding materials for the main beam and scattered beam attenuation. The

number of boards in front of the device under test (DUT) and the distance from the counter

shall be recorded to be used in attenuation calculations. The results of the testing shall be

due to radiation effects on the DUT and not from interaction of radiation with other

components in the test. In particular, power supplies can be vulnerable to radiation-induced

avalanche breakdown. Sensitive electronic circuits in the tester and any device on the DUT

board (e.g., buffers or registers) can also be affected. These components are to be moved as

far from the primary and scattered beam as possible or appropriate shielding is to be used.

Care is to be taken that the tester and power supply are not affected by scattered radiation

from the beam before conducting tests in a new facility or before conducting tests with a new

tester setup (including modified shielding of the tester). To assure this, the tester is to be

positioned and shielded in exactly the same way as during actual tests except for the DUT

that shall be positioned outside the beam or shielded from the beam. With the beam on and

the DUT shielded or otherwise not exposed to the beam, test the DUT. Tester setup

verification is successful if no failures are observed. Unless otherwise specified, this tester

setup verification test shall last as long as a typical test. Care shall be taken to prevent upsets

from stray signals or noise in the cables to the DUT. A tester readiness check shall be

performed as part of the test sequence to assure electrical noise immunity.

4.3 Test sample

Any type of integrated circuits with memory can be tested. The device parameters

(capacitance of the memory cell in the DRAM, etc.) which can affect the soft error rate shall

be well understood. Modern complex devices including application specific integrated circuits

(ASIC) and field programmable gate arrays (FPGA) can contain more than one type of

memory. These can have very different radiation upset sensitivities. FPGA as an example will

generally contain configuration memory, register (flip/flop) memory and composite SRAM

memory. An ASIC for example generally contains register (flip/flop) memory and composite

SRAM memory. It is important that the distinction is recognised between these elements and

each of the SEE rates determined separately for each type of memory bit.

5 Procedure neutron irradiated soft error test

5.1 Surface preparation

The mould compound of the DUT does not need to be etched off because the range of

neutron beam in the device is sufficiently long.

5.2 Power supply voltage

Unless otherwise required, the power supply voltage shall be the nominal operating conditions

specified for the device.

In order to characterize cosmic ray sensitivity as a function of Qcrit (the minimum charge

needed to upset a memory cell), lower and higher voltages are also permitted.

5.3 Ambient temperature

Unless otherwise required in any specification, the ambient temperature shall be the nominal

operating conditions specified for the device.

5.4 Core cycle time

The core cycle time is dependent on the samples under test (when required, the core cycle

time dependence shall be measured).

5.5 Data pattern

This is dependent on the samples under test. The structure of the data patterns shall be

recorded (a checker board, all 0/1-read/write pattern, etc).

Record the impact of data patterns on the observed rates.

5.6 Number of measurement samples

Multiple samples shall be measured to take into account measurement variation. If test

samples are mounted along the beam line with samples behind the first sample, the beam

fluence shall be calculated at each test location allowing for beam attenuation at that sample.

The maximum variation in flux between different parts in the sample shall not exceed 20 %.

5.7 Calculations for time required in the beam

Information shall be provided on how to calculate, to a specified accuracy, the amount of time

required in the beam, to obtain the required neutron fluence. This will be based on beam type

and beam flux. Some suitable neutron beam test facilities are included in Annex B.

6 Evaluation

6.1 Measurement and failure rate estimation

The set-up of DUTs and the measuring system are the same as for the other accelerated tests.

The effective SEU cross section σ over the specific range of energy can be defined as

eff

follows:

N

err

(1)

σ =

eff

Φ(E , E )

min max

where

N is total number of errors counted per device;

err

–2

Φ (E , E -) is the total fluence in the energy range from E to E . (neuton × cm ).

min max min max

On the condition that the shape of the white neutron spectrum is close enough to the field

spectrum, Soft error rate (SER) or single event effect rate (SEE rate) can be estimated by

SER=σ f (E , E ) (2)

eff field min max

where

-2 -1

f (E , E ) is the neutron flux in the field (neuton.cm .s ).

field min max

– 12 – IEC 60749-44:2016 © IEC 2016

6.2 Determination of MCU and MBU cross sections

These cross sections are determined by analysing the errors in the memory if two or more

errors occur during the same read cycle or in an adjacent read cycle (see Note below) then

these are caused by the same neuron event. The MCU cross section is the number of these

multiple events divided by the fluence. The number of MBU events can be determined by

inspection, these occur when more than 1 bit is upset in the same logical word. The neutron

flux and related event rate shall not be too high (the probability should be 100 or more times

smaller than the single event MCU probability) to avoid multiple upset caused by more than

one neutron in the same clock cycle.

NOTE If the neutron event causes SEU in two separate words (i.e. MCU) after the first word has been read in the

cycle, then the two SEU will be identified in adjacent read cycles.

6.3 Determination of device FIT (event rate) from cross section

Upset data expressed as FIT/Mbit can be converted to a cross section in units of cm²/bit by

using the conversion factor 7,7E-17 Mbit.cm /(FIT per bit), and to a device cross section in

2 2

units of cm /device by using the conversion factor 7,7E-11 cm /(FIT per device), both of

-2 -1

which are based on a neutron flux (E> 10 MeV) of 13 netron.cm .hr at New York City, NYC.

A device upset rate of one FIT due to SEU equates to a device cross section of 7,7E-11 cm

[8].

The device NYC FIT rate for a single event effect is determined from the device cross section

-2

for that effect multiplied by 1,3 E + 10 cm .

7 Summary

The following information shall be specified in the applicable procurement document

(additional detail on these requirements is given in Annex A):

a) sample size;

b) vehicle description;

c) test description;

d) values of relevant test stress conditions for example voltage, operating frequency;

e) test results provided for each SEE type tested. Cross section data on per bit or per device

for all SEE measured including SEU, MBU, MCU, SEL, SEFI, SET.

Annex A

(informative)

Additional information for the

applicable procurement specification

A.1 General

The information provided in Clauses A.2 to A.5 may additionally be specified in the applicable

procurement document (see Clause 6).

A.2 Description of the beam source

The description of the beam source can include the following elements:

1) facility and location, facility contact information, description of the source generation,

particle type (neutron, proton);

2) beam energy (mono-energetic) or energy spectrum description;

3) filters used, if any (e.g., cadmium strip or borated shield for thermal neutrons);

4) variation in beam flux or fluence during testing, including description of the monitor

technique or method of estimation;

5) description of beam with respect to each DUT, including:

a) beam flux density at DUT;

b) beam area and uniformity of beam across DUT;

c) DUT orientation to incident beam;

d) attenuating factors, including a description of the types and thicknesses for materials

between the tested silicon chip and the beam source if the thickness is not uniform or if

the uniform thickness attenuates the energy of the beam incident on the silicon

(includes attenuation from component packaging, heat sinks and thermal

enhancements, other tested devices, test fixtures and includes effects of materials

containing B-10).

A.3 Description of the sample and test vehicle

A.3.1 Sample size

The sample size (number of devices) tested may also include information on the circuits

(array sizes, scan chain size, etc.) tested on each device.

A.3.2 Vehicle description

The vehicle description may include the following elements:

1) circuit type and sub-element (e.g., SRAM, DRAM, flip-flop master, flip-flop slave);

2) package description (e.g., connection to chip, materials, and geometries), including any

modifications made for SER testing (e.g., non-standard heatsink);

– 14 – IEC 60749-44:2016 © IEC 2016

3) supplier part number (and die revision, if applicable);

4) operational description of the circuit;

5) ECC description (type and coverage) or “tested per data sheet” if the ECC is unknown”.

A.4 Test description

The test description may include the following elements:

1) voltage (external supply, use of internal regulated, back bias if applicable);

NOTE 1 Reporting an internal regulated voltage level is optional, but encouraged where the portability of the

data to other devices is of interest.

2) test pattern(s), including logical data pattern and, if known, the physical data pattern;

3) fluence and test duration;

4) core cycle time or frequency with special notation of cycle times different than product

data sheet (for dynamic test) or designation as “static”;

5) refresh rate, where applicable;

6) temperature during test (at minimum, ambient temperature; if available, junction

temperature as well. Report the means for determining the junction temperature);

7) which source and energy are used, if multiple sources and energies are used;

8) tester (commercial model and/or physical description);

9) problems or unusual behavior of the devices during test;

10) fail information:

i) count of each error type (transient soft errors, static soft errors, hard errors);

NOTE 2 Because test durations are often relatively short, hard error observations are typically

exceptional. Where total dose effects drive those errors, they are test artifacts only and those

observations are specially identified as such.

ii) identification of those soft errors that are multiple-cell errors;

iii) electrical signature of hard and firm errors / faults;

iv) failing logical address or addresses;

NOTE 3 Interpretation of multi-cell errors is enhanced by an understanding of the physical relationship of

failing addresses.

v) test conditions (voltage, ECC usage, data pattern, etc.) where multiple conditions are

applied within the same test;

vi) failure rate in test condition. Ideally, the failure rate shall be identified on both a per-bit

(or other circuit element) basis as well as a per-event basis. At minimum, the basis for

any given failure rate shall be clearly identified.

11) periodicity of test readouts;

12) the measured SER; where available, it includes the single-bit and multi-bit components

and a description of how the multi-bit component was determined;

13) for devices intended for harsh environments the electrical signature and sensitivity of hard

and firm errors / faults are to be determined under worst case conditions. For example

SEL devices are generally at greatest sensitivity (rate) when supply voltage and

temperature are at their highest operating limits.

A.5 Test results

The test results may include the following elements:

1) the measured SEE rate and SEE cross section(s) at the DUT locations if DUTs are not

uniform in their exposure to the beam (e.g. stacked DUTs, differing distances from the

beam);

2) where observed, fully categorize by a) single-cell upset, b) multi-cell errors, c) latch up, d)

address or command errors, e) upset of redundancy latches and provide a description of

how these elements were determined;

3) linearity which shows the failure rate proportionality to the flux density;

4) multiple errors – demonstrate multiple errors are from single energetic events.

– 16 – IEC 60749-44:2016 © IEC 2016

Annex B

(informative)

White neutron test apparatus

White neutron spectrum can be obtained by bombarding high energy protons at a relatively

thick target of, typically, tungsten or lead, which simulates terrestrial neutron spectrum at the

ground. The beam line 4FP30L at Los Alamos Neutron Science Center (LANSCE) is widely

known and used as such a neutron source. As shown in Figure B.1, the neutron spectrum in

the beam line is well defined over 1 MeV by the combination of a fission chamber and a TOF

6 -2 -1

(Time Of Flight) system. The neutron flux is in the range of as high as 10 neutron.cm .s .

The white neutron beam line at Research Center for Nuclear Physics (RCNP) has been in

5 -2 -1

operation since 2004. A neutron beam with flux of 6 × 10 neutron.cm .s is available using

a 400 MeV proton beam. The neutron energy spectrum is shown in Figure B.2, which was

measured by a TOF method using liquid scintillators. A Comparison of LANSCE (WNR) and

TRIUMF neutron spectra with terrestrial neutron spectrum is shown in Figure B.3.

The neutron energy spectrum of the atmospheric radiation exceeds 100 MeV and facilities

used for white neutron testing of devices shall have an upper energy range of greater than

100 MeV to ensure that the beam is representative. Additional neutron beam facilities for

white neutron testing are ANITA, at TSL, Uppsala, Sweden maximum energy 180 MeV, NIF at

TRIUMF, Vancouver, Canada maximum energy 400 MeV and ISIS, Chipir at RAL, Harwell, UK

maximum energy 800 MeV.

1 000

Non shield

5,08 mm (2’’)

100 10,16 mm (4’’)

20,32 mm (8’’)

0,1

0,01

0,001

1 10 100 1 000

Neutron energy (MeV)

IEC

Figure B.1 – Typical white neutron spectra with

different shield (polyethylene) thickness

Differential neutron flux (arb. units)

1 × 10

1 × 10

1 × 10

1 × 10

LANSCE

RCNP

1 × 10

Cosmic ray × 2,4 × 10

1 × 10

1 10 100 1 000

Neutron energy (MeV)

IEC

Figure B.2 – Typical neutron spectrum

0 1 2 3

10 10 10 10

Neutron energy (MeV)

IEC

Key

Facility Multiplication Factor

Ground Spectrum [latitude 45º North]

Line plot is ground level multiplied by 3 × 10

ICE House (WNR) Measured Spectrum 2005 1

TRIUMF at 100 µA

Figure B.3 – Comparison of LANSCE (WNR) and TRIUMF

neutron spectra with terrestrial neutron spectrum

-2 -1 -1

-2 -1 -1

Differential neutron flux (neutron × cm × sec × MeV )

Differential neutron flux (neutron × cm × sec × MeV )

– 18 – IEC 60749-44:2016 © IEC 2016

Annex C

(informative)

Failure rate calculation

C.1 An influence of soft error for actual semiconductor devices

C.1.1 General

Derating with a consideration of semiconductor device and its application using conditions

may be applied to extract actual soft error rate. In Annex C, the derating method is provided.

C.1.2 Duty derating

Normal soft error rate calculation is done based on the power-on time of the devices.

Therefore, its error rate can be decreased by inverse proportion of the time and this

procedure is called as “Duty derating”.

For example, soft error rate of an application with 8 hours operating in a day becomes one

third (1/3).

In Figure C.1 device A is an example of a case of non derated condition with “Duty

derating = 1” and device B is an example of a case of derated condition. “Duty derating = 1/3”.

Device A

24 hours / day working factor = 24/24 = 1

Device B

8h 16h 8h 16h 8h 16h

8 hours / day working factor =8/24 = 1/3

IEC

Figure C.1 – Schematic image of duty derating

C.1.3 Utility derating

In general, all of memory area is not always used. The proportion of used data area and not

used data area in memory is called as “utility derating”. This derating rate needs to consider

the various situations. Those are non-programed area, ineffective data area of programmed

data and ineffective time rate of programmed data. This calculation may be complicated in the

application, so averaging is also available.

Not

Used

Used

used

X (FIT) X/2 (FIT)

IEC IEC

a) All area used “Utility derating = 1 b) Half area used “Utility derating = 1/2

Figure C.2 – Schematic image of memory effective area for utility derating

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...