IEC 60749-27:2006

(Main)Semiconductor devices - Mechanical and climatic test methods - Part 27: Electrostatic discharge (ESD) sensitivity testing - Machine model (MM)

Semiconductor devices - Mechanical and climatic test methods - Part 27: Electrostatic discharge (ESD) sensitivity testing - Machine model (MM)

Establishes a standard procedure for testing and classifying semiconductor devices according to their susceptibility to damage or degradation by exposure to a defined machine model (MM) electrostatic discharge (ESD). It may be used as an alternative test method to the human body model ESD test method. The objective is to provide reliable, repeatable ESD test results so that accurate classifications can be performed. This test method is applicable to all semiconductor devices and is classified as destructive

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques - Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) - Modèle de machine (MM)

Etablit une procédure normalisée pour les essais et les classements des dispositifs à semiconducteurs en fonction de leur sensibilité aux dommages ou à la dégradation du fait de leur exposition à une décharge électrostatique (DES) sur un modèle de machine (MM) défini. Elle peut être utilisée comme une méthode d'essai en variante à la méthode d'essai de DES sur le modèle du corps humain. L'objectif est de fournir des résultats d'essai de DES fiables et reproductibles de manière à ce que des classifications précises puissent être réalisées. Cette méthode d'essai est applicable à tous les dispositifs à semiconducteurs et elle est classée destructive.

General Information

- Status

- Published

- Publication Date

- 17-Jul-2006

- Technical Committee

- TC 47 - Semiconductor devices

- Current Stage

- PPUB - Publication issued

- Start Date

- 18-Jul-2006

- Completion Date

- 15-Sep-2006

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 60749-27:2006 is an international standard developed by the International Electrotechnical Commission (IEC) that specifies mechanical and climatic test methods for semiconductor devices, focusing on electrostatic discharge (ESD) sensitivity testing using the Machine Model (MM). This standard establishes a uniform, repeatable, and reliable procedure for evaluating the susceptibility of semiconductor devices to damage or degradation caused by MM-type ESD exposure. It provides an important alternative to the Human Body Model (HBM) ESD test (covered under IEC 60749-26), enabling manufacturers and test engineers to classify semiconductor products accurately based on their ESD robustness.

The MM ESD test method is especially significant for modern semiconductor device quality control to prevent failure during manufacturing, handling, or deployment phases. This test method is classified as destructive, meaning the devices tested are exposed to high stresses that may cause permanent damage to assess their limits effectively.

Key Topics

Scope and Application:

IEC 60749-27 applies to all semiconductor devices, focusing on mechanical and climatic test methods that assess ESD sensitivity via the Machine Model. It serves as an alternative to the Human Body Model but delivers distinct results due to different test conditions and waveform characteristics.Test Equipment and Waveform Generation:

The standard specifies the use of an MM ESD waveform generator capable of producing defined ESD current pulses. The generator typically includes a nominal 200 pF capacitor, a discharge switch, and specified evaluation loads - a shorting wire and a 500 Ω resistor with tight tolerances. Waveform verification requires a recording system and current transducer with a minimum 350 MHz bandwidth to capture the high-speed ESD discharge accurately.Waveform Requirements and Verification:

MM ESD current waveforms must meet strict criteria regarding rise time, peak current, and pulse duration to ensure consistency and relevance. The verification process uses the evaluation loads to confirm that the waveform generator functions correctly and produces repeatable results.Device Testing and Classification:

The standard details test sample size, pin combinations, test order, and stress levels. Devices are tested for failure under increasing MM ESD voltages and classified based on the maximum withstand voltage that does not cause failure. Failure criteria are clearly defined as any parameter deviation beyond specified limits due to ESD stress.Relation to Other Standards:

IEC 60749-27 references IEC 60749-26 for the Human Body Model and IEC 61340-3-2 for machine model electrostatic discharge waveforms. It integrates related procedures and definitions for comprehensive ESD testing in semiconductor devices.

Applications

Semiconductor Manufacturing:

Using IEC 60749-27 ensures that devices meet stringent ESD immunity requirements prior to packaging and shipment, reducing field failures caused by inadvertent ESD events during handling or assembly.Quality Control and Product Reliability:

The standard provides a validated test method to classify devices for ESD robustness, enabling manufacturers to specify protection levels and implement suitable mitigation strategies in device design or packaging.Research and Development:

Designers and engineers leverage MM ESD testing to evaluate device vulnerability and improve layout, materials, and circuit protection tailored to withstand realistic machine-generated ESD stresses.ESD Protection Component Qualification:

Components intended for electrostatic discharge protection, such as diodes and resistors, are tested using the MM method to confirm their ability to reliably dissipate machine-model ESD pulses.

Related Standards

IEC 60749-26 – Human Body Model (HBM) ESD Testing:

Complementary to IEC 60749-27, this standard tests ESD sensitivity simulating static discharge from a human body, with different waveform characteristics.IEC 61340-3-2 – Electrostatics – Machine Model Waveforms:

Provides detailed MM ESD test waveforms and procedures used in conjunction with IEC 60749-27 for device-level component testing.IEC 60749 Series – Mechanical and Climatic Test Methods for Semiconductors:

A series covering various environmental and mechanical testing protocols ensuring device reliability under different stresses.

Summary

IEC 60749-27:2006 establishes a critical, internationally recognized protocol for machine model (MM) electrostatic discharge testing in semiconductor devices. By defining precise test methodologies, equipment requirements, and classification criteria, the standard helps maintain device performance and reliability in environments susceptible to ESD events. Adoption of this standard contributes significantly to reducing device failures during manufacturing and in the field, making it invaluable for engineers, quality assurance professionals, and manufacturers involved in semiconductor design and testing.

Keywords: IEC 60749-27, machine model ESD, semiconductor devices, electrostatic discharge sensitivity, MM ESD test, semiconductor testing standard, ESD classification, device reliability, ESD waveform generator, IEC standards for ESD

Buy Documents

IEC 60749-27:2006 - Semiconductor devices - Mechanical and climatic test methods - Part 27: Electrostatic discharge (ESD) sensitivity testing - Machine model (MM)

IEC 60749-27:2006+AMD1:2012 CSV - Semiconductor devices - Mechanical and climatic test methods - Part27: Electrostatic discharge (ESD) sensitivity testing - Machine model (MM) Released:9/25/2012 Isbn:9782832204078

Frequently Asked Questions

IEC 60749-27:2006 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Mechanical and climatic test methods - Part 27: Electrostatic discharge (ESD) sensitivity testing - Machine model (MM)". This standard covers: Establishes a standard procedure for testing and classifying semiconductor devices according to their susceptibility to damage or degradation by exposure to a defined machine model (MM) electrostatic discharge (ESD). It may be used as an alternative test method to the human body model ESD test method. The objective is to provide reliable, repeatable ESD test results so that accurate classifications can be performed. This test method is applicable to all semiconductor devices and is classified as destructive

Establishes a standard procedure for testing and classifying semiconductor devices according to their susceptibility to damage or degradation by exposure to a defined machine model (MM) electrostatic discharge (ESD). It may be used as an alternative test method to the human body model ESD test method. The objective is to provide reliable, repeatable ESD test results so that accurate classifications can be performed. This test method is applicable to all semiconductor devices and is classified as destructive

IEC 60749-27:2006 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60749-27:2006 has the following relationships with other standards: It is inter standard links to IEC 60749-27:2006/AMD1:2012, IEC 60749-27:2003. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60749-27:2006 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE

IEC

60749-27

INTERNATIONAL

Deuxième édition

STANDARD

Second edition

2006-07

Dispositifs à semiconducteurs –

Méthodes d'essais mécaniques

et climatiques –

Partie 27:

Essai de sensibilité aux décharges

électrostatiques (DES) –

Modèle de machine (MM)

Semiconductor devices –

Mechanical and climatic test methods –

Part 27:

Electrostatic discharge (ESD) sensitivity

testing –

Machine model (MM)

Numéro de référence

Reference number

CEI/IEC 60749-27:2006

Numérotation des publications Publication numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. Ainsi, la CEI 34-1 issued with a designation in the 60000 series. For

devient la CEI 60034-1. example, IEC 34-1 is now referred to as IEC 60034-1.

Editions consolidées Consolidated editions

Les versions consolidées de certaines publications de la The IEC is now publishing consolidated versions of its

CEI incorporant les amendements sont disponibles. Par publications. For example, edition numbers 1.0, 1.1

exemple, les numéros d’édition 1.0, 1.1 et 1.2 indiquent and 1.2 refer, respectively, to the base publication,

respectivement la publication de base, la publication de the base publication incorporating amendment 1 and

base incorporant l’amendement 1, et la publication de the base publication incorporating amendments 1

base incorporant les amendements 1 et 2. and 2.

Informations supplémentaires Further information on IEC publications

sur les publications de la CEI

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. Des renseignements relatifs à the content reflects current technology. Information

cette publication, y compris sa validité, sont dispo- relating to this publication, including its validity, is

nibles dans le Catalogue des publications de la CEI available in the IEC Catalogue of publications

(voir ci-dessous) en plus des nouvelles éditions, (see below) in addition to new editions, amendments

amendements et corrigenda. Des informations sur les and corrigenda. Information on the subjects under

sujets à l’étude et l’avancement des travaux entrepris consideration and work in progress undertaken by the

par le comité d’études qui a élaboré cette publication, technical committee which has prepared this

ainsi que la liste des publications parues, sont publication, as well as the list of publications issued,

également disponibles par l’intermédiaire de: is also available from the following:

• Site web de la CEI (www.iec.ch) • IEC Web Site (www.iec.ch)

• Catalogue des publications de la CEI • Catalogue of IEC publications

Le catalogue en ligne sur le site web de la CEI The on-line catalogue on the IEC web site

(www.iec.ch/searchpub) vous permet de faire des (www.iec.ch/searchpub) enables you to search by a

recherches en utilisant de nombreux critères, variety of criteria including text searches,

comprenant des recherches textuelles, par comité technical committees and date of publication. On-

d’études ou date de publication. Des informations en line information is also available on recently

ligne sont également disponibles sur les nouvelles issued publications, withdrawn and replaced

publications, les publications remplacées ou retirées, publications, as well as corrigenda.

ainsi que sur les corrigenda.

• IEC Just Published • IEC Just Published

Ce résumé des dernières publications parues This summary of recently issued publications

(www.iec.ch/online_news/justpub) est aussi dispo- (www.iec.ch/online_news/justpub) is also available

nible par courrier électronique. Veuillez prendre by email. Please contact the Customer Service

contact avec le Service client (voir ci-dessous) Centre (see below) for further information.

pour plus d’informations.

• Service clients • Customer Service Centre

Si vous avez des questions au sujet de cette If you have any questions regarding this

publication ou avez besoin de renseignements publication or need further assistance, please

supplémentaires, prenez contact avec le Service contact the Customer Service Centre:

clients:

Email: custserv@iec.ch Email: custserv@iec.ch

Tél: +41 22 919 02 11 Tel: +41 22 919 02 11

Fax: +41 22 919 03 00 Fax: +41 22 919 03 00

.

NORME CEI

INTERNATIONALE

IEC

60749-27

INTERNATIONAL

Deuxième édition

STANDARD

Second edition

2006-07

Dispositifs à semiconducteurs –

Méthodes d'essais mécaniques

et climatiques –

Partie 27:

Essai de sensibilité aux décharges

électrostatiques (DES) –

Modèle de machine (MM)

Semiconductor devices –

Mechanical and climatic test methods –

Part 27:

Electrostatic discharge (ESD) sensitivity

testing –

Machine model (MM)

IEC 2006 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in any

utilisée sous quelque forme que ce soit et par aucun procédé, form or by any means, electronic or mechanical, including

électronique ou mécanique, y compris la photocopie et les photocopying and microfilm, without permission in writing from

microfilms, sans l'accord écrit de l'éditeur. the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

CODE PRIX

M

PRICE CODE

Commission Electrotechnique Internationale

International Electrotechnical Commission

МеждународнаяЭлектротехническаяКомиссия

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 60749-27 CEI:2006

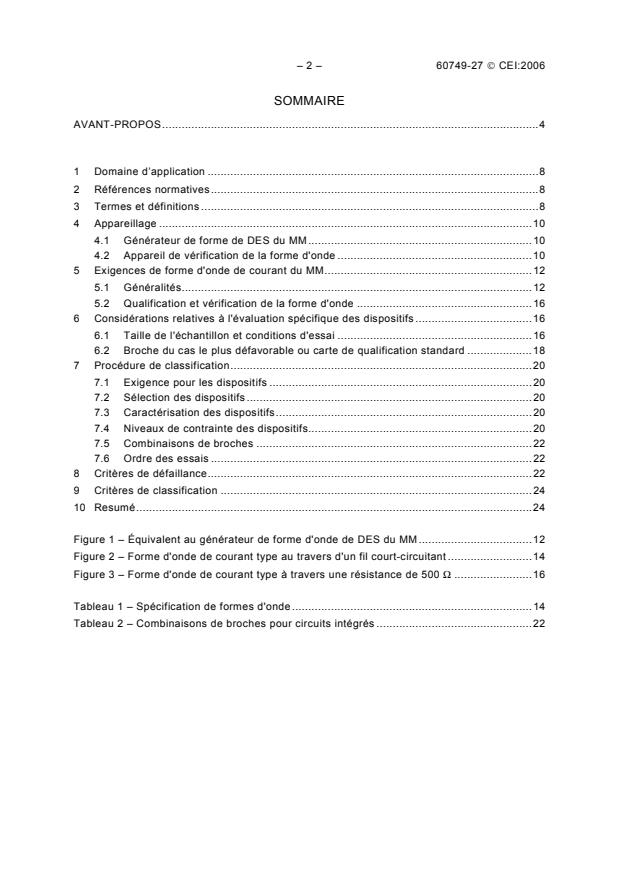

SOMMAIRE

AVANT-PROPOS.4

1 Domaine d’application .8

2 Références normatives.8

3 Termes et définitions .8

4 Appareillage .10

4.1 Générateur de forme de DES du MM.10

4.2 Appareil de vérification de la forme d'onde .10

5 Exigences de forme d'onde de courant du MM.12

5.1 Généralités.12

5.2 Qualification et vérification de la forme d'onde .16

6 Considérations relatives à l'évaluation spécifique des dispositifs .16

6.1 Taille de l'échantillon et conditions d'essai .16

6.2 Broche du cas le plus défavorable ou carte de qualification standard .18

7 Procédure de classification.20

7.1 Exigence pour les dispositifs .20

7.2 Sélection des dispositifs .20

7.3 Caractérisation des dispositifs.20

7.4 Niveaux de contrainte des dispositifs.20

7.5 Combinaisons de broches .22

7.6 Ordre des essais .22

8 Critères de défaillance.22

9 Critères de classification .24

10 Resumé.24

Figure 1 – Équivalent au générateur de forme d'onde de DES du MM.12

Figure 2 – Forme d'onde de courant type au travers d'un fil court-circuitant .14

Figure 3 – Forme d'onde de courant type à travers une résistance de 500 Ω .16

Tableau 1 – Spécification de formes d'onde.14

Tableau 2 – Combinaisons de broches pour circuits intégrés .22

60749-27 IEC:2006 – 3 –

CONTENTS

FOREWORD.5

1 Scope.9

2 Normative references .9

3 Terms and definitions .9

4 Equipment .11

4.1 MM ESD waveform generator .11

4.2 Waveform verification equipment.11

5 MM current waveform requirements.13

5.1 General .13

5.2 Waveform qualification and verification .17

6 Device specific evaluation considerations.17

6.1 Sample size and test conditions .17

6.2 Worst-case pin or standard qualification board .19

7 Classification procedure .21

7.1 Device requirements .21

7.2 Device selection .21

7.3 Device characterization .21

7.4 Device stress levels .21

7.5 Pin combinations .23

7.6 Order of test.23

8 Failure criteria .23

9 Classification criteria .25

10 Summary.25

Figure 1 – MM ESD waveform generator equivalent.13

Figure 2 – Typical current waveform through a shorting wire.15

Figure 3 – Typical current waveform through a 500 Ω resistor.17

Table 1 – Waveform specification .15

Table 2 – Pin combinations for integrated circuits .23

– 4 – 60749-27 CEI:2006

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

____________

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) –

Modèle de machine (MM)

AVANT-PROPOS

1) La Commission Electrotechnique Internationale (CEI) est une organisation mondiale de normalisation

composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a

pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les

domaines de l'électricité et de l'électronique. A cet effet, la CEI – entre autres activités – publie des Normes

internationales, des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au

public (PAS) et des Guides (ci-après dénommés "Publication(s) de la CEI"). Leur élaboration est confiée à des

comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les

organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent

également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO),

selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux de la CEI

intéressés sont représentés dans chaque comité d’études.

3) Les Publications de la CEI se présentent sous la forme de recommandations internationales et sont agréées

comme telles par les Comités nationaux de la CEI. Tous les efforts raisonnables sont entrepris afin que la CEI

s'assure de l'exactitude du contenu technique de ses publications; la CEI ne peut pas être tenue responsable

de l'éventuelle mauvaise utilisation ou interprétation qui en est faite par un quelconque utilisateur final.

4) Dans le but d'encourager l'uniformité internationale, les Comités nationaux de la CEI s'engagent, dans toute la

mesure possible, à appliquer de façon transparente les Publications de la CEI dans leurs publications

nationales et régionales. Toutes divergences entre toutes Publications de la CEI et toutes publications

nationales ou régionales correspondantes doivent être indiquées en termes clairs dans ces dernières.

5) La CEI n’a prévu aucune procédure de marquage valant indication d’approbation et n'engage pas sa

responsabilité pour les équipements déclarés conformes à une de ses Publications.

6) Tous les utilisateurs doivent s'assurer qu'ils sont en possession de la dernière édition de cette publication.

7) Aucune responsabilité ne doit être imputée à la CEI, à ses administrateurs, employés, auxiliaires ou

mandataires, y compris ses experts particuliers et les membres de ses comités d'études et des Comités

nationaux de la CEI, pour tout préjudice causé en cas de dommages corporels et matériels, ou de tout autre

dommage de quelque nature que ce soit, directe ou indirecte, ou pour supporter les coûts (y compris les frais

de justice) et les dépenses découlant de la publication ou de l'utilisation de cette Publication de la CEI ou de

toute autre Publication de la CEI, ou au crédit qui lui est accordé.

8) L'attention est attirée sur les références normatives citées dans cette publication. L'utilisation de publications

référencées est obligatoire pour une application correcte de la présente publication.

9) L’attention est attirée sur le fait que certains des éléments de la présente Publication de la CEI peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 60749-27 a été établie par le comité d'études 47 de la CEI:

Dispositifs à semiconducteurs.

Cette deuxième édition annule et remplace la première édition, publiée en 2003, et a été

révisée en collaboration avec le comité d’études 101. Bien qu’elle ne contienne pas de

modifications techniques majeures, référence est maintenant faite, si nécessaire, à la

CEI 61340-3-2.

60749-27 IEC:2006 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 27: Electrostatic discharge (ESD) sensitivity testing –

Machine model (MM)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-27 has been prepared by IEC technical committee 47:

Semiconductor devices.

This second edition cancels and replaces the first edition, published in 2003, and has been

revised in collaboration with technical committee 101. Whilst it does not contain any major

technical changes, reference is now made, where necessary, to IEC 61340-3-2.

– 6 – 60749-27 CEI:2006

Le texte de cette norme est issu des documents suivants:

FDIS Rapport de vote

47/1861/FDIS 47/1873/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote ayant

abouti à l'approbation de cette norme.

Cette publication a été rédigée selon les Directives ISO/CEI, Partie 2.

Une liste de toutes les parties de la série CEI 60749, présentées sous le titre général

Dispositifs à semiconducteurs – Méthodes d’essais mécaniques et climatiques peut être

consultée sur le site web de la CEI.

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant la date de

maintenance indiquée sur le site web de la CEI sous "http://webstore.iec.ch" dans les

données relatives à la publication recherchée. A cette date, la publication sera

• reconduite,

• supprimée,

• remplacée par une édition révisée, ou

• amendée.

60749-27 IEC:2006 – 7 –

The text of this standard is based on the following documents:

FDIS Report on voting

47/1861/FDIS 47/1873/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts of IEC 60749 series, under the general title Semiconductor devices –

Mechanical and climatic test methods can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

– 8 – 60749-27 CEI:2006

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) –

Modèle de machine (MM)

1 Domaine d’application

La présente partie de la CEI 60749 établit une procédure normalisée pour les essais et les

classements des dispositifs à semiconducteurs en fonction de leur sensibilité aux dommages

ou à la dégradation du fait de leur exposition à une décharge électrostatique (DES) sur un

modèle de machine (MM) défini. Elle peut être utilisée comme une méthode d'essai en

variante à la méthode d'essai de DES sur le modèle du corps humain. L’objectif est de fournir

des résultats d’essai de DES fiables et reproductibles de manière à ce que des classifications

précises puissent être réalisées.

Cette méthode d'essai est applicable à tous les dispositifs à semiconducteurs et elle est

classée destructive.

L’essai de DES pour les dispositifs à semiconducteurs est choisi entre la présente méthode

d’essai, celle du modèle du corps humain (HBM - voir la CEI 60749-26) ou d'autres méthodes

d'essai de série de la CEI 60749. Les méthodes d’essai MM et HBM donnent des résultats

similaires mais pas identiques. Sauf spécification contraire, la méthode d’essai HBM sera

choisie.

NOTE 1 Cette méthode d’essai ne simule pas vraiment les décharges de machines réelles ou d’outils métalliques

parce que cette méthode utilise une inductance parasite forte du circuit d'essai, alors que les machines réelles ou

les outils métalliques dont le temps de montée de décharge est approximativement 100 ps n’ont pas d’inductance.

NOTE 2 Certains articles de cette méthode d'essai sont conformes à la CEI 61340-3-2.

2 Références normatives

Les documents de référence suivants sont indispensables pour l’application du présent

document. Pour les références datées, seule l’édition citée s’applique. Pour les références

non datées, la dernière édition du document de référence s’applique (y compris les éventuels

amendements.

CEI 61340-3-2, Electrostatique – Partie 3-2: Méthodes pour la simulation des effets

électrostatiques – Formes d'onde d'essai des décharges électrostatiques pour les modèles de

machine (MM)

CEI 60749-26, Dispositifs à semiconducteurs – Méthodes d’essais mécaniques et climatiques

– Partie 26: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle du corps

humain (HBM)

3 Termes et définitions

Pour les besoins du présent document les termes et définitions suivants sont applicables.

3.1

dispositif en essai

DEE

dispositif à semiconducteur soumis à l'essai de DES MM

60749-27 IEC:2006 – 9 –

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 27: Electrostatic discharge (ESD) sensitivity testing –

Machine model (MM)

1 Scope

This part of IEC 60749 establishes a standard procedure for testing and classifying

semiconductor devices according to their susceptibility to damage or degradation by exposure

to a defined machine model (MM) electrostatic discharge (ESD). It may be used as an

alternative test method to the human body model ESD test method. The objective is to

provide reliable, repeatable ESD test results so that accurate classifications can be performed.

This test method is applicable to all semiconductor devices and is classified as destructive.

ESD testing of semiconductor devices is selected from this test method, the human body

model (HBM – see IEC 60749-26) or other test methods in the IEC 60749 series. The MM and

HBM test methods produce similar but not identical results. Unless otherwise specified, the

HBM test method is the one selected.

NOTE 1 This test method does not truly simulate discharge from real machines or metallic tools because the test

method uses high parasitic inductance of the test circuit, whereas real machines and metallic tools, whose

discharge rise time is approximately 100 ps, have no inductance.

NOTE 2 Certain clauses in this test method are in accordance with IEC 61340-3-2.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61340-3-2, Electrostatics – Part 3-2: Methods for simulation of electrostatic effects –

Machine model (MM – Component testing ) electrostatic discharge test waveforms

IEC 60749-26: Semiconductor devices – Mechanical and climatic test methods – Part 26:

Electrostatic discharge (ESD) sensitivity testing – Human body model (HBM)

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

3.1

device under test

DUT

semiconductor product subjected to MM ESD test

– 10 – 60749-27 CEI:2006

3.2

défaillance du DEE

condition pour laquelle un DEE n'est pas conforme à un ou plusieurs paramètres spécifiés à

la fin de l'essai de DES

3.3

tension de tenue de DES

niveau de tension de DES maximum appliqué qui ne provoque pas de dépassement des

limites de défaillance pourvu que tous les DEE soumis à contrainte à des niveaux inférieurs

aient également subi les essais avec succès

NOTE L'Article 3 de cette méthode d'essai est conforme à la CEI 61340-3-2 sauf pour les références particulières

aux dispositifs.

4 Appareillage

4.1 Générateur de forme de DES du MM

Cet appareil produit une impulsion de décharge de courant électrostatique simulant un

événement de DES du MM pour l'application du DEE. Le circuit de générateur de forme

équivalent ainsi que les charges d'évaluation de l'appareil d'essai sont illustrées à la Figure 1.

4.2 Appareil de vérification de la forme d'onde

4.2.1 Généralités

L'appareil capable de vérifier l'impulsion de la forme d'onde de courant du MM est défini dans

la présente norme. Cet appareil comprend, entre autres, un système d'enregistrement de la

forme d'onde, une résistance à haute tension et un transducteur de courant.

4.2.2 Système d'enregistrement de la forme d'onde

Le système d'enregistrement de la forme d'onde doit avoir une largeur de bande à action

unique minimale de 350 MHz.

4.2.3 Charges d'évaluation

Deux charges d'évaluation sont nécessaires pour vérifier la fonctionnalité du générateur de

forme d'onde:

a) charge 1: un fil court-circuitant

b) charge 2: une résistance de 500 Ω à inductance faible de valeur nominale appropriée avec

une tolérance de ±1 % pour les tensions qui seront utilisées pour la qualification de la

forme d'onde.

La longueur des fils des charges d'évaluation (fil court-circuitant ou résistance) aussi courte

que possible doit être compatible avec une connexion de la charge d'évaluation aux broches

de référence appropriées (A et B à la Figure 1) lors du passage à travers le transducteur de

courant.

4.2.4 Transducteur de courant

Le transducteur de courant doit avoir une largeur de bande minimale de 350 MHz.

60749-27 IEC:2006 – 11 –

3.2

DUT failure

condition in which a DUT does not meet one or more specified parameters as a result of ESD

test

3.3

ESD withstand voltage

maximum applied ESD voltage level that does not cause failure parameter limits to be

exceeded provided that all DUTs stressed at lower levels have also passed

NOTE Clause 3 of this test method is in accordance with IEC 61340-3-2 except for the specific reference to

devices.

4 Equipment

4.1 MM ESD waveform generator

This equipment produces an electrostatic discharge c

...

IEC 60749-27 ®

Edition 2.1 2012-09

CONSOLIDATED VERSION

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 27: Electrostatic discharge (ESD) sensitivity testing – Machine model (MM)

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle de

machine (MM)

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les

microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

Useful links:

IEC publications search - www.iec.ch/searchpub Electropedia - www.electropedia.org

The advanced search enables you to find IEC publications The world's leading online dictionary of electronic and

by a variety of criteria (reference number, text, technical electrical terms containing more than 30 000 terms and

committee,…). definitions in English and French, with equivalent terms in

It also gives information on projects, replaced and additional languages. Also known as the International

withdrawn publications. Electrotechnical Vocabulary (IEV) on-line.

IEC Just Published - webstore.iec.ch/justpublished Customer Service Centre - webstore.iec.ch/csc

Stay up to date on all new IEC publications. Just Published If you wish to give us your feedback on this publication

details all new publications released. Available on-line and or need further assistance, please contact the

also once a month by email. Customer Service Centre: csc@iec.ch.

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

Liens utiles:

Recherche de publications CEI - www.iec.ch/searchpub Electropedia - www.electropedia.org

La recherche avancée vous permet de trouver des Le premier dictionnaire en ligne au monde de termes

publications CEI en utilisant différents critères (numéro de électroniques et électriques. Il contient plus de 30 000

référence, texte, comité d’études,…). termes et définitions en anglais et en français, ainsi que

Elle donne aussi des informations sur les projets et les les termes équivalents dans les langues additionnelles.

publications remplacées ou retirées. Egalement appelé Vocabulaire Electrotechnique

International (VEI) en ligne.

Just Published CEI - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications de la CEI.

Just Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur

Disponible en ligne et aussi une fois par mois par email. cette publication ou si vous avez des questions

contactez-nous: csc@iec.ch.

IEC 60749-27 ®

Edition 2.1 2012-09

CONSOLIDATED VERSION

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Semiconductor devices – Mechanical and climatic test methods –

Part 27: Electrostatic discharge (ESD) sensitivity testing – Machine model (MM)

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques –

Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle

de machine (MM)

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.080.01 ISBN 978-2-8322-0407-8

– 2 – 60749-27 IEC:2006+A1:2012

CONTENTS

FOREWORD . 3

1 Scope . 5

2 Normative references . 5

3 Terms and definitions . 5

4 Equipment . 6

4.1 MM ESD waveform generator . 6

4.2 Waveform verification equipment . 6

5 MM current waveform requirements . 7

5.1 General . 7

5.2 Waveform qualification and verification . 10

5.3 Extra consideration for waveform specifications . 9

6 Device specific evaluation considerations . 10

6.1 Sample size and test conditions . 10

6.2 Worst-case pin or standard qualification board . 10

7 Classification procedure . 11

7.1 Device requirements . 11

7.2 Device selection . 11

7.3 Device characterization . 11

7.4 Device stress levels . 11

7.5 Pin combinations . 12

7.6 Order of test . 12

8 Failure criteria . 12

9 Classification criteria . 12

10 Summary . 13

Figure 1 – MM ESD waveform generator equivalent . 7

Figure 2 – Typical current waveform through a shorting wire . 8

Figure 3 – Typical current waveform through a 500 Ω resistor . 9

Table 1 – Waveform specification . 8

Table 2 – Pin combinations for integrated circuits . 12

60749-27 IEC:2006+A1:2012 – 3 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 27: Electrostatic discharge (ESD) sensitivity testing –

Machine model (MM)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

This consolidated version of the official IEC Standard and its amendment has been prepared

for user convenience.

IEC 60749-27 edition 2.1 contains the second edition (2006) [documents 47/1861/FDIS and

47/1873/RVD] and its amendment 1 (2012) [documents 47/2135/FDIS and 47/2144/RVD].

A vertical line in the margin shows where the base publication has been modified by

amendment 1. Additions and deletions are displayed in red, with deletions being struck

through.

– 4 – 60749-27 IEC:2006+A1:2012

International Standard IEC 60749-27 has been prepared by IEC technical committee 47:

Semiconductor devices.

This second edition cancels and replaces the first edition, published in 2003, and has been

revised in collaboration with technical committee 101. Whilst it does not contain any major

technical changes, reference is now made, where necessary, to IEC 61340-3-2.

A list of all parts of IEC 60749 series, under the general title Semiconductor devices –

Mechanical and climatic test methods can be found on the IEC website.

The committee has decided that the contents of the base publication and its amendments will

remain unchanged until the stability date indicated on the IEC web site under

"http://webstore.iec.ch" in the data related to the specific publication. At this date, the

publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The “colour inside” logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct understanding

of its contents. Users should therefore print this publication using a colour printer.

60749-27 IEC:2006+A1:2012 – 5 –

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 27: Electrostatic discharge (ESD) sensitivity testing –

Machine model (MM)

1 Scope

This part of IEC 60749 establishes a standard procedure for testing and classifying

semiconductor devices according to their susceptibility to damage or degradation by exposure

to a defined machine model (MM) electrostatic discharge (ESD). It may be used as an

alternative test method to the human body model ESD test method. The objective is to

provide reliable, repeatable ESD test results so that accurate classifications can be performed.

This test method is applicable to all semiconductor devices and is classified as destructive.

ESD testing of semiconductor devices is selected from this test method, the human body

model (HBM – see IEC 60749-26) or other test methods in the IEC 60749 series. The MM and

HBM test methods produce similar but not identical results. Unless otherwise specified, the

HBM test method is the one selected.

NOTE 1 This test method does not truly simulate discharge from real machines or metallic tools because the test

method uses high parasitic inductance of the test circuit, whereas real machines and metallic tools, whose

discharge rise time is approximately 100 ps, have no inductance.

NOTE 2 Certain clauses in this test method are in accordance with IEC 61340-3-2.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61340-3-2, Electrostatics – Part 3-2: Methods for simulation of electrostatic effects –

Machine model (MM – Component testing ) electrostatic discharge test waveforms

IEC 60749-26: Semiconductor devices – Mechanical and climatic test methods – Part 26:

Electrostatic discharge (ESD) sensitivity testing – Human body model (HBM)

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

3.1

device under test

DUT

semiconductor product subjected to MM ESD test

3.2

DUT failure

condition in which a DUT does not meet one or more specified parameters as a result of ESD

test

– 6 – 60749-27 IEC:2006+A1:2012

3.3

ESD withstand voltage

maximum applied ESD voltage level that does not cause failure parameter limits to be

exceeded provided that all DUTs stressed at lower levels have also passed

NOTE Clause 3 of this test method is in accordance with IEC 61340-3-2 except for the specific reference to

devices.

3.4

ringing

noise component caused by a large inductance in the discharge circuit

4 Equipment

4.1 MM ESD waveform generator

This equipment produces an electrostatic discharge current pulse simulating a MM ESD event

for application to the DUT. The equivalent waveform generator circuit and tester evaluation

loads are illustrated in Figure 1.

4.2 Waveform verification equipment

4.2.1 General

Equipment capable of verifying the MM current waveform is defined in this standard. This

equipment includes but is not limited to a waveform recording system, a high voltage resistor

and a current transducer.

4.2.2 Waveform recording system

The waveform recording system shall have a minimum single shot bandwidth of 350 MHz.

4.2.3 Evaluation loads

Two evaluation loads are necessary to verify the functionality of the waveform generator:

a) load 1: a shorting wire;

b) load 2: a 500 Ω with a tolerance of ±1 % low inductance resistor appropriate rated for the

voltages that will be used for waveform qualification.

The lead length of the evaluation loads (shorting wire or resistor) shall be as short as possible

consistent with connecting the evaluation load to the appropriate reference terminals (A and B

in Figure 1) while passing through the current transducer.

4.2.4 Current transducer

The current transducer shall have a minimum bandwidth of 350 MHz.

60749-27 IEC:2006+A1:2012 – 7 –

IEC 678/02

Key

1 MM ESD waveform generator (nominally 200 pF)

2 Terminal A

3 Switch

4 Terminal B

5 DUT

6 Evaluation load

7 Shorting wire

8 Resistance R = 500 Ω

9 Current transducer

Figure 1 – MM ESD waveform generator equivalent

Requirements for Figure 1:

1. The evaluation loads (7 and 8) are specified in 4.2.3.

2. The current transducer (9) is specified in 4.2.4.

3. The reversal of terminals A (2) and B (4) to achieve dual polarity is not permitted.

4. The switch (3) is closed 10 ms to 100 ms after the pulse delivery period of each single MM

pulse to ensure that the DUT and any test fixture are not left in a charged state.

NOTE 1 The performance of the waveform generator is strongly influenced by parasitic capacitance and

inductance.

NOTE 2 Precautions must be taken in the design of the waveform generator to avoid recharge transients and

double pulses.

NOTE 3 A resistance in series with the switch would ensure a slow discharge of the DUT.

NOTE 4 Clause 4 of this test method is in accordance with IEC 61340-3-2 except for the specific reference to

devices.

5 MM current waveform requirements

5.1 General

Prior to DUT testing, MM ESD waveform generator qualification shall ensure waveform

integrity of the discharge current through both a shorting wire and a resistive load. The

shorting wire waveform requirements are specified in Figure 2 for all positive and negative

voltages defined in Table 1, while the resistive load waveform requirements for ±400 V are

shown in Figure 3 and Table 1.

– 8 – 60749-27 IEC:2006+A1:2012

Table 1 – Waveform specification

Equivalent I peak current I peak current I current through a

p1 PR 100

Level voltage through a shorting wire

through a 500 Ω resistor 500 Ω resistor at 100 ns

V A (±15 %)

A A (±15 %)

1 100 1,7 – –

2 200 3,5 – –

3 400 7,0 0,29

4 800 14,0 – –

Equivalent I peak current through I peak current I current through a

p1 PR 100

voltage a shorting wire

Level through a 500 Ω resistor 500 Ω resistor at 100 ns

a

V

A (± 15 %) A

A (± 15 %)

1 100 1,7 (1,5) – –

2 200 3,5 (3,0) – –

3 400 7,0 (6,0)

4 800 14,0 (12,0) – –

a

Values in parentheses are the peak current value without ringing.

I

p1

t

pm

t

t

t

t

0 2

I

p2

20 ns per division

IEC 682/02

Figure 2 – Typical current waveform through a shorting wire

60749-27 IEC:2006+A1:2012 – 9 –

Requirements for Figure 2:

The current pulse shall meet the following requirements:

I is the maximum peak current is specified in Table 1;

p1

I is the second peak current shall be between 67 % and 90 % of the absolute value

p2

obtained for I for each level;

p1

t is the period of the major pulse shall be between 63 ns and 91 ns. The measurement

pm

shall be made between the first zero crossing point, t , and the third zero crossing point, t .

1 3

The inductance (L) which is related to t shall be controlled to meet the above specified

pm

pulse period. The recommended value is 750 nH.

I

PR

I

20 ns per division

IEC 683/02

Figure 3 – Typical current waveform through a 500 Ω resistor

Requirements for Figure 3:

The current pulse through a 500 Ω resistor shall meet the following characteristics:

I is the maximum peak current shall be within the range specified in Table 1;

PR

I is the current at 100 ns is defined in Table 1.

5.3 Extra consideration for waveform specifications

The peak current I without ringing shall be verified against the values in Table 1.

p1

– 10 – 60749-27 IEC:2006+A1:2012

5.2 Waveform qualification and verification

Equipment qualification shall be performed during initial acceptance testing. Re-qualification

is required whenever equipment repairs are made that may affect the waveform. Additionally,

the waveforms shall be verified periodically. If a test fixture or circuit board is used to perform

DUT testing, the test fixture (board) shall also be used during equipment qualification tests. In

case the waveform no longer meets the waveform parameters described in Table 1 and

Figures 2 and 3, all ESD testing performed after the previous satisfactory waveform check

shall be considered invalid.

NOTE Clause 5 of this test method is in accordance with IEC 61340-3-2 except for the specific reference to

devices.

6 Device specific evaluation considerations

6.1 Sample size and test conditions

In the semiconductor industry, the typical ESD evaluation uses a sample size of three devices,

each of which is tested using one positive and one negative pulse with a pulse interval of

300 ms.

6.2 Worst-case pin or standard qualification board

6.2.1 General

Equipment qualification shall be made by discharge current measurement with a worst-case

pin combination of DUT board, as specified in 6.2.2. This method shall be used if the

equipment is constructed using a single discharge generator that can be connected to all pins

of the socket on the DUT board by switching of relays.

Multiple discharge generators shall be qualified using the standard qualification board

specified in 6.2.3. This method shall be used if the equipment is constructed to use a large

number of pairs of pins of the DUT board and each test circuit is connected to only a single

pin of the DUT board.

6.2.2 Worst-case pin

The worst-case pin combination for each socket and DUT board shall be identified and

documented. It is recommended that the manufacturers supply the worst-case pin data with

each DUT board. The pin combination with the waveform closest to the limits (see Table 1)

shall be designated for waveform verification.

The worst-case pin combination shall be identified by the following procedure:

a) For each test socket, identify the socket pin with the shortest wiring path from the pulse

generating circuit to the test socket. Connect this pin to terminal B (where it will remain

the reference pin throughout the worst case pin search) and connect one of the remaining

pins to terminal A. Attach a shorting wire between these pins with the current probe

around the shorting wire, as close to terminal B as practicable.

b) Apply a positive 400 V pulse and a negative 400 V pulse and verify that the waveform

meets the requirements defined in Table 1 for both positive and negative pulses.

c) Repeat steps a) and b) until all socket pins have been evaluated.

d) Determine the worst-case pin pair (within the limits and closest to the minimum or

maximum parameter values as specified in Table 1) to be used for future waveform

verification.

60749-27 IEC:2006+A1:2012 – 11 –

e) For initial board check-out, connect a 500 Ω resistor between the worst-case pins

previously identified with the shorting wire in step d). Apply a positive and negative 400 V

pulse and verify that the waveform meets the requirements defined in Table 1.

NOTE If the test socket/test board has already been characterized for worst-case pin on HBM, then that pin

combination is acceptable for use with MM waveform verification. As an alternative to the worst-case pin search,

the reference pin pair may be identified for each test socket of each test fixture. The reference pin combination

should be identified by determining the socket pin with the shortest wiring path from the pulse generating circuit to

the test socket. Connect this pin to terminal B and then connect the socket pin with the longest wiring path from the

pulse generating circuit to the test socket to terminal A (normally provided by the manufacturer). Attach a shorting

wire between these pins with the current probe around the shorting wire. Follow the procedure in step b). For the

initial board check-out connect a 500 Ω resistor between the reference pins. Apply a positive and negative 400 V

pulse and verify that the waveform meets the parameters in Table 1.

6.2.3 Standard qualification board

The standard qualification board shall satisfy the following requirements:

a) the size for the standard qualification board shall be the same size as is used for the DUT

board;

b) the specific length of internal wires of the standard qualification board, between equipment

and the terminals used to connect with evaluation loads, shall be specified in the

applicable specification;

c) the total length of each circuit pair in all DUT boards shall be shorter than/equal to the

length of the internal wire pairs in the standard qualification board and the evaluation load

specified in 4.2.3.

7 Classification procedure

7.1 Device requirements

The devices used for classification testing shall have completed all normal manufacturing

operations.

7.2 Device selection

Prior to ESD testing, d.c. parametric and functional testing at room temperature and, if

applicable, high temperature shall be performed on all devices submitted for ESD testing. The

test devices shall meet device data sheet requirements for these parameters.

7.3 Device characterization

A sample of devices (e.g. three) for each voltage level shall be characterized for the device

ESD failure threshold using the voltage steps shown in Table 1. Finer voltage steps may

optionally be used to obtain a more accurate measure of the failure threshold. ESD testing

should begin at the lowest step in Table 1. The ESD test shall be performed at room

temperature.

7.4 Device stress levels

Each sample of devices (e.g. three) shall be stressed at one voltage level using one positive

and one negative pulse with a minimum of 0,3 s between pulses per pin for all pin

combinations specified in Table 2. It is permitted to use a separate sample of devices (e.g.

three) for each pin combination specified in Table 2. It is permitted to use the same sample

(e.g. three) at the next highest voltage stress level if all devices pass the failure criteria

specified in Clause 8 after ESD exposure to a specified voltage level.

– 12 – 60749-27 IEC:2006+A1:2012

7.5 Pin combinations

The pin combinations to be used are given in Table 2. The actual number of pin combinations

depends on the number of power pin groups. Like-named power pins (V , V , V , V ,

CC1 CC2 SS1 SS2

GND, etc.) that are directly connected by metal (inside the package) may be tied together and

treated as one pin for terminal B connection. Otherwise, each power pin shall be treated as a

separate power pin. Programming pins that do not draw current should be considered as I/O

pins (example: V pins on memory devices). Active discrete devices (FETs, transistors, etc.)

PP

shall be tested using all possible pin-pair combinations (one pin connected to terminal A,

another pin connected to terminal B) regardless of pin name or function. All pins configured

as “no connect” pins shall be verified as “no-connect” and left open (floating) at all times.

Pins labelled “no-connect”, that in fact are connected, shall be tested as non-supply pins.

Table 2 – Pin combinations for integrated circuits

Connect individually to Connect to terminal B Floating pins

Pin combination

terminal A (ground) (unconnected)

a

1 All pins one at a time, First power pin(s) All pins except PUT

except the pin(s) connected and first power pin(s)

to terminal B

2 All pins one at a time, Second power pin(s) All pins except PUT and

except the pin(s) connected second power pin(s)

to terminal B

th

3 All pins one at a time, N power pin(s) All pins except PUT and

th

except the pin(s) connected N power pin(s)

to terminal B

4 Each non-supply pin, one at All other non-supply pins All power pins

a time collectively except PUT

a

PUT: Pin under test.

7.6 Order of test

If a different sample group is ESD tested at each stress level, it is permitted to perform the d.c.

parametric and functional ATE (automatic test equipment) testing after all sample groups

have been ESD tested.

8 Failure criteria

A device will be defined as a failure if, after exposure to ESD pulses, it no longer meets the

device data sheet requirements using parametric and functional testing. If testing is required

at a number of different temperatures, testing shall be performed at the lowest temperature

first.

9 Classification criteria

All samples used shall meet the test requirements of Clause 7 up to a particular voltage level

in order for the device to be classified as meeting a particular withstand classification.

CLASS A: Any device that fails after exposure to an ESD pulse of 200 V or less.

CLASS B: Any device that passes after exposure to an ESD pulse of 200 V, but fails after

exposure to an ESD pulse of 400 V.

CLASS C: Any device that passes after exposure to an ESD pulse of 400 V.

60749-27 IEC:2006+A1:2012 – 13 –

10 Summary

The following details shall be specified in the applicable specification:

a) test method to be selected from human body model or machine model (see Clause 1);

b) frequency of equipment qualification (see 5.2);

c) worst case pin pair and DUT board used for equipment qualification if it is used (see 6.2);

d

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...