ISO 17987-7:2016

(Main)Road vehicles — Local Interconnect Network (LIN) — Part 7: Electrical Physical Layer (EPL) conformance test specification

Road vehicles — Local Interconnect Network (LIN) — Part 7: Electrical Physical Layer (EPL) conformance test specification

ISO 17987-7:2016 specifies the conformance test for the electrical physical layer (EPL) of the LIN communications system. It is part of this document to define a test that considers ISO 9646 and ISO 17987‑4. The purpose of ISO 17987-7:2016 is to provide a standardized way to verify whether a LIN bus driver is compliant to ISO 17987?4. The primary motivation is to ensure a level of interoperability of LIN bus drivers from different sources in a system environment. ISO 17987-7:2016 provides all the necessary technical information to ensure that test results are consistent even on different test systems, provided that the particular test suite and the test system are compliant to the content of this document.

Véhicules routiers — Réseau Internet local (LIN) — Partie 7: Spécification d'essai de conformité de la couche électrique physique (EPL)

General Information

- Status

- Published

- Publication Date

- 13-Dec-2016

- Technical Committee

- ISO/TC 22/SC 31 - Data communication

- Drafting Committee

- ISO/TC 22/SC 31/WG 3 - In-vehicle networks

- Current Stage

- 9599 - Withdrawal of International Standard

- Start Date

- 28-May-2025

- Completion Date

- 12-Feb-2026

Relations

- Consolidated By

ISO 25239-4:2020 - Friction stir welding — Aluminium — Part 4: Specification and qualification of welding procedures - Effective Date

- 06-Jun-2022

- Effective Date

- 06-Jun-2022

Overview

ISO 17987-7:2016 - Road vehicles - Local Interconnect Network (LIN) - Part 7: Electrical Physical Layer (EPL) conformance test specification - defines a standardized test specification to verify conformance of the LIN electrical physical layer. Its purpose is to provide a reproducible way to check whether a LIN bus driver (the Implementation Under Test, IUT) meets the electrical requirements specified in ISO 17987‑4, taking into account test methodology principles from ISO 9646. The standard enables consistent, interoperable LIN bus driver behavior across suppliers and test systems.

Key topics and technical requirements

ISO 17987-7:2016 organizes test cases and measurement requirements for different device classes and voltages. Key technical areas covered include:

- Test scope and organization

- Test case structure for devices with and without RX/TX access

- Separate sections for 12 V and 24 V LIN devices

- Measurement and signal generation requirements

- Calibration and operational conditions to ensure repeatable measurements

- Electrical parameters and static tests

- Operating voltage range checks

- Threshold voltages verification

- Internal resistor measurement (IUT as master/slave)

- Internal capacitance and dynamic interference checks

- Dynamic behavior and timing

- Slope control and edge behavior

- Propagation delay measurement

- Supply voltage offset and failure-mode response

- Failure and robustness tests

- Behaviour under fault conditions and non‑nominal voltages

- Test case identifiers

- Standard includes named test cases (e.g., EPL–CT 1, EPL–CT 22, etc.) covering calibration, static and dynamic verification

The standard specifies the technical information needed so test results are consistent across compliant test suites and test systems.

Practical applications and intended users

ISO 17987-7:2016 is intended for organizations and professionals involved in LIN physical-layer design, testing and validation:

- Automotive OEMs and system integrators verifying LIN node compatibility

- LIN transceiver and ECU hardware designers ensuring EPL compliance

- Supplier test laboratories and certification bodies performing conformance testing

- Tool and test-system vendors implementing LIN EPL test suites

- Validation and quality engineering teams concerned with interoperability and robustness of LIN bus drivers

Using this standard helps reduce integration issues, improve interchangeability of LIN components, and accelerate supplier qualification.

Related standards

- ISO 17987-4 - LIN electrical physical layer normative requirements (referenced as the compliance target)

- ISO 9646 - Conformance test methodology referenced for test definition and procedures

Keywords: ISO 17987-7:2016, LIN, Local Interconnect Network, Electrical Physical Layer, EPL conformance test, LIN bus driver, interoperability, IUT, operating voltage, propagation delay, internal resistor, test specification.

Get Certified

Connect with accredited certification bodies for this standard

TÜV Rheinland

TÜV Rheinland is a leading international provider of technical services.

TÜV SÜD

TÜV SÜD is a trusted partner of choice for safety, security and sustainability solutions.

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

Sponsored listings

Frequently Asked Questions

ISO 17987-7:2016 is a standard published by the International Organization for Standardization (ISO). Its full title is "Road vehicles — Local Interconnect Network (LIN) — Part 7: Electrical Physical Layer (EPL) conformance test specification". This standard covers: ISO 17987-7:2016 specifies the conformance test for the electrical physical layer (EPL) of the LIN communications system. It is part of this document to define a test that considers ISO 9646 and ISO 17987‑4. The purpose of ISO 17987-7:2016 is to provide a standardized way to verify whether a LIN bus driver is compliant to ISO 17987?4. The primary motivation is to ensure a level of interoperability of LIN bus drivers from different sources in a system environment. ISO 17987-7:2016 provides all the necessary technical information to ensure that test results are consistent even on different test systems, provided that the particular test suite and the test system are compliant to the content of this document.

ISO 17987-7:2016 specifies the conformance test for the electrical physical layer (EPL) of the LIN communications system. It is part of this document to define a test that considers ISO 9646 and ISO 17987‑4. The purpose of ISO 17987-7:2016 is to provide a standardized way to verify whether a LIN bus driver is compliant to ISO 17987?4. The primary motivation is to ensure a level of interoperability of LIN bus drivers from different sources in a system environment. ISO 17987-7:2016 provides all the necessary technical information to ensure that test results are consistent even on different test systems, provided that the particular test suite and the test system are compliant to the content of this document.

ISO 17987-7:2016 is classified under the following ICS (International Classification for Standards) categories: 01.040.43 - Road vehicle engineering (Vocabularies); 43.020 - Road vehicles in general; 43.040.15 - Car informatics. On board computer systems. The ICS classification helps identify the subject area and facilitates finding related standards.

ISO 17987-7:2016 has the following relationships with other standards: It is inter standard links to ISO 25239-4:2020, ISO 17987-7:2025. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

ISO 17987-7:2016 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL ISO

STANDARD 17987-7

First edition

2016-12-01

Road vehicles — Local Interconnect

Network (LIN) —

Part 7:

Electrical Physical Layer (EPL)

conformance test specification

Véhicules routiers — Réseau Internet local (LIN) —

Partie 7: Spécification d’essai de conformité de la couche électrique

physique (EPL)

Reference number

©

ISO 2016

© ISO 2016, Published in Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized otherwise in any form

or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior

written permission. Permission can be requested from either ISO at the address below or ISO’s member body in the country of

the requester.

ISO copyright office

Ch. de Blandonnet 8 • CP 401

CH-1214 Vernier, Geneva, Switzerland

Tel. +41 22 749 01 11

Fax +41 22 749 09 47

copyright@iso.org

www.iso.org

ii © ISO 2016 – All rights reserved

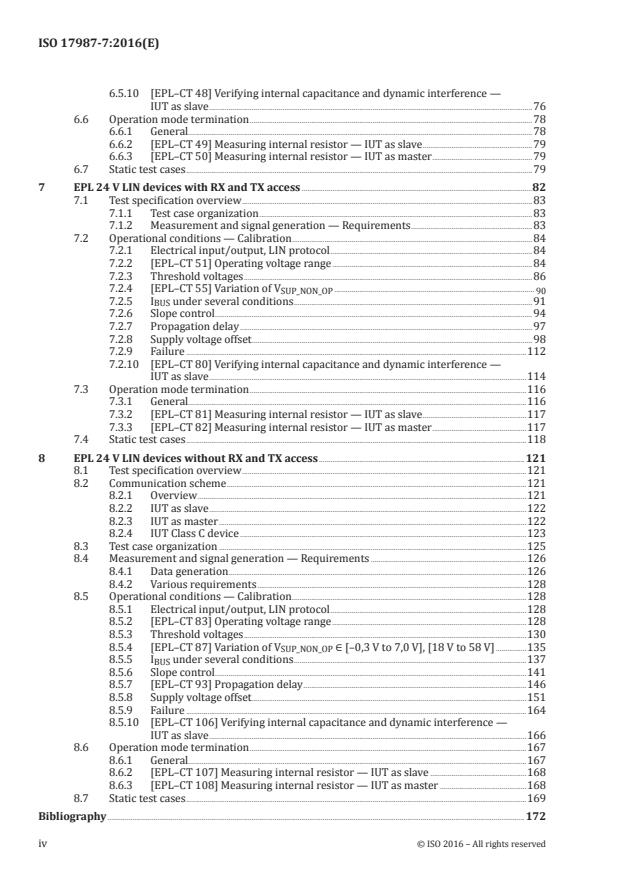

Contents Page

Foreword .v

Introduction .vi

1 Scope . 1

2 Normative references . 1

3 Terms, definitions, symbols and abbreviated terms . 1

3.1 Terms and definitions . 1

3.2 Symbols . 1

3.3 Abbreviated terms . 4

4 Conventions . 5

5 EPL 12 V LIN devices with RX and TX access . 5

5.1 Test specification overview . 5

5.1.1 Test case organization . 5

5.1.2 Measurement and signal generation requirements . 6

5.2 Operational conditions — Calibration . 7

5.2.1 Electrical input/output, LIN protocol . 7

5.2.2 [EPL–CT 1] Operating voltage range . 7

5.2.3 Threshold voltages . 8

5.2.4 [EPL–CT 5] Variation of V . .

SUP_NON_OP 12

5.2.5 I under several conditions .13

BUS

5.2.6 Slope control .16

5.2.7 Propagation delay .19

5.2.8 Supply voltage offset.21

5.2.9 Failure .28

5.2.10 [EPL–CT 22] Verifying internal capacitance and dynamic interference —

IUT as slave .30

5.3 Operation mode termination .32

5.3.1 General.32

5.3.2 [EPL–CT 23] Measuring internal resistor — IUT as slave .33

5.3.3 [EPL–CT 24] Measuring internal resistor — IUT as master .34

5.4 Static test cases .34

6 EPL 12 V LIN devices without RX and TX access .38

6.1 Test specification overview .38

6.2 Communication scheme .38

6.2.1 General.38

6.2.2 IUT as slave .38

6.2.3 IUT as master .39

6.2.4 IUT class C device .40

6.3 Test case organization .42

6.4 Measurement and signal generation — Requirements .43

6.4.1 Data generation . .43

6.4.2 Various requirements .45

6.5 Operational conditions — Calibration .45

6.5.1 Electrical input/output, LIN protocol .45

6.5.2 [EPL–CT 25] Operating voltage range .45

6.5.3 Threshold voltages .47

6.5.4 [EPL–CT 29] Variation of V ∈ [–0,3 V to 7,0 V], [18 V to 40 V] .51

SUP_NON_OP

6.5.5 I under several conditions .52

BUS

6.5.6 Slope control .55

6.5.7 [EPL–CT 35] Propagation delay .59

6.5.8 Supply voltage offset.65

6.5.9 Failure .74

6.5.10 [EPL–CT 48] Verifying internal capacitance and dynamic interference —

IUT as slave .76

6.6 Operation mode termination .78

6.6.1 General.78

6.6.2 [EPL–CT 49] Measuring internal resistor — IUT as slave .79

6.6.3 [EPL–CT 50] Measuring internal resistor — IUT as master .79

6.7 Static test cases .79

7 EPL 24 V LIN devices with RX and TX access .82

7.1 Test specification overview .83

7.1.1 Test case organization .83

7.1.2 Measurement and signal generation — Requirements .83

7.2 Operational conditions — Calibration .84

7.2.1 Electrical input/output, LIN protocol .84

7.2.2 [EPL–CT 51] Operating voltage range .84

7.2.3 Threshold voltages .86

7.2.4 [EPL–CT 55] Variation of V .

SUP_NON_OP 90

7.2.5 I under several conditions .91

BUS

7.2.6 Slope control .94

7.2.7 Propagation delay .97

7.2.8 Supply voltage offset.98

7.2.9 Failure .112

7.2.10 [EPL–CT 80] Verifying internal capacitance and dynamic interference —

IUT as slave .114

7.3 Operation mode termination .116

7.3.1 General.116

7.3.2 [EPL–CT 81] Measuring internal resistor — IUT as slave .117

7.3.3 [EPL–CT 82] Measuring internal resistor — IUT as master .117

7.4 Static test cases .118

8 EPL 24 V LIN devices without RX and TX access .121

8.1 Test specification overview .121

8.2 Communication scheme .121

8.2.1 Overview .121

8.2.2 IUT as slave .122

8.2.3 IUT as master .122

8.2.4 IUT Class C device .123

8.3 Test case organization .125

8.4 Measurement and signal generation — Requirements .126

8.4.1 Data generation . .126

8.4.2 Various requirements .128

8.5 Operational conditions — Calibration .128

8.5.1 Electrical input/output, LIN protocol .128

8.5.2 [EPL–CT 83] Operating voltage range .128

8.5.3 Threshold voltages .130

8.5.4 [EPL–CT 87] Variation of V ∈ [–0,3 V to 7,0 V], [18 V to 58 V] .135

SUP_NON_OP

8.5.5 I under several conditions .137

BUS

8.5.6 Slope control .141

8.5.7 [EPL–CT 93] Propagation delay .146

8.5.8 Supply voltage offset.151

8.5.9 Failure .164

8.5.10 [EPL–CT 106] Verifying internal capacitance and dynamic interference —

IUT as slave .166

8.6 Operation mode termination .167

8.6.1 General.167

8.6.2 [EPL–CT 107] Measuring internal resistor — IUT as slave .168

8.6.3 [EPL–CT 108] Measuring internal resistor — IUT as master .168

8.7 Static test cases .169

Bibliography .172

iv © ISO 2016 – All rights reserved

Foreword

ISO (the International Organization for Standardization) is a worldwide federation of national standards

bodies (ISO member bodies). The work of preparing International Standards is normally carried out

through ISO technical committees. Each member body interested in a subject for which a technical

committee has been established has the right to be represented on that committee. International

organizations, governmental and non-governmental, in liaison with ISO, also take part in the work.

ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of

electrotechnical standardization.

The procedures used to develop this document and those intended for its further maintenance are

described in the ISO/IEC Directives, Part 1. In particular the different approval criteria needed for the

different types of ISO documents should be noted. This document was drafted in accordance with the

editorial rules of the ISO/IEC Directives, Part 2 (see www.iso.org/directives).

Attention is drawn to the possibility that some of the elements of this document may be the subject of

patent rights. ISO shall not be held responsible for identifying any or all such patent rights. Details of

any patent rights identified during the development of the document will be in the Introduction and/or

on the ISO list of patent declarations received (see www.iso.org/patents).

Any trade name used in this document is information given for the convenience of users and does not

constitute an endorsement.

For an explanation on the meaning of ISO specific terms and expressions related to conformity assessment,

as well as information about ISO’s adherence to the World Trade Organization (WTO) principles in the

Technical Barriers to Trade (TBT) see the following URL: www.iso.org/iso/foreword.html.

The committee responsible for this document is ISO/TC 22, Road vehicles, Subcommittee SC 31, Electrical

and electronic equipment.

A list of all parts in the ISO 17987 series can be found on the ISO website.

Introduction

The LIN protocol as proposed is an automotive focused low-speed universal asynchronous receiver

transmitter (UART)-based network. Some of the key characteristics of the Local Interconnect Network

(LIN) protocol are signal-based communication, schedule table-based frame transfer, master/slave

communication with error detection, node configuration and diagnostic service transportation.

The LIN protocol is for low-cost automotive control applications, for example, door module and air

condition systems. It serves as a communication infrastructure for low-speed control applications in

vehicles by providing

— signal-based communication to exchange information between applications in different nodes,

— bitrate support from 1 kbit/s to 20 kbit/s,

— deterministic schedule table-based frame communication,

— network management that wakes up and puts the LIN cluster into sleep mode in a controlled manner,

— status management that provides error handling and error signalling,

— transport layer that allows large amount of data to be transported (such as diagnostic services),

— specification of how to handle diagnostic services,

— electrical physical layer specifications,

— node description language describing properties of slave nodes,

— network description file describing behaviour of communication, and

— application programmer’s interface.

ISO 17987 (all parts) is based on the open systems interconnection (OSI) basic reference model as

specified in ISO/IEC 7498–1 which structures communication systems into seven layers.

The OSI model structures data communication into seven layers called (top down) application layer

(layer 7), presentation layer, session layer, transport layer, network layer, data link layer and physical layer

(layer 1). A subset of these layers is used in ISO 17987 (all parts).

ISO 17987 (all parts) distinguishes between the services provided by a layer to the layer above it and

the protocol used by the layer to send a message between the peer entities of that layer. The reason for

this distinction is to make the services, especially the application layer services and the transport layer

services, reusable also for other types of networks than LIN. In this way, the protocol is hidden from the

service user and it is possible to change the protocol if special system requirements demand it.

ISO 17987 (all parts) provides all documents and references required to support the implementation of

the requirements related to the following:

— ISO 17987–1: This part provides an overview of the ISO 17987 (all parts) and structure along

with the use case definitions and a common set of resources (definitions, references) for use by all

subsequent parts.

— ISO 17987–2: This part specifies the requirements related to the transport protocol and the network

layer requirements to transport the PDU of a message between LIN nodes.

— ISO 17987–3: This part specifies the requirements for implementations of the LIN protocol on the

logical level of abstraction. Hardware related properties are hidden in the defined constraints.

— ISO 17987–4: This part specifies the requirements for implementations of active hardware

components which are necessary to interconnect the protocol implementation.

vi © ISO 2016 – All rights reserved

— ISO/TR 17987–5: This part specifies the LIN application programmers interface (API) and the

node configuration and identification services. The node configuration and identification services

are specified in the API and define how a slave node is configured and how a slave node uses the

identification service.

— ISO 17987–6: This part specifies tests to check the conformance of the LIN protocol implementation

according to ISO 17987–2 and ISO 17987–3. This comprises tests for the data link layer, the network

layer and the transport layer.

— ISO 17987–7: This part specifies tests to check the conformance of the LIN electrical physical layer

implementation (logical level of abstraction) according to ISO 17987–4.

INTERNATIONAL STANDARD ISO 17987-7:2016(E)

Road vehicles — Local Interconnect Network (LIN) —

Part 7:

Electrical Physical Layer (EPL) conformance test

specification

1 Scope

This document specifies the conformance test for the electrical physical layer (EPL) of the LIN

communications system. It is part of this document to define a test that considers ISO 9646 and

ISO 17987–4.

The purpose of this document is to provide a standardized way to verify whether a LIN bus driver is

compliant to ISO 17987–4. The primary motivation is to ensure a level of interoperability of LIN bus

drivers from different sources in a system environment.

This document provides all the necessary technical information to ensure that test results are

consistent even on different test systems, provided that the particular test suite and the test system are

compliant to the content of this document.

2 Normative references

The following documents are referred to in text in such a way that some or all of their content

constitutes requirements of this document. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any amendments) applies.

ISO 17987–4:2016, Road vehicles — Local Interconnect Network (LIN) — Part 4: Electrical Physical Layer

(EPL) specification 12V/24V

3 Terms, definitions, symbols and abbreviated terms

3.1 Terms and definitions

For the purposes of this document, the terms and definitions in ISO 17987–4 and ISO 17987–6 apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

• IEC Electropedia: available at http://www.electropedia.org/

• ISO Online browsing platform: available at http://www.iso.org/obp

NOTE This also includes the device classification of ISO 17987–6:2016, 5.6 into class A/B/C for the different

ECU and transceiver types.

3.2 Symbols

% Percentage

µs Microsecond

C1/2 capacitance

C capacitance in the communication line

COMMON

C` line capacitance

LINE

C total bus capacitance

BUS

C capacitance of master node

MASTER

C reference capacitance

REF

C RXD capacitance (LIN receiver, RXD capacitive load condition)

RXD

C capacitance of slave node

SLAVE

∈ mathematical symbol: replacement for “is an element of”

2 2 2 2

d V/dt second derivative of Voltage (Volt per second )

di/dt instantaneous rate of current change (amps per second)

D1/2 diode

D serial internal diode at transceiver IC

ser_int

D serial master diode

ser_master

F test system bit rate

TS

I current into the ECU bus line

BUS

I current limitation for driver dominant state driver on V = V into ECU bus line

BUS_LIM BUS BAT_max

I current at ECU bus line when V is disconnected

BUS_NO_BAT BAT

I current at ECU bus line when V is disconnected

BUS_NO_GND GND_ECU

I current at ECU bus line when driver off (passive) at dominant LIN-bus-level

BUS_PAS_dom

(12 V LIN devices: V = 0 V and V = 12 V; 24 V LIN devices: V = 0 V and

BUS BAT BUS

V = 24 V)

BAT

I current at ECU bus line when driver off (passive) at recessive LIN-bus-level

BUS_PAS_rec

(12 V LIN devices: 8 V < V < 18 V; 8 V < V < 18 V; V ≥ V ;

BAT BUS BUS BAT

24 V LIN devices: 16 V < V < 36 V; 16 V < V < 36 V; V ≥ V )

BAT BUS BUS BAT

GND GND of ECU

Device

kΩ kilo ohm

kbit/s kilo bit per second

LEN total length of bus line

BUS

LIN LIN network

Bus

ms millisecond

nF nano farad

pF pico farad

pF/m pico farad per meter (line capacitance)

2 © ISO 2016 – All rights reserved

R1/2 resistor

R resistor in the communication line

COMMON

R total bus-resistor including all slave and master resistors

BUS

R = R ||R ||R ||to||R

BUS Master Slave1 Slave2 SlaveN

R reference resistor

REF

R master resistor

master

R pull-up resistor

pull_up

R slave resistor

slave

t byte field synchronization time

BFS

t basic bit times

BIT

t earliest bit sample time

EBS

t propagation delay of receiver

rx_pd

t symmetry of receiver propagation delay rising edge propagation delay of receiver

rx_sym

t latest bit sample time

LBS

t propagation delay time of receiving node 1 at falling (recessive to dominant) LIN bus edge

rx_pdf(1)

t propagation delay time of receiving node 2 at falling (recessive to dominant) LIN bus edge

rx_pdf(2)

t propagation delay time of receiving node 1 at rising (dominant to recessive) LIN bus edge

rx_pdr(1)

t propagation delay time of receiving node 2 at rising (dominant to recessive) LIN bus edge

rx_pdr(2)

t sample window repetition time

SR

TH maximum dominant threshold of receiving node (volt)

Dom(max)

TH minimum dominant threshold of receiving node (volt)

Dom(min)

TH maximum recessive threshold of receiving node (volt)

Rec(max)

TH minimum recessive threshold of receiving node (volt)

Rec(min)

V voltage

V voltage at the anode of the diode

ANODE

V voltage across the ECU supply connectors

BAT

V voltage across the vehicle battery connectors

BATTERY

V battery shift

BS1/2

V voltage on the LIN bus

BUS

V centre point of receiver threshold

BUS_CNT

V receiver dominant voltage

BUS_dom

V receiver recessive voltage

BUS_rec

V voltage at the cathode of the diode

CATHODE

V positive power supply voltage (e.g. 5 V)

CC1/2

V voltage at diode between anode and cathode

D1/2

V dominant voltage

Dom

V ground shift

GND1/2

V battery ground voltage

GND_BATTERY

V voltage on the local ECU ground connector with respect to vehicle battery ground con-

GND_ECU

nector (V )

GND_BATTERY

V receiver hysteresis voltage

HYS

V voltage at IUT supply pins

IUT

V voltage at remote power supply no. 1/no. 2

PS1/2

V recessive voltage

Rec

V voltage drop at the serial diodes

SerDiode

V battery shift

Shift_BAT

V difference between battery shift and GND shift

Shift_Difference

V GND shift

Shift_GND

V voltage at transceiver supply pins

SUP

V voltage which the device is not destroyed; no guarantee of correct operation

SUP_NON_OP

V receiver threshold voltage of the recessive to dominant LIN bus edge

th_dom

V receiver threshold voltage of the dominant to recessive LIN bus edge

th_rec

ΔF/F deviation from nominal bit rate

Nom

τ time constant

Ω ohm

3.3 Abbreviated terms

AC alternate current

API application programmers interface

ASIC application specific integrated circuit

BFS byte field synchronization

DC direct current

EBS earliest bit sample

EMC electromagnetic compatibility

4 © ISO 2016 – All rights reserved

EMI electromagnetic interference

EPL electrical physical layer

ESD electrostatic discharge

GND ground

IUT implementation under test

LBS latest bit sample

Max. maximum

Min. minimum

no. number

OSI open systems interconnection

PDU protocol data unit

RC RC time constant τ (τ = C × R )

BUS BUS

RX RX pin of the transceiver

RXD receive data

SBC system basis chip

SR sample window repetition

TRX transceiver

TX TX pin of the transceiver

TXD transmit data

Typ typical

UART universal asynchronous receiver transmitter

4 Conventions

ISO 17987 (all parts) is based on the conventions specified in the OSI Service Conventions

(ISO/IEC 10731) as they apply for physical layer, data link layer, network and transport protocol and

diagnostic services.

5 EPL 12 V LIN devices with RX and TX access

This clause addresses class A and class B devices.

5.1 Test specification overview

5.1.1 Test case organization

The intention of each test case is described at first, with a short textual explanation. Before tests are

executed, the test system shall be set to its initial state as described in 5.2.

The test procedure and the expected results are described in the form of a chart for each test case.

Table 1 is a typical test description and defines the test case organization.

Table 1 — Test case organization

IUT node as Class A/B/C device as master Corresponding test number TC x, TC y, where x, y are the

or slave or both test case number

Initial state Parameters:

Number of nodes Number of node in the test implementation

Bus loads In order to simulate a LIN network

Operational conditions:

IUT mode Operation mode for the IUT (e.g. normal mode, low power

mode, …).

TX signal State of TX pin at the beginning of the test.

RX signal Logical output voltages of the Rx pin corresponding to

recessive/dominant level at the LIN pin are taken from the

datasheet of the IUT.

V , V , V V , V , Value in volt

BAT SUP IUT, CC PS1/2

V

BUS

Failure In order to set failure at

GND Shift Value in volt

Test steps Describe the test stages.

Response Describe the result expected in order to decide if the test passed or failed.

Reference Corresponding number in ISO 17987–4.

IUT may be a master or slave ECU or an individual transceiver chip. The RX, TX and V signals shall

SUP

be accessible for proper test execution. It is recommended to test with RX/TX access, if not possible,

testing according the specification without RX/TX access (see Clause 6) is accepted. Depending on the

type of IUT, the supply voltage is V for ECU or V for a chip, referred to as V in this description.

BAT SUP IUT

5.1.2 Measurement and signal generation requirements

Table 2 defines the requirements in measurement and signal generation.

Table 2 — Measurement and signal generation requirements

Signal generation: Rise/Fall time <20 ns (square wave)

<40 ns (triangle)

Frequency 20 ppm

Jitter <25 ns

Signal measurement: Dynamic signals: Oscilloscope 100 MHz rise time ≤3,5 ns

Static signals: DC voltage 0,5 %

DC current 0,6 %

Resistance 0,5 %

Power Supply Resolution 10 mV/1 mA

(V , V , V , V , V

BAT SUP IUT CC PS1/2,

Accuracy 0,2 % of value

V )

BUS

6 © ISO 2016 – All rights reserved

5.2 Operational conditions — Calibration

5.2.1 Electrical input/output, LIN protocol

The initial configuration for each test case is defined here. Any requirements for individual tests are

specified with the test case.

Table 3 defines the initial state of electrical input/output.

Table 3 — Initial state of electrical input/output

Parameters:

Number of nodes 1

Bus loads —

Operational conditions:

Initial state IUT mode Set to normal/active mode

TX signal Recessive

V , V , V V , V , V Specified for each test

BAT SUP IUT, CC PS1/2 BUS

Failure No failure

GND shift 0 V

5.2.2 [EPL–CT 1] Operating voltage range

This test shall ensure the correct operation in the valid supply voltage ranges, by correct reception of

dominant bits. The IUT is therefore supplied with an increasing/decreasing voltage ramp.

Figure 1 shows the test configuration of the test system “Operating voltage range with RX and TX

access”.

Figure 1 — Test system: Operating voltage range with RX and TX access

Table 4 defines the test system “Operating voltage range with RX and TX access”.

Table 4 — Test system: Operating voltage range with RX and TX access

IUT node as Class B device as master or slave [EPL–CT 1].1, [EPL–CT 1].2

Class A device

Initial state Operational conditions:

V : [V /V ] Table 5

IUT SUP BAT

Test steps A voltage ramp is set on the V /V as defined in Table 5. The LIN signal is driven with

SUP BAT

a 10 kHz rectangular signal with a duty cycle of 50 % and a voltage swing of 18 V. The IUT

shall be in operational/active mode

Response The RX pin of the IUT shall show the 10 kHz signal. A maximum deviation of 10 % (time,

voltage) is allowed (see Figure 2).

Reference ISO 17987–4:2016, Table 10, Param 9, Param 10

Figure 2 shows the RX response of the test system “Operating voltage range”.

Figure 2 — RX response of test system: Operating voltage range

Table 5 defines the test cases for “Operating voltage ramp”.

Table 5 — Test cases: Operating voltage ramp

EPL–CT–TC V range: [V range/V range] Signal ramp

IUT SUP BAT

[EPL–CT 1].1 [7,0 V to 18 V]/[8,0 V to 18 V] 0,1 V/s

[EPL–CT 1].2 [18 V to 7,0 V]/[18 V to 8,0 V] 0,1 V/s

5.2.3 Threshold voltages

5.2.3.1 General

This group of tests checks whether the receiver threshold voltages of the IUT are implemented correctly

within the entire specified operating supply voltage range. The LIN bus voltage is driven with a voltage

ramp checking the entire dominant and recessive signal area with respect to the applied supply voltage.

In 5.2.3.2 and 5.2.3.3, the signal shall stay continuously on recessive or dominant level depending on

the test case. In 5.2.3.4, the RX output transition is detected. Figure 3 shows the triangle signal on the

LIN bus.

8 © ISO 2016 – All rights reserved

Figure 3 — Triangle signal on the LIN bus

5.2.3.2 [EPL–CT 2] IUT as receiver: V at V (down)

SUP BUS_dom

Figure 4 shows the test configuration of the test system “IUT as receiver V at V (down)”.

SUP BUS_dom

Figure 4 — Test system: IUT as receiver V at V (down)

SUP BUS_dom

Table 6 defines the test system “IUT as receiver V at V (down)”.

SUP BUS_dom

Table 6 — Test system: IUT as receiver V at V (down)

SUP BUS_dom

IUT node as Class A device [EPL–CT 2].1, [EPL–CT 2].2, [EPL–CT 2].3

Initial state Operational conditions:

V : [V ] Table 7

IUT SUP

Test steps A triangle signal with f = 20 Hz and symmetry of 50 % is set on the LIN Bus (see Figure 3).

Response The IUT shall generate a dominant or recessive value on RX as defined on Table 7 during

the falling slope of the triangle signal.

Reference ISO 17987–4:2016, Table 10, Param 17, Param 18

ISO 17987–4:2016, Figure 4

Table 7 defines the test cases for the falling slope of the triangle signal on the LIN bus.

Table 7 — Test cases: Falling slope of the triangle signal on the LIN bus

EPL–CT–TC V : [V ] Signal range Expected RX signal

IUT SUP

[18 V to 4,2 V] Recessive

[EPL–CT 2].1 7 V

[2,8 V to –1,05 V] Dominant

[18 V to 8,4 V] Recessive

[EPL–CT 2].2 14 V

[5,6 V to –2,1 V] Dominant

[20,7 V to 10,8 V] Recessive

[EPL–CT 2].3 18 V

[7,2 V to –2,7 V] Dominant

5.2.3.3 [EPL–CT 3] IUT as receiver: V at V (up)

SUP BUS_rec

Figure 5 shows the test configuration of the test system “IUT as receiver V at V (up)”.

SUP BUS_rec

Figure 5 — Test system: IUT as receiver V at V (up)

SUP BUS_rec

Table 8 defines the test system “IUT as receiver V at V (up)”.

SUP BUS_rec

10 © ISO 2016 – All rights reserved

Table 8 — Test system: IUT as receiver V at V (up)

SUP BUS_rec

IUT node as Class A device [EPL–CT 3].1, [EPL–CT 3].2, [EPL–CT 3].3

Initial state Operational conditions:

V : [V ] Table 9

IUT SUP

Test steps A triangle signal with f = 20 Hz and symmetry of 50 % is set on the LIN Bus (see Figure 3).

Response The IUT shall generate a dominant or recessive value on RX as defined on Table 9 during

the rising slope of the triangle signal.

Reference ISO 17987–4:2016, Table 10, Param 17, Param 18

ISO 17987–4:2016, Figure 4

Table 9 defines the test cases for the rising slope of the triangle signal on the LIN bus.

Table 9 — Test cases: Rising slope of the triangle signal on the LIN bus

EPL–CT–TC V : [V ] Signal range Expected RX signal

IUT SUP

[–1,05 V to 2,8 V] Dominant

[EPL–CT 3].1 7 V

[4,2 V to 18 V] Recessive

[–2,1 V to 5,2 V] Dominant

[EPL–CT 3].2 14 V

[7,8 V to 18 V] Recessive

[–2,7 V to 7,2 V] Dominant

[EPL–CT 3].3 18 V

[10,8 V to 20,7 V] Recessive

5.2.3.4 [EPL–CT 4] IUT as receiver: V at V

SUP BUS

This test shall verify the symmetry of the receiver thresholds. For this purpose a voltage ramp on V

BUS

shows the required threshold values.

Figure 6 shows the test configuration of the test system “IUT as receiver V at V ”.

SUP BUS

Figure 6 — Test system: IUT as receiver V at V

SUP BUS

Table 10 defines the test system “IUT as receiver V at V .

SUP BUS”

Table 10 — Test system: IUT as receiver V at V

SUP BUS

IUT node as Class A device [EPL–CT 4].1, [EPL–CT 4].2, [EPL–CT 4].3

Initial state Operational conditions:

V : [V ] Table 11

IUT SUP

Test steps A triangle signal with f = 20 Hz and symmetry of 50 % is set on the LIN Bus (see Figure 3).

Response The RX output of the IUT shall switch from dominant to recessive when the LIN bus

voltage ramps up and it shall switch from recessive to dominant when the LIN bus voltage

ramps down.

The RX output transition shall meet the following conditions:

— V = (V + V )/2 in the range of (0,475 to 0,525) × V

BUS_CNT th_dom th_rec SUP

— V = V –V shall be less than 0,175 × V

HYS th_rec th_dom SUP

Reference ISO 17987–4:2016, Table 10, Param 19, Param 20

Table 11 defines the test cases for “IUT as receiver V at V ”.

SUP BUS

Table 11 — Test cases: IUT as receiver V at V

SUP BUS

EPL–CT–TC V : [V ] Signal range

IUT SUP

[–1,05 V to 8,05 V] up

[EPL–CT 4].1 7 V

[8,05 V to –1,05 V] down

[–2,1 V to 16,1 V] up

[EPL–CT 4].2 14 V

[16,1 V to –2,1 V] down

[–2,7 V to 20,7 V] up

[EPL–CT 4].3 18 V

[20,7 V to –2,7 V] down

5.2.4 [EPL–CT 5] Variation of V

SUP_NON_OP

Variation of V shall be checked within this test, whether the IUT influences the bus during

SUP_NON_OP

under voltage and over voltage conditions.

Figure 7 shows the test configuration of the test system “Variation of V ”.

SUP_NON_OP

Figure 7 — Test system: Variation of V

SUP_NON_OP

12 © ISO 2016 – All rights reserved

Table 12 defines the test system “Variation of V ”.

SUP_NON_OP

Table 12 — Test system: Variation of V

SUP_NON_OP

IUT node as Class B device as master [EPL–CT 5].1

Class B device as slave [EPL–CT 5].2

Class A device [EPL–CT 5].3

Initial state Operational conditions:

V : [V /V ] V Signal with a 1 V/s ramp in the range see Table 13

IUT SUP BAT IUT

V ; V See Table 13

IUT PS2

Bus load See Table 13

Test steps A voltage ramp (up and down) is set on V . The stimulus stays for t = 30 s at V = 40 V. The

IUT1 IUT1

TX signal shall be left open if an internal pull-up is provided or applied with a recessive level.

Response No dominant state on LIN shall occur.

The IUT shall not be destroyed during the test.

The afterward recessive voltage shall have a maximum deviation of ±5 % from the before

recessive voltage.

Reference ISO 17987–4:2016, Table 10, Param 11

Table 13 defines the test cases “Variation of V ”.

SUP_NON_OP

Table 13 — Test cases: Variation of V

SUP_NON_OP

EP

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...