IEC 61691-5:2004

(Main)Behavioural languages - Part 5: VITAL ASIC (application specific integrated circuit) modeling specification

Behavioural languages - Part 5: VITAL ASIC (application specific integrated circuit) modeling specification

Providse a standard method of modeling ASICs in VHDL.This method is aimed at providing efficient, accurate,and tool independent simulation suitable for large chip-level designs typical of those which are based on ASICs. This publication has the status of a double logo IEEE/IEC standard

General Information

- Status

- Withdrawn

- Publication Date

- 06-Oct-2004

- Withdrawal Date

- 02-Aug-2010

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 2 - TC 91/WG 2

- Current Stage

- WPUB - Publication withdrawn

- Start Date

- 03-Aug-2010

- Completion Date

- 14-Feb-2026

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 61691-5:2004 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Behavioural languages - Part 5: VITAL ASIC (application specific integrated circuit) modeling specification". This standard covers: Providse a standard method of modeling ASICs in VHDL.This method is aimed at providing efficient, accurate,and tool independent simulation suitable for large chip-level designs typical of those which are based on ASICs. This publication has the status of a double logo IEEE/IEC standard

Providse a standard method of modeling ASICs in VHDL.This method is aimed at providing efficient, accurate,and tool independent simulation suitable for large chip-level designs typical of those which are based on ASICs. This publication has the status of a double logo IEEE/IEC standard

IEC 61691-5:2004 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.060 - Languages used in information technology. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61691-5:2004 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL IEC

STANDARD 61691-5

First edition

2004-10

™

IEEE 1076.4

Behavioural languages –

Part 5:

VITAL ASIC (application specific integrated circuit)

modeling specification

Reference number

IEC 61691-5(E):2004

IEEE Std. 1076.4(E):2000

Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the

60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example,

edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the

base publication incorporating amendment 1 and the base publication incorporating

amendments 1 and 2.

Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC,

thus ensuring that the content reflects current technology. Information relating to

this publication, including its validity, is available in the IEC Catalogue of

publications (see below) in addition to new editions, amendments and corrigenda.

Information on the subjects under consideration and work in progress undertaken

by the technical committee which has prepared this publication, as well as the list

of publications issued, is also available from the following:

• IEC Web Site (www.iec.ch)

• Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/searchpub) enables you to

search by a variety of criteria including text searches, technical committees

and date of publication. On-line information is also available on recently issued

publications, withdrawn and replaced publications, as well as corrigenda.

• IEC Just Published

This summary of recently issued publications (www.iec.ch/online_news/ justpub)

is also available by email. Please contact the Customer Service Centre (see

below) for further information.

• Customer Service Centre

If you have any questions regarding this publication or need further assistance,

please contact the Customer Service Centre:

Email: custserv@iec.ch

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

INTERNATIONAL IEC

STANDARD 61691-5

First edition

2004-10

™

IEEE 1076.4

Behavioural languages –

Part 5:

VITAL ASIC (application specific integrated circuit)

modeling specification

Copyright © IEEE 2004 ⎯ All rights reserved

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Inc.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or

mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

The Institute of Electrical and Electronics Engineers, Inc, 3 Park Avenue, New York, NY 10016-5997, USA

Telephone: +1 732 562 3800 Telefax: +1 732 562 1571 E-mail: stds-info@ieee.org Web: www.standards.ieee.org

Commission Electrotechnique Internationale

International Electrotechnical Commission

Международная Электротехническая Комиссия

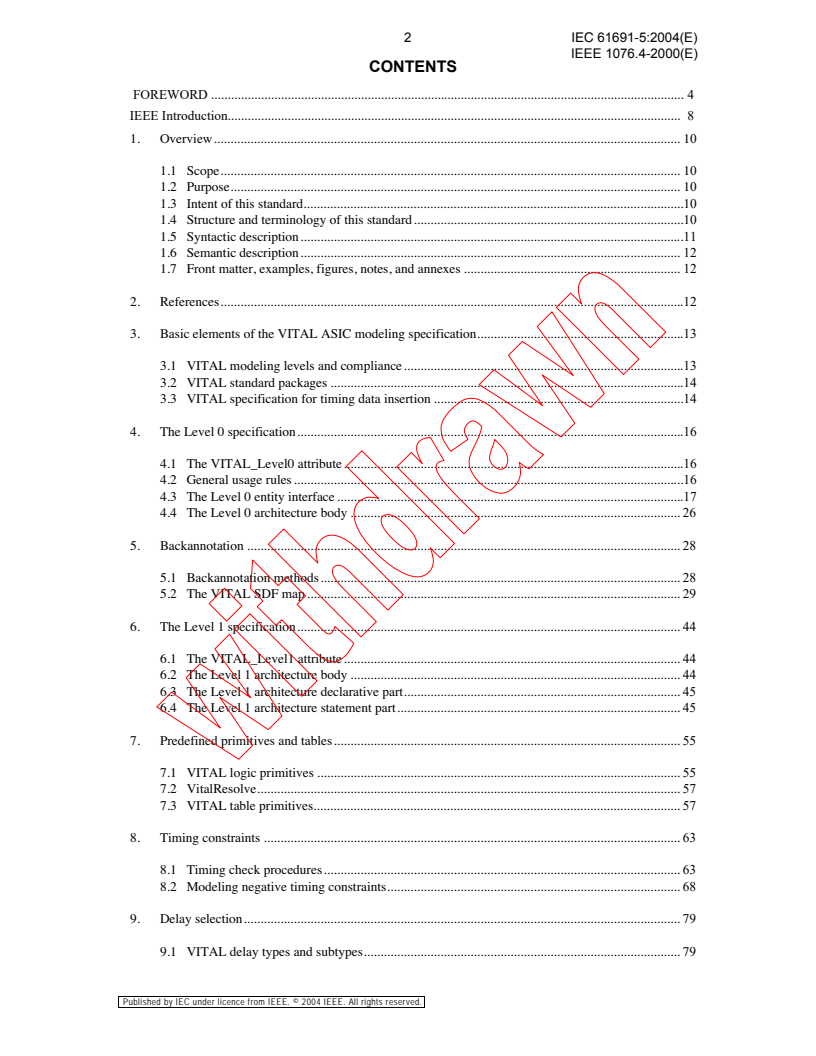

2 IEC 61691-5:2004(E)

IEEE 1076.4-2000(E)

CONTENTS

FOREWORD . 4

IEEE Introduction. 8

1. Overview. 10

1.1 Scope. 10

1.2 Purpose. 10

1.3 Intent of this standard.10

1.4 Structure and terminology of this standard.10

1.5 Syntactic description.11

1.6Semantic description. 12

1.7 Front matter, examples, figures, notes, and annexes . 12

2. References.12

3. Basic elements of the VITAL ASIC modeling specification.13

3.1 VITAL modeling levels and compliance.13

3.2 VITAL standard packages .14

3.3 VITAL specification for timing data insertion .14

4. The Level 0 specification.16

4.1 The VITAL_Level0 attribute.16

4.2 General usage rules.16

4.3 The Level 0 entity interface .17

4.4 The Level 0 architecture body . 26

5. Backannotation . 28

5.1 Backannotation methods. 28

5.2 The VITAL SDF map . 29

6. The Level 1 specification. 44

6.1 The VITAL_Level1 attribute. 44

6.2 The Level 1 architecture body . 44

6.3 The Level 1 architecture declarative part. 45

6.4 The Level 1 architecture statement part. 45

7. Predefined primitives and tables. 55

7.1 VITAL logic primitives . 55

7.2 VitalResolve. 57

7.3 VITAL table primitives. 57

8. Timing constraints . 63

8.1 Timing check procedures. 63

8.2 Modeling negative timing constraints. 68

9. Delay selection. 79

9.1 VITAL delay types and subtypes. 79

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1076.4-2000(E)

9.2 Transition dependent delay selection. 80

9.3 Glitch handling. 80

9.4 Path delay procedures . 81

9.5 Delay selection in VITAL primitives . 83

9.6 VitalExtendToFillDelay. 84

10. The Level 1 Memory specification. 85

10.1 The VITAL Level 1 Memory attribute . 85

10.2 The VITAL Level 1 Memory architecture body. 85

10.3 The VITAL Level 1 Memory architecture declarative part. 86

10.4 The VITAL Level 1 Memory architecture statement part. 86

11. VITAL Memory function specification. 96

11.1 VITAL memory construction . 96

11.2 VITAL memory table specification. 99

11.3 VitalDeclareMemory .108

11.4 VitalMemoryTable. 110

11.5 VitalMemoryCrossPorts . 112

11.6 VitalMemoryViolation. 114

12. VITAL memory timing specification . 117

12.1 VITAL memory timing types . 117

12.2 Memory Output Retain timing behavior. 118

12.3 VITAL Memory output retain timing specification. 119

12.4 Transition dependent delay selection. 119

12.5 VITAL memory path delay procedures . 120

12.6 VITAL memory timing check procedures. 125

13. The VITAL standard packages . 130

13.1 VITAL_Timing package declaration. 130

13.2 VITAL_Timing package body. 145

13.3 VITAL_Primitives package declaration . 172

13.4 VITAL_Primitives package body. 241

13.5 VITAL_Memory package declaration. 311

13.6 VITAL_Memory package body. 332

Annex A (informative) Syntax summary . 421

Annex B (informative) Glossary.427

Annex C (informative) Bibliography.429

Annex D (informative) List of Participants. 430

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

4 IEC 61691-5:2004(E)

IEEE 1076.4-2000(E)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

BEHAVIOURAL LANGUAGES –

Part 5: VITAL ASIC (application specific integrated circuit)

modeling specification

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization

comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to

promote international co-operation on all questions concerning standardization in the electrical and

electronic fields. To this end and in addition to other activities, IEC publishes International Standards,

Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter

referred to as “IEC Publication(s)”). Their preparation is entrusted to technical committees; any IEC National

Committee interested in the subject dealt with may participate in this preparatory work. International,

governmental and non-governmental organizations liaising with the IEC also participate in this preparation.

IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with

conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has

representation from all interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly

indicated in the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC/IEEE 61691-5 has been processed through IEC technical

committee 93: Design automation.

The text of this standard is based on the following documents:

IEEE Std FDIS Report on voting

1076.4 (2000) 93/194/FDIS 93/199/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives.

The committee has decided that the contents of this publication will remain unchanged until

2005.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1076.4-2000(E)

IEC 61691 consists of the following parts, under the general title Behavioural languages:

IEC/IEEE 61691-1-1, Part 1: VHDL language reference manual

IEC 61691-2, Part 2: VHDL multilogic system for model interoperability

IEC 61691-3-1, Part 3-1: Analog description in VHDL (under consideration)

IEC 61691-3-2, Part 3-2: Mathematical operation in VHDL

IEC 61691-3-3, Part 3-3: Synthesis in VHDL

IEC 61691-3-4, Part 3-4: Timing expressions in VHDL (under consideration)

IEC 61691-3-5, Part 3-5: Library utilities in VHDL (under consideration)

IEC/IEEE 61691-4, Part 4: Verilog® hardware description language

IEC/IEEE 61691-5, Part 5: VITAL ASIC (application specific integrated circuit) modeling

specification

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

6 IEC 61691-5:2004(E)

IEEE 1076.4-2000(E)

IEC/IEEE Dual Logo International Standards

This Dual Logo International Standard is the result of an agreement between the IEC and the Institute of

Electrical and Electronics Engineers, Inc. (IEEE). The original IEEE Standard was submitted to the IEC for

consideration under the agreement, and the resulting IEC/IEEE Dual Logo International Standard has been

published in accordance with the ISO/IEC Directives.

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating

Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards

through a consensus development process, approved by the American National Standards Institute, which

brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers

are not necessarily members of the Institute and serve without compensation. While the IEEE administers the

process and establishes rules to promote fairness in the consensus development process, the IEEE does not

independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an IEC/IEEE Dual Logo International Standard is wholly voluntary. The IEC and IEEE disclaim liability for

any personal injury, property or other damage, of any nature whatsoever, whether special, indirect,

consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon

this, or any other IEC or IEEE Standard document.

The IEC and IEEE do not warrant or represent the accuracy or content of the material contained herein, and

expressly disclaim any express or implied warranty, including any implied warranty of merchantability or fitness

for a specific purpose, or that the use of the material contained herein is free from patent infringement.

IEC/IEEE Dual Logo International Standards documents are supplied “AS IS”.

The existence of an IEC/IEEE Dual Logo International Standard does not imply that there are no other ways to

produce, test, measure, purchase, market, or provide other goods and services related to the scope of the

IEC/IEEE Dual Logo International Standard. Furthermore, the viewpoint expressed at the time a standard is

approved and issued is subject to change brought about through developments in the state of the art and

comments received from users of the standard.

Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a

document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents,

although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to

determine that they have the latest edition of any IEEE Standard.

In publishing and making this document available, the IEC and IEEE are not suggesting or rendering

professional or other services for, or on behalf of, any person or entity. Neither the IEC nor IEEE is undertaking

to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other

IEC/IEEE Dual Logo International Standards or IEEE Standards document, should rely upon the advice of a

competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations – Occasionally questions may arise regarding the meaning of portions of standards as they relate

to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will

initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of concerned

interests, it is important to ensure that any interpretation has also received the concurrence of a balance of

interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are

not able to provide an instant response to interpretation requests except in those cases where the matter has

previously received formal consideration.

Comments for revision of IEC/IEEE Dual Logo International Standards are welcome from any interested party,

regardless of membership affiliation with the IEC or IEEE. Suggestions for changes in documents should be in

the form of a proposed change of text, together with appropriate supporting comments. Comments on standards

and requests for interpretations should be addressed to:

Secretary, IEEE-SA Standards Board, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA and/or

General Secretary, IEC, 3, rue de Varembé, PO Box 131, 1211 Geneva 20, Switzerland.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the

Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright

Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center,

Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy

portions of any individual standard for educational classroom use can also be obtained through the Copyright

Clearance Center.

NOTE – Attention is called to the possibility that implementation of this standard may require use of subject

matter covered by patent rights. By publication of this standard, no position is taken with respect to the

existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for

identifying patents for which a license may be required by an IEEE standard or for conducting inquiries into the

legal validity or scope of those patents that are brought to its attention.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1076.4-2000(E)

IEEE Standard for VITAL ASIC

(Application Specific Integrated

Circuit) Modeling Specification

Sponsor

Design Automation Standards Committee

of the

IEEE Computer Society

Approved 21 September 2000

IEEE-SA Standards Board

Abstract: The VITAL (VHDL Initiative Towards ASIC Libraries) ASIC Modeling Specification is

defined in this standard. This modeling specification defines a methodology which promotes the

development of highly accurate, efficient simulation models for ASIC (Application-Specific Integrat-

ed Circuit) components in VHDL.

Keywords: ASIC, computer, computer languages, constraints, delay calculation, HDL, modeling,

SDF, timing, Verilog, VHDL

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

8 IEC 61691-5:2004(E)

IEEE 1076.4-2000(E)

IEEE Introduction

The objectives of the VITAL (VHDL Initiative Towards ASIC Libraries) initiative can be summed up in one

sentence:

Accelerate the development of sign-off quality ASIC macrocell simulation libraries written in VHDL by

leveraging existing methodologies of model development.

The VITAL ASIC modeling specification is a revision of the IEEE 1076.4-1995, IEEE Standard for VITAL

ASIC Modeling Specification. Several new modeling enhancements have been added to the standard and

several usability issues which have been raised with the 1995 standard have been addressed. The new

enhancements and usability improvements addressed include:

— Standardized ASIC memory models

— Support of IEEE VHDL93 and SDF 1497 standards

— Multisource interconnect timing simulation

— SKEW constraint timing checks

— Timing constraint checks feature enhancements

— Additional generics to control ‘X’ generation and message reporting for glitches and timing con-

straints.

— Negative constraint calculation enhancement for vector signals to support memory models

— Fast delay path disable

— Negative glitch preemption

These new features will improve the functional, timing accuracy significantly and aid performance of gate

level VHDL simulations.

The major enhancement is the definition of a ASIC memory modeling standard. With the addition of memory

model package VITAL_Memory, a standard is defined which allow memory models to be coded in VHDL

more efficiently. The standard VITAL memory model package provides a method to represent memories,

procedures and functions to perform various operations and the definition of a modeling style that promotes

consistency, maintainability and tool optimization. This standard does not define modeling behavior of

specific memories. The scope of the memory model standard is currently restricted to ASIC memory

modeling requirement for static RAMs and ROMs. The VITAL memory modeling enhancements are

specified in Clause 10 through Clause 12. The VITAL standard memory package is found in Clause 13.

The memory model standard is derived from contributed work from the LSI Logic VHDL behavioral model

and Mentor Graphics Memory Table Model (MTM) techniques. The generous support of VHDL

International provided the needed funding to take these two contributed works and convert them into the

memory specification and package code by the IEEE 1076.4 TAG (Technical Action Group) with significant

contribution coming from leading EDA services company GDA Technologies.

The technical direction of the working group as well as the day to day activities of issue analysis and drafting

of proposed wordings for the specification are the responsibility of the IEEE 1076.4 TAG. This group consists

of Ekambaram Balaji, Prakash Bare, Nitin Chowdhary, Jose De Castro, Martin Gregory, Rama Kowsalya, B.

Sudheendra Phani Kumar, William Yam, David Lin, Ashwini Mulgaonkar, Ajayharsh P. Varikat, and Steve

Wadsworth and is chaired by Dennis B. Brophy. Without the dedication and hard work of this group it would

not have been possible to complete this work.

The VITAL effort germinated from ideas generated at the VHDL International Users’ Forum held in

Scottsdale, Arizona in May 1992. Further discussions brought people to the conclusion that the biggest

impediment to VHDL design was the lack of ASIC libraries; and that the biggest impediment to ASIC library

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1076.4-2000(E)

development was the lack of a uniform, efficient method for handling timing in VHDL. Since this problem

had already been solved for other languages it was clear that a solution in VHDL was possible and that an

effective way to arrive at this solution was to leverage existing technology. Leveraging existing tools and

environments is viewed as a catalyst for the rapid deployment of ASIC libraries once this initiative is

standardized under the IEEE.

The 1076.4 Working Group has a large membership of over three hundred interested people who have made

significant contributions to this work through their participation in technical meetings, their review of

technical data both in print and through electronic media, and their votes which guided and finally approved

the content of the draft specification. This group is chaired by Victor Berman.

The VITAL ASIC modeling specification is the result of numerous discussions with ASIC vendors, EDA tool

vendors, and ASIC designers to determine the requirements for effective design and fabrication of ASICS

using VHDL. The highest priority issues identified by this group were:

— Timing accuracy

— Model maintainability

— Simulation performance

Some basic guiding principles followed during the entire specification development process were:

— To describe all functionality and timing semantics of the model entirely within the VHDL model and

the associated VITAL packages except for multi-source interconnect.

— To provide a set of modeling rules (Level 1) which constrain the use of VHDL to a point that is ame-

nable for simulator optimizations, and at the same time provide enough flexibility to support most

existing modeling scenarios.

— To have all timing calculations (load dependent or environmentally dependent) performed outside of

the VITAL model. The VITAL model would get these timing values solely as actual values to the

model’s generic parameter list or via SDF direct import.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

10 IEC 61691-5:2004(E)

IEEE 1076.4-2000(E)

BEHAVIOURAL LANGUAGES –

Part 5: VITAL ASIC (application specific integrated circuit)

modeling specification

1. Overview

This clause describes the purpose and organization of this standard.

1.1 Scope

To provide a standard method of modeling ASICs in VHDL. This method is aimed at providing efficient,

accurate, and tool independent simulation suitable for large chip-level designs typical of those which are

based on ASICs.

1.2 Purpose

Current industry methods for designing complex chip-level designs rely on proprietary solutions which are

based on specific commercial tools. This standard provides an effective means of performing those designs

in a standard, non-proprietary manner that is independent of specific tools. This promotes cost effective

design flows and promotes healthy levels of competition in the electronic design industry. This standard

builds on the work of IEEE 1076 VHDL which is a standard hardware description language designed to allow

such tool independent electronic design.

1.3 Intent of this standard

The intent of this standard is to accurately define the Draft Standard VITAL ASIC Modeling Specification.

The primary audiences of this standard are the implementors of tools supporting the specification and ASIC

modelers.

1.4 Structure and terminology of this standard

This standard is organized into clauses, each of which focuses on some particular area of the definition of the

specification. Each page of the formal definition contains ruler-style line numbers in the left margin. Within

each clause, individual constructs or concepts are discussed in each subclause.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE

IEEE 1076.4-2000(E)

Std 1076.4-2000 IEEE STANDARD FOR VITAL ASIC (APPLICATION SPECIFIC

Each subclause describing a specific construct or concept begins with an introductory paragraph. If

applicable, the syntax of the construct is then described using one or more grammatical productions. A set of

paragraphs describing in narrative form the information and rules related to the construct or concept then

follows. Finally, each subclause may end with examples, figures, and notes.

1.5 Syntactic description

The form of a VITAL compliant VHDL description is described by means of a context-free syntax, using a

simple variant of the Backus Naur Form (BNF); in particular:

a) Lower cased words, some containing embedded underlines, are used to denote syntactic categories,

for example:

VITAL_process_statement

Whenever the name of a syntactic category is used, apart from the syntax rules themselves, spaces

take the place of underlines (thus, “VITAL process statement” would appear in the narrative

description when referring to the above syntactic category).

b) Boldface words are used to denote reserved words, for example:

process

Reserved words shall be used only in those places indicated by the syntax.

c) A production consists of a left-hand side, the symbol “::=” (which is read as “can be replaced by”),

and a right-hand side. The left-hand side of a production is always a syntactic category; the right-

hand side is a replacement rule.

The meaning of a production is a textual-replacement rule: any occurrence of the left-hand side may

be replaced by an instance of the right-hand side.

d) A vertical bar separates alternative items on the right-hand side of a production unless it occurs

immediately after an opening brace, in which case it stands for itself.

e) Square brackets enclose optional items on the right-hand side of a production.

f) Braces enclose a repeated item or items on the right-hand side of a production. The items may

appear zero or more times; the repetitions occur from left to right as with an equivalent left-

recursive rule.

g) If the name of any syntactic category starts with an italicized part, it is equivalent to the category

name without the italicized part. The italicized part is intended to convey some semantic

information. For example, unrestricted_variable_name is syntactically equivalent to name alone.

h) The term simple_name is used for any occurrence of an identifier that already denotes some

declared entity.

i) A syntactic category for which no replacement rule is specified is assumed to correspond to the

VHDL syntactic category of the same name. In this case the appropriate replacement rule can be

found in the IEEE Std 1076-1993 VHDL LRM.

j) A syntactic category beginning with the unitalicized prefix “VITAL_” represents a subset of a

VHDL syntactic category.

2 Copyright © 2001 IEEE. All rights reserved.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

12 IEC 61691-5:2004(E)

IEEE

IEEE 1076.4-2000(E)

INTEGRATED CIRCUIT) MODELING SPECIFICATION Std 1076.4-2000

1.6 Semantic description

The meaning of a particular construct or concept and any related restrictions are described with a set of

narrative rules immediately following any syntactic productions in the subclause. In these rules, an italicized

term indicates the definition of that term, and an identifier appearing in Helvetica font refers to a definition

in one of the VHDL or VITAL standard packages or in a VHDL model description. An identifier beginning

with the prefix “VITAL” corresponds to a definition in a VITAL standard package.

Use of the words “is” or “shall” in such a narrative indicates mandatory weight. A non-compliant practice

may be described as erroneous or as an error. These terms are used in these semantic descriptions with the

following meaning:

erroneous: the condition described represents a non-compliant modeling practice; however,

implementations are not required to detect and report this condition. Conditions are deemed

erroneous only when it is either very difficult or impossible in general to detect the condition during

the processing of a model.

error: the condition described represents a non-compliant modeling practice; implementations are

required to detect the condition and report an error to the user of the tool.

1.7 Front matter, examples, figures, notes, and annexes

Prior to this clause are several pieces of introductory material; following the final clause are some annexes

and an index. The front matter, annexes, and index serve to orient and otherwise aid the user of this manual

but are not part of the definition of the Draft Standard VITAL ASIC Modeling Specification.

Some subclauses of this definition contain examples, figures, and notes; with the exception of figures, these

parts always appear at the end of a subclause. Examples are meant to illustrate the possible forms of the

construct described. Figures are meant to illustrate the relationship between various constructs or concepts.

Notes are meant to emphasize consequences of the rules described in the clause or elsewhere. In order to

distinguish notes from the other narrative portions of the definition, notes are set as enumerated paragraphs

in a font smaller than the rest of the text. Examples, figures, and notes are not part of the definition of the

specification.

2. References

This clause lists the standards upon which this standard depends. Bibliographic references may be found in

Annex C. Citations of the form “[C1]” refer to items listed in Annex C, not to items listed in this clause.

IEEE Std 1076-1993, IEEE Standard VHDL Language Reference Manual.

NOTE An updated edition (2002) has been issued.

IEEE Std 1164-1993, IEEE Standard Multivalue Logic System for VHDL Model Interoperability

(Std_logic_1164).

IEEE P1497, Draft Standard Delay Format Specification.

IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway,

NJ 08855-1331, USA (http://standards.ieee.org/).

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE

IEEE 1076.4-2000(E)

Std 1076.4-2000 IEEE STANDARD FOR VITAL ASIC (APPLICATION SPECIFIC

3. Basic elements of the VITAL ASIC modeling specification

This standard defines a modeling style for the purpose of facilitating the development and acceleration of

sign-off quality ASIC macrocell simulation libraries written in VHDL.

The VITAL ASIC modeling specification is an application of the VHSIC Hardware Description Language

(VHDL), described in IEEE Std 1076-1993 [C2] . This document uses the term VHDL to refer to the VHSIC

Hardware Description Language.

This modeling specification relies on the IEEE Standard Multivalue Logic System for VHDL Model

Interoperability (Std_Logic_1164), described in IEEE Std 1164-1993, for its basic logic representation.

Throughout this document, the term standard logic refers to the Std_Logic_1164 package or to an item

declared in the Std_Logic_1164 package.

This modeling specification relies on the IEEE P1497 Draft Standard Delay Format (SDF), as a standard

external timing data representation. Throughout this document, the term SDF refers to this particular version

of the delay format.

The VITAL ASIC modeling specification consists of three basic elements: the formal definition of a VITAL

compliant VHDL model, a set of VHDL packages for providing standard timing support, standard

functionality support, standard memory functional and timing support, and a semantic specification

describing a standard mechanism for insertion of timing data into a VHDL model.

NOTE—VHDL is used to define the VITAL ASIC modeling specification except certain features of multi-source inter-

connect modeling, direct SDF backannotation and negative constraint calculations. The use of the VITAL package code

without specific implementation of these other features does not offer full use of these features.

3.1 VITAL modeling levels and compliance

A VITAL ASIC cell is represented by a VHDL design entity. The VITAL ASIC modeling specification

defines the characteristics of a VITAL design entity in terms of the VHDL descriptions of the entity and

architecture, and in terms of the associated model which is the result of the elaboration of those VHDL

descriptions.

The specification defines three modeling levels; these levels are called VITAL Level 0, VITAL Level 1 and

VITAL Level 1 Memory. Each modeling level is defined by a set of modeling rules. The VITAL Level 0

specification forms a proper subset of the VITAL Level 1 specification and VITAL Level 1 Memory

specification. The modeling rules for a VITAL Level 1 specification and VITAL Level 1 Memory

specification are mutually exclusive.

A model is said to adhere to the rules in a particular specification only if both the model and its VHDL

description satisfy all of the requirements of the specification. Furthermore, if such a model makes use of an

item described in a configuration declaration or a package other than a VHDL or VITAL standard package,

then the external item shall satisfy the requirements of the specification, as though the item appeared in the

VHDL description of the design entity itself.

The VITAL Level 0 specification defines a set of standard modeling rules that facilitate the portability and

interoperability of ASIC models, including the specification of timing information. A model which adheres

to the rules in the Level 0 specification is said to be a VITAL Level 0 model. The Level 0 modeling

specification is described in Clause 4.

The numbers in brackets correspond to those of the bibliography in Annex C.

4 Copyright © 2001 IEEE. All rights reserved.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

14 IEC 61691-5:2004(E)

IEEE

IEEE 1076.4-2000(E)

INTEGRATED CIRCUIT) MODELING SPECIFICATION Std 1076.4-2000

The VITAL Level 1 specification defines a usage model for constructing complete cell models in a manner

that facilitates optimization of the execution of the models. A model which adheres to the rules in both the

Level 0 model interface specification and the Level 1 model architecture specification is said to be a VITAL

Level 1 model. The Level 1 modeling rules are defined in Clause 6.

The VITAL Level 1 Memory specification defines a usage model for constructing complete memory cell

models in a manner that facilitates optimization of the execution of the memory models. A model which

adheres to the rules in both the Level 0 model interface specification and the Level 1 Memory model

architecture specification is said to be a VITAL Level 1 Memory model. The Level 1 Memory modeling rules

are defined in clause 10.

A model that is a VITAL Level 0 model or a VITAL Level 1 model or a VITAL Level 1 Memory model is

said to be VITAL compliant. A VITAL compliant model description contains an attribute specification

representing the highest level of compliance intended by the enclosing entity or architecture. Descriptions of

these attribute specifications may be found in 4.1, 6.1 and 10.1.

NOTES:

1) A Level 1 model or a Level 1 Memory model is by definition a Level 0 model as well (but not vice versa).

2) The rules outlined in the Level 0, Level 1 and Level 1 Memory specifications apply to model descriptions, not to the

VITAL standard packages themselves.

3) AVITAL compliant tool is assumed to enforce the definition of all applicable rules in accordance with the definitions

of the terms IS, SHALL, ERROR, and ERRONEOUS. In addition, a compliant tool is expected to accept and correctly

execute a VITAL compliant model, and to identify and reject models which are not compliant. A VITAL compliant tool

is also expected to fully support the processes described in the specification, including SDF backannotation and negative

time sequential constraint transformation.

3.2 VITAL standard packages

The Draft Standard VITAL ASIC Modeling Specificatio

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...