IEC 61988-3-2:2009

(Main)Plasma display panels - Part 3-2: Interface - Electrical interface

Plasma display panels - Part 3-2: Interface - Electrical interface

IEC 61988-3-2:2009 defines the electrical interface of digital video data signals, synchronization signals and functional signals between the image processing board of the PDP set and the control board of the PDP module, and defines the description of the pin assignment of the connectors.

Panneaux d'affichage à plasma - Partie 3-2: Interface - Interface électrique

La CEI 61988-3-2:2009 définit l'interface électrique des signaux de données vidéo numériques, des signaux de synchronisation et des signaux fonctionnels entre la carte de traitement d'image de l'ensemble PDP (plasma display panel) et la carte de commande du module PDP, et elle définit l'affectation des broches des connecteurs.

General Information

- Status

- Published

- Publication Date

- 05-Aug-2009

- Technical Committee

- TC 110 - Electronic displays

- Drafting Committee

- WG 4 - TC 110/WG 4

- Current Stage

- PPUB - Publication issued

- Start Date

- 06-Aug-2009

- Completion Date

- 31-Aug-2009

Overview

IEC 61988-3-2:2009 is an international standard developed by the International Electrotechnical Commission (IEC) that specifies the electrical interface requirements for plasma display panels (PDPs). This standard defines how digital video data signals, synchronization signals, and functional signals are transferred between the image processing board of a PDP set and the control board of a PDP module. Additionally, it provides guidance on the description of pin assignment for connectors utilized in these interfaces.

IEC 61988-3-2:2009 is essential for manufacturers, designers, and integrators working in the flat panel display industry, ensuring compatibility, safety, and consistent performance across plasma display panel equipment.

Key Topics

- Electrical Interface Definition: The standard outlines the electrical interface for digital video, synchronization, and control signals between PDP components.

- Digital Signal Interface Types: Includes the use of LVDS (Low Voltage Differential Signaling), TTL (Transistor-Transistor Logic), and TMDS (Transition Minimized Differential Signaling) as the main digital interface types.

- Pin Assignment Guidance: Provides example tables and formats for clear pin assignment of connectors between image processing boards and PDP modules.

- Input Signal Specification: Details about input signal types, including display data, synchronization (horizontal/vertical sync), data enable (DE), data clock (DCLK), and function control signals.

- Power Sequencing: Guidance on power supply sequence requirements to prevent hardware damage and ensure reliable operation.

- Timing Specifications: Describes signal timing requirements and provides timing diagrams to illustrate valid data periods and synchronization.

- Connector Examples: Sample pin assignments and connector layouts for different signaling standards (LVDS, TTL, TMDS).

Applications

Implementing IEC 61988-3-2:2009 brings numerous advantages to organizations in the plasma display field.

- Product Design and Development: Enables engineers to design PDP image processing and control boards that are universally compatible with industry-standard interfaces and connectors.

- Supply Chain Integration: Facilitates communication and integration between components from different suppliers by ensuring uniform electrical interface definitions.

- Quality Assurance: Supports robust testing and validation by providing standardized reference input signals and timing, reducing the risk of interface failures during operation.

- Interoperability: Increases product interoperability and interchangeability between PDP modules and control electronics, which is valuable for both OEM manufacturers and system integrators.

- Documentation and Support: Helps with accurate technical documentation, particularly regarding pin assignments, signal functions, and power requirements for installation and maintenance.

Related Standards

IEC 61988-3-2:2009 functions within a comprehensive set of standards that collectively address different facets of plasma display panel technology:

- IEC 61988-1: Plasma display panels – Part 1: Terminology and letter symbols

- IEC 61988-2-1: Plasma display panels – Part 2-1: Measuring methods – Optical

- IEC 61988-2-2: Plasma display panels – Part 2-2: Measuring methods – Optoelectrical

- TIA/EIA-644A: Electrical characteristics of LVDS interface circuits

- JEIDA-59-1999: Digital interface standards for monitors

Additional references may include standards on environmental testing (IEC 60068-1) and television broadcast measurement (IEC 60107-1).

Keywords: IEC 61988-3-2:2009, plasma display panel, PDP, electrical interface, LVDS, TTL, TMDS, digital video signal, interface pin assignment, synchronization signals, power sequencing, flat panel display standard, international standard, connector specification.

Frequently Asked Questions

IEC 61988-3-2:2009 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Plasma display panels - Part 3-2: Interface - Electrical interface". This standard covers: IEC 61988-3-2:2009 defines the electrical interface of digital video data signals, synchronization signals and functional signals between the image processing board of the PDP set and the control board of the PDP module, and defines the description of the pin assignment of the connectors.

IEC 61988-3-2:2009 defines the electrical interface of digital video data signals, synchronization signals and functional signals between the image processing board of the PDP set and the control board of the PDP module, and defines the description of the pin assignment of the connectors.

IEC 61988-3-2:2009 is classified under the following ICS (International Classification for Standards) categories: 31.260 - Optoelectronics. Laser equipment. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61988-3-2:2009 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 61988-3-2 ®

Edition 1.0 2009-08

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Plasma display panels –

Part 3-2: Interface – Electrical interface

Panneaux d’affichage à plasma –

Partie 3-2: Interface – Interface électrique

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by

any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or

IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

ƒ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

ƒ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

ƒ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

ƒ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

ƒ Catalogue des publications de la CEI: www.iec.ch/searchpub/cur_fut-f.htm

Le Catalogue en-ligne de la CEI vous permet d’effectuer des recherches en utilisant différents critères (numéro de référence,

texte, comité d’études,…). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

ƒ Just Published CEI: www.iec.ch/online_news/justpub

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles

publications parues. Disponible en-ligne et aussi par email.

ƒ Electropedia: www.electropedia.org

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et

définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé

Vocabulaire Electrotechnique International en ligne.

ƒ Service Clients: www.iec.ch/webstore/custserv/custserv_entry-f.htm

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du

Service clients ou contactez-nous:

Email: csc@iec.ch

Tél.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 61988-3-2 ®

Edition 1.0 2009-08

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Plasma display panels –

Part 3-2: Interface – Electrical interface

Panneaux d’affichage à plasma –

Partie 3-2: Interface – Interface électrique

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

PRICE CODE

INTERNATIONALE

T

CODE PRIX

ICS 31.260 ISBN 978-2-88910-599-1

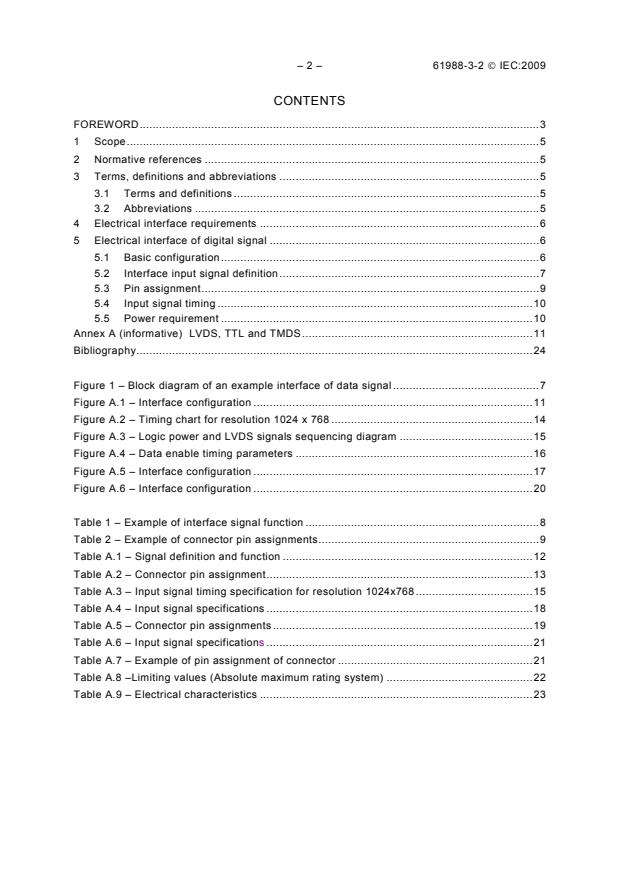

– 2 – 61988-3-2 © IEC:2009

CONTENTS

FOREWORD.3

1 Scope.5

2 Normative references .5

3 Terms, definitions and abbreviations .5

3.1 Terms and definitions .5

3.2 Abbreviations .5

4 Electrical interface requirements .6

5 Electrical interface of digital signal .6

5.1 Basic configuration.6

5.2 Interface input signal definition.7

5.3 Pin assignment.9

5.4 Input signal timing .10

5.5 Power requirement .10

Annex A (informative) LVDS, TTL and TMDS.11

Bibliography.24

Figure 1 – Block diagram of an example interface of data signal .7

Figure A.1 – Interface configuration .11

Figure A.2 – Timing chart for resolution 1024 x 768 .14

Figure A.3 – Logic power and LVDS signals sequencing diagram .15

Figure A.4 – Data enable timing parameters .16

Figure A.5 – Interface configuration .17

Figure A.6 – Interface configuration .20

Table 1 – Example of interface signal function .8

Table 2 – Example of connector pin assignments.9

Table A.1 – Signal definition and function .12

Table A.2 – Connector pin assignment.13

Table A.3 – Input signal timing specification for resolution 1024x768 .15

Table A.4 – Input signal specifications .18

Table A.5 – Connector pin assignments .19

Table A.6 – Input signal specifications .21

Table A.7 – Example of pin assignment of connector .21

Table A.8 –Limiting values (Absolute maximum rating system) .22

Table A.9 – Electrical characteristics .23

61988-3-2 © IEC:2009 – 3 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

PLASMA DISPLAY PANELS –

Part 3-2: Interface –

Electrical interface

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61988-3-2 has been prepared by IEC technical committee 110:

Flat panel display devices.

The text of this standard is based on the following documents:

FDIS Report on voting

110/181/FDIS 110/190/RVD

Full information on the voting for the approval on this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all the parts in the IEC 61988 series, under the general title Plasma display panels,

can be found on the IEC website.

– 4 – 61988-3-2 © IEC:2009

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

61988-3-2 © IEC:2009 – 5 –

PLASMA DISPLAY PANELS –

Part 3-2: Interface –

Electrical interface

1 Scope

This part of IEC 61988 defines the electrical interface of digital video data signals,

synchronization signals and functional signals between the image processing board of the

PDP set and the control board of the PDP module, and defines the description of the pin

assignment of the connectors.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61988-1, Plasma display panels – Part 1: Terminology and letter symbols

IEC 61988-2-1, Plasma display panels – Part 2-1: Measuring methods – Optical

IEC 61988-2-2, Plasma display panels – Part 2-2: Measuring methods – Optoelectrical

TIA/EIA-644A, Electrical characteristics of low voltage differential signaling (LVDS) interface

circuits

JEIDA-59-1999, Digital interface standards for monitor (only available in English)

3 Terms, definitions and abbreviations

3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 61988-1,

IEC 60068-1 and IEC 60107-1 as well as the following apply.

3.1.1

image processing board

circuit board including A/D converter, scaler and video decoder, deinterlacing for image signal

from input device such as TV-tuner, PC, DVD, etc.

3.2 Abbreviations

NOTE The following are acronyms for reference.

TTL Transistor-transistor logic

LVDS Low voltage differential signalling

TMDS Transition minimized differential signalling

HS Horizontal synchronization

VS Vertical synchronization

DE Data enable

DCLK Data clock

APC Auto power control

– 6 – 61988-3-2 © IEC:2009

4 Electrical interface requirements

The electrical interface of PDP module is a power sequence and a digital interface of PDP

module.

The power sequence of PDP module is power on- and off-sequence of all power supplies in

and to PDP module. The power on- and off-sequence of PDP module shall be fully described

in each relevant specification.

The digital signal interface is either an LVDS, a TTL or a TMDS interface, whose signal

encodes the digital video data and function control signals.

Function control signal, which is the additional signal, except digital video signal, to control

the functions such as APC, shall be fully described in each detail specification.

The interface configuration, input signal definition, pin assignment, input signal timing and

power requirement shall be described in each detail specification.

5 Electrical interface of digital signal

5.1 Basic configuration

The basic configuration of electrical interface of digital signal is shown in Figure 1 as one of

examples. Examples of LVDS, TTL and TMDS are explained in Annex A.

61988-3-2 © IEC:2009 – 7 –

Image processing board PDP module

Electrical interface signal

(Display data signal and control signal)

R – R R – R

0 n–1 0 n–1

G – G G – G

0 n–1 0 n–1

B – B B – B

0 n–1 0 n–1

LVDS

TTL

VS

VS

TMDS

HS

HS

DE

DE

DCLK

DCLK

Function control signals Function control signals

IEC 1348/09

NOTE 1 The image processing board includes A/D converter, scaler and video decoder for image signal from

input device such as TV-tuner, PC, DVD, etc.

NOTE 2 Ri, Gi and Bi: ith bit data for n-bit digital video signal of red, green and blue, respectively (i=0 to n-1).

Figure 1 – Block diagram of an example interface of data signal

5.2 Interface input signal definition

The example of interface signal definition and function is as follows in Table 1.

– 8 – 61988-3-2 © IEC:2009

Table 1 – Example of interface signal function

Symbol I/O Function Description

Rx IN0+

I LVDS differential data (+)

(or RA+) Display data signal:

R , R , R , R , R , R , G

Rx IN0 - 0 1 2 3 4 5 0

I LVDS differential data (-)

(or RA-)

Rx IN1+

I LVDS differential data (+)

Display data signal:

(or RB+)

G , G , G , G , G , B , B

Rx IN1 -

1 2 3 4 5 0 1

I LVDS differential data (-)

(or RB-)

Rx IN2+

I Display data signal: LVDS differential data (+)

(or RC+)

B , B , B , B , HS,

2 3 4 5

Rx IN2 -

I VS, DE LVDS differential data (-)

(or RC-)

Rx IN3+

I LVDS differential data (+)

Display data signal and control signal:

(or RD+)

R , R , G , G , B , B , RES

Rx IN3 - 6 7 6 7 6 7

I LVDS differential data (-)

(or RD-)

Rx IN4+

I LVDS differential data (+)

Display data signal and control signal:

(or RE+)

B , B , G , G , R , R , RES

Rx IN4-

8 9 8 9 8 9

I LVDS differential data (-)

(or RE-)

Rx CLKIN+

I LVDS differential clock (+)

(or CLK+)

Data clock signal:

DCLK

Rx CLKIN-

I LVDS differential clock (-)

(or CLK-)

NOTE This example shows the case of LVDS with 10-bit video signal.

61988-3-2 © IEC:2009 – 9 –

5.3 Pin assignment

The pin assignments should be given in the form of Table 2.

Table 2 – Example of connector pin assignments

Pin no Pin name

1 GND

2 GND

3 Rx IN0-

4 Rx IN0+

5 GND

6 GND

7 Rx IN1-

8 Rx IN1+

9 GND

10 GND

11 Rx IN2-

12 Rx IN2+

13 GND

14 GND

15 Rx CLKIN-

16 Rx CLKIN+

17 GND

18 GND

19 Rx IN3-

20 Rx IN3+

21 GND

22 GND

23 GND

24 GND

25 RX IN4-

26 RX IN4+

27 GND

28 GND

29 GND

30 GND

31 GND

– 10 – 61988-3-2 © IEC:2009

5.4 Input signal timing

Timing of the interface signals of the PDP module shall be fully described. An example is

given in A.1.

5.5 Power requirement

Power requirements, and power on sequence when needed, shall be fully described. An

example is given in A.1.1.

61988-3-2 © IEC:2009 – 11 –

Annex A

(informative)

LVDS, TTL and TMDS

A.1 Video

A.1.1 LVDS

A.1.1.1 Basic configuration

Figure A.1 shows an example of interface configuration of LVDS.

PDP module

Image processing board

Tx/Rx0+

R – R

Tx/Rx0–

0 n–1

R – R

0 n–1

Tx/Rx1+

G – G

0 n–1

G – G

0 n–1

Tx/Rx1–

B – B

Tx/Rx2+

0 n–1

B – B

0 n–1

LVDS LVDS

receiver

transmitter

Tx/Rx2–

VS

(Serial / Parallel)

(Parallel / Serial)

VS

Tx/Rx3+

HS

HS

Tx/Rx3–

DE

DE

Tx/Rx4+

DCLK

Tx/Rx4– DCLK

CLK+

CLK–

m bits

Function control signals

Function control signals

IEC 1349/09

Figure A.1 – Interface configuration

– 12 – 61988-3-2 © IEC:2009

A.1.1.2 Interface input signal specification

The input signal (display data signal and control signal) is converted from parallel data to

serial data with the LVDS transmitter and further converted into six sets of differential signals

before input to the PDP module. The LVDS signal definition and function is as follows in

Table A.1.

Table A.1 – Signal definition and function

Symbol I/O Function Description

Rx IN0+ (or RA+) I LVDS differential data (+)

Display data signal:

R , R , R , R , R , R , G

0 1 2 3 4 5 0

Rx IN0- (or RA-) I LVDS differential data (-)

Rx IN1+ (or RB+) I LVDS differential data (+)

Display data signal:

G , G , G , G , G , B , B

1 2 3 4 5 0 1

Rx IN1- (or RB-) I LVDS differential data (-)

Rx IN2+ (or RC+) I LVDS differential data (+)

Display data signal:

B , B , B , B , HS, VS, DE

2 3 4 5

Rx IN2- (or RC-) I LVDS differential data (-)

Rx IN3+ (or RD+) I LVDS differential data (+)

Display data signal and control signal:

R , R , G , G , B , B , RES

6 7 6 7 6 7

Rx IN3- (or RD-) I LVDS differential data (-)

Rx IN4+ (or RE+) I LVDS differential data (+)

Display data signal and control signal:

B , B , G , G , R , R , RES

8 9 8 9 8 9

Rx IN4- (or RE-) I LVDS differential data (-)

Rx CLKIN+

I LVDS differential clock (+)

(or DCLK+)

Data clock signal: DCLK

Rx CLKIN-

I LVDS differential clock (-)

(or DCLK-)

61988-3-2 © IEC:2009 – 13 –

A.1.1.3 Pin assignment

The pin names may be given in the form of Table A.2.

Table A.2 – Connector pin assignment

Pin no Pin name

1 GND

2 GND

3 Rx IN0-

4 Rx IN0+

5 GND

6 GND

7 Rx IN1-

8 Rx IN1+

9 GND

10 GND

11 Rx IN2-

12 Rx IN2+

13 GND

14 GND

15 Rx CLKIN-

16 Rx CLKIN+

17 GND

18 GND

19 Rx IN3-

20 Rx IN3+

21 GND

22 GND

23 GND

24 GND

25 RX IN4-

26 RX IN4+

27 GND

28 GND

29 GND

30 GND

31 GND

– 14 – 61988-3-2 © IEC:2009

A.1.1.4 Input signal timing chart

Figure A.2 is an example of input signal timing chart.

t

vsync

VS

t

vw

t

vbp

t

vfp

HS

1 2 3 - - 767 768 1 2 3 - - 767 768 1 2 3 - - -

Line number 768

t

hsync

HS

t

hw

t t

hbp

dclk t

hfp

DCLK

1 2 3 4 1 024

DE

(Period of valid data)

Data D1 D2 D3 D1 024

Shaded area

: Invalid data

IEC 1350/09

Figure A.2 – Timing chart for resolution 1 024 x 768

61988-3-2 © IEC:2009 – 15 –

A.1.1.5 Input signal timing specification

Table A.3 is an example of input signal timing specification.

Table A.3 – Input signal timing specification for resolution 1024 x 768

No Symbol Typical value Unit Remark

t

1 16,667 ms 60 Hz, 806 lines

vsync

t

2 0,12 ms 6 lines

vw

t

3 0,60 ms 29 lines

vbp

t

4 0,06 ms 3 lines

vfp

t

5 20,667 μs 1 344 dots

hsync

t

6 2,09 136 dots

μs

hw

t

7 2,46 μs 160 dots

hbp

t

8 0,36 μs 24 dots

hfp

t

9 15,385 ns 64,999 MHz

dclk

A.1.1.6 Power sequencing requirements

The LVDS interface requires the logic power and data/control signal sequencing and the data

enable timing of Figure A.3 and Figure A.4.

t

0,9 VDD 0,9 VDD

Power

0,1 VDD 0,1 VDD

Supply 0 V

t t

2 3

VDD t

Valid data

LVDS

interface

0,5 ms ≤ t ≤ 10 ms 0 ≤ t ≤ 50 ms 0 ≤ t ≤ 50 ms 500 ms ≤ t

1 2 3 4

IEC 1351/09

Figure A.3 – Logic power and LVDS signals sequencing diagram

– 16 – 61988-3-2 © IEC:2009

t

hsync

HS

t

hw

t t

hfp

hbp

DE

t

ha (horizontal active)

t

vsync

VS

t

vw

t t

vbp vfp

DE

t

va (vertical active)

DE-only timing mode

t or t t t or t

deb ha va

ha va

DE

IEC 1352/09

Figure A.4 – Data enable timing parameters

61988-3-2 © IEC:2009 – 17 –

A.1.2 TTL

A.1.2.1 Basic configuration

Figure A.5 shows an example of interface configuration of TTL.

Image processing board PDP module

R ∼ R R ∼ R

0 n–1 0 n–1

n bits

G ∼ G n bits G ∼ G

0 n–1 0 n–1

n bits

B ∼ B B ∼ B

0 n–1 0 n–1

VS VS

HS HS

DE DE

DCLK DCLK

m bits

Function control signals Function control signals

IEC 1353/09

Figure A.5 – Interface configuration

– 18 – 61988-3-2 © IEC:2009

A.1.2.2 Interface input signal specification

Table A.4 is an example of input signal specification.

Table A.4 – Input signal specifications

Symbol Function Remarks

Display data signal:

R ~ R

n bits red video signal

0 n-1

R : MSB*, R : LSB**

n-1 0

Display data signal:

G ~ G

n bits green video signal

0 n-1

G : MSB*, G : LSB**

n-1 0

Display data signal:

B ~ B

n bits blue video signal

0 n-1

B : MSB*, B : LSB**

n-1 0

This signal specifies the data period for

one horizontal line. Control of the next

HS Horizontal synchronous signal

line begins at the rising edge of

HS

Timing signal that controls the start of

VS Vertical synchronous signal

the screen. Control of the next screen

begins at the rising edge of VS

When DE signal is high, data is valid

DE Data enable

When DE signal is low, data is invalid

DCLK Clock for video signal Latch the video signal at falling edge

* MSB: Most significant bit (the highest intensity bit)

** LSB: Least significant bit (the lowest intensity bit)

61988-3-2 © IEC:2009 – 19 –

A.1.2.3 Pin assignment

Table A.5 shows an example of the pin assignments of TTL.

Table A.5 – Connector pin assignments

Pin

Pin no. Pin name Pin no. Pin name Pin no.

name

1 GND 24 B2 47 GND

2 NC 25 GND 48 G5

3 GND 26 B3 49 GND

4 NC 27 GND 50 G6

5 GND 28 B4 51 GND

6 NC 29 GND 52 G7

7 GND 30 B5 53 GND

8 NC 31 GND 54 R0

9 GND 32 B6 55 GND

10 NC 33 GND 56 R1

11 GND 34 B7 57 GND

12 DCLK 35 GND 58 R2

13 GND 36 NC 59 GND

14 DE 37 GND 60 R3

15 CTRL1 38 G0 61 GND

16 DHS 39 GND 62 R4

17 CTRL2 40 G1 63 GND

18 DVS 41 GND 64 R5

19 RESET 42 G2 65 GND

20 B0 43 GND 66 R6

21 GND 44 G3 67 GND

22 B1 45 GND 68 R7

23 GND 46 G4

A.1.2.4 Input signal timing chart

Description of input signal timing chart is basically same as that of LVDS. (See Figure A.2.)

A.1.2.5 Input signal timing specification

Description of input signal timing specification is basically same as that of LVDS. (See Table

A.3.)

– 20 – 61988-3-2 © IEC:2009

A.1.3 TMDS

A.1.3.1 Basic configuration

Figure A.6 shows an example of interface configuration of TMDS.

Image processing board PDP module

TX2 (Red)

R – R

0 n–1 R – R

0 n–1

TX1 (Green)

G – G

G – G

0 n–1

0 n–1

TMDS

TMDS

B – B

B – B

0 n–1

transmitter 0 n–1

receiver

TX0 (Blue)

(Parallel / Serial)

VS

(Serial / Parallel)

VS

HS

HS

DCLK

DE

DE

DCLK

DCLK

m bits

Function control signals Function control signals

IEC 1354/09

Figure A.6 – Interface configuration

61988-3-2 © IEC:2009 – 21 –

A.1.3.2 Interface input signal specification

Table A.6 is an example of input signal specification.

Table A.6 – Input signal specifications

Symbol I/O Function Description

TX0+ I Display data signal: TMDS differential data (+)

B , B , B , B , B , B , B , B , HS, VS

TX0- I 0 1 2 3 4 5 6 7 TMDS differential data (-)

Display data signal:

TX1+ I TMDS differential data (+)

G ,G , G , G , G , G ,G , G , PLL SYNC

TX1- I TMDS differential data (-)

0 1 2 3 4 5 6 7

Display data signal:

TX2+ I TMDS differential data (+)

R , R , R , R , R , R , R , R

TX2- I 0 1 2 3 4 5 6 7 TMDS differential data (-)

TXC+ I TMDS differential clock (+)

Data clock signal:

DCLK

TXC- I TMDS differential clock (-)

A.1.3.3 Pin assignment

Table A.7 shows an example of the pin assignments of TMDS.

Table A.7 – Example of pin assignment of connector

Pin no Pin name

1 TX1 +

2 TX1 -

3 TX1 SHELD

4 TXC SHELD

5 TXC +

6 TXC -

7 GND

8 +5VDC

9 RES

10 RES

11 TX2 +

12 TX2 -

13 TX2 SHELD

14 TX0 SHELD

15 TX0 +

16 TX0 -

17 RES

18 SENS

19 DDC/SDA

20 DDC/SCL

NOTE SDA is the abbreviation for ‘Serial data’, and SCL for ‘Serial clock’.

– 22 – 61988-3-2 © IEC:2009

A.1.3.4 Input signal timing chart

Description of input signal timing chart is basically same as that of LVDS. (See Figure A.2.)

A.1.3.5 Input signal timing specification

Description of input signal timing specification is basically same as that of LVDS. (See Table

A.3.)

A.2 Function control signal

Function control signal is the additional signal, except digital video signal, to control the

functions such as APC, SDA and SCL.

A.3 Electrical characteristics

A.3.1 Limiting values (Absolute maximum rating system)

Limiting values (Absolute maximum rating system) are those values beyond which the safety

of the device cannot be guaranteed.

Table A.8 shows an example of Limiting values (Absolute maximum rating system).

Table A.8 –Limiting values (Absolute maximum rating system)

Subclause Limiting values Symbol Value Unit

Min. Max.

A.1.1 Supply voltage V –0,3 4 V

CC

range of LVDS

A.1.2 Supply voltage V –0,5 7 V

CC

range of TTL

A.1.3 Supply voltage V –0,3 4 V

CC

range of TMDS

61988-3-2 © IEC:2009 – 23 –

A.3.2 Signal voltage and current

Table A.9 shows an example of the electrical characteristics of LVDS, TMDS and TTL.

Table A.9 – Electrical characteristics

Signal Parameter Symbol Conditions Min. Typ. Max. Unit

Common mode

V V = 3,3 V

1,125 1,25 1,375 mV

OC CC

Voltage

Differential

V = +1,2 V

OC

input high

V

100 mV

TH

= 3,3 V

V

CC

LVDS Threshold

Receiver

Differential

V = +1,2 V

OC

input low

V

–100 mV

TL

V = 3,3 V

CC

Threshold

V = +2,4 V / 0 V

Input

IN

I

±10 μA

IN

Current V = 3,6 V

CC

Differential

input

V V = 3,3 V

150 1200 mV

idiff CC

Voltage

Input

TMDS

common

V V = 3,3 V V – 300

V – 37

mV

icm CC CC

CC

Receiver

Mode

Voltage

Open circuit

V V = 3,3 V V – 10 V – 10

mV

I(OC) CC CC CC

Input Voltage

High–level

inp

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...