IEC 62343-4-1:2016

(Main)Dynamic modules - Part 4-1: Software and hardware interface - 1 x 9 wavelength selective switch

Dynamic modules - Part 4-1: Software and hardware interface - 1 x 9 wavelength selective switch

IEC 62343-4-1:2016 describes and provides specifications for a software and hardware interface for the 1 x 9 wavelength selective switch. These switches can be controlled by resident firmware with this interface. This standard addresses the configuration and function to control a WSS. This interface is intended to enable a user or host to retrieve the switch status and/or adjust relevant switch and attenuation settings.

Modules dynamiques - Partie 4-1 : Interface logicielle et matérielle - Commutateur sélectif en longueur d'onde 1 x 9

IEC 62323-4-1:2016 décrit et fournit des spécifications d'une interface logicielle et matérielle pour le commutateur sélectif en longueur d'onde 1 x 9. Ces commutateurs peuvent être contrôlés par un micrologiciel résident et cette interface. La présente norme couvre la configuration et les fonctions permettant de contrôler un WSS. L'interface est destinée à permettre à un utilisateur ou à un hôte de récupérer l'état du commutateur et/ou de régler le commutateur en question et l'affaiblissement.

Mots clés: Un commutateur sélectif en longueur d’onde (WWS), multiplexage optique d'insertion-extraction reconfigurable (ROADM), multiplexage par répartition en longueur d’onde à forte densité (DWDM)

General Information

- Status

- Published

- Publication Date

- 03-Mar-2016

- Technical Committee

- SC 86C - Fibre optic systems, sensing and active devices

- Drafting Committee

- WG 5 - TC 86/SC 86C/WG 5

- Current Stage

- PPUB - Publication issued

- Start Date

- 04-Mar-2016

- Completion Date

- 15-Jun-2016

Overview

IEC 62343-4-1:2016 defines the software and hardware interface for a 1 x 9 wavelength selective switch (WSS) - a dynamic module used in DWDM/ROADM systems to route and attenuate individual wavelength channels. The standard specifies how a host controller (HC) or resident firmware controls the WSS, how status and alarm information are exposed, and the electrical and memory interfaces used for command/response (notably a DPRAM interface and optional RS232).

Key topics and technical requirements

- Interface scope: Configuration and function to control a 1 x 9 WSS - retrieve switch status, set switch mapping and attenuation, and store settings in non‑volatile memory.

- Primary control paths:

- DPRAM interface: 12‑bit address bus and 16‑bit data bus between HC and WSS module; DPRAM control signals include R/W, CE (active low), OE (active low).

- RS232: Optional serial TxD / RxD channel for communication.

- Control and status signals:

- START (active low input) to trigger commands

- DONE, ERROR outputs for command completion/status

- BUSY (active low) to indicate contention on DPRAM

- MASTER RESET and SOFT RESET inputs

- READY (asserted as logic 0) and ALARM outputs

- Memory and commands:

- DPRAM memory map (examples shown in the standard): e.g., 0x0001 = hardware/software version (RO); 0x0020 = command register (RW); 0x0021 = command code (RW); 0x0022 = command data 1 (RW)

- Annex B provides detailed DPRAM memory map variations and timing charts for read/write cycles, power on, reset and alarm timing.

- Electrical details:

- Interface operates at low voltage +3.3 V logic levels

- Annex A gives connector form, pin assignment, supply and threshold details (electrical connector and supply current specs are included in the standard).

Applications and who uses it

- Module manufacturers: implement the standardized DPRAM/RS232 interface and pinout so their 1 x 9 WSS modules are interoperable with host controllers.

- Firmware and hardware engineers: develop resident firmware, FPGA/DSP logic, and host drivers that follow the command register map and timing requirements.

- System integrators and network equipment vendors: integrate WSS modules into ROADMs and chassis using consistent control and alarm semantics.

- Test labs / certification bodies: verify compliance with DPRAM timing, reset behavior and functional command responses.

- Network operators: benefit indirectly via predictable control, consistent status reporting and reliable non‑volatile configuration storage for DWDM networks.

Related standards

- IEC 62343 (Dynamic modules - general guidance)

- IEC 60050-731 (Optical fibre communication vocabulary) - normative references used in the standard

Keywords: IEC 62343-4-1:2016, wavelength selective switch, WSS, 1x9 WSS, DPRAM interface, RS232, DWDM, ROADM, firmware interface, optical networking, module control.

IEC 62343-4-1:2016 - Dynamic modules - Part 4-1: Software and hardware interface - 1 x 9 wavelength selective switch Released:3/4/2016 Isbn:9782832231999

IEC 62343-4-1:2016 - Dynamic modules - Part 4-1: Software and hardware interface - 1 x 9 wavelength selective switch

Get Certified

Connect with accredited certification bodies for this standard

TL 9000 QuEST Forum

Telecommunications quality management system.

ANCE

Mexican certification and testing association.

Intertek Slovenia

Intertek testing, inspection, and certification services in Slovenia.

Sponsored listings

Frequently Asked Questions

IEC 62343-4-1:2016 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Dynamic modules - Part 4-1: Software and hardware interface - 1 x 9 wavelength selective switch". This standard covers: IEC 62343-4-1:2016 describes and provides specifications for a software and hardware interface for the 1 x 9 wavelength selective switch. These switches can be controlled by resident firmware with this interface. This standard addresses the configuration and function to control a WSS. This interface is intended to enable a user or host to retrieve the switch status and/or adjust relevant switch and attenuation settings.

IEC 62343-4-1:2016 describes and provides specifications for a software and hardware interface for the 1 x 9 wavelength selective switch. These switches can be controlled by resident firmware with this interface. This standard addresses the configuration and function to control a WSS. This interface is intended to enable a user or host to retrieve the switch status and/or adjust relevant switch and attenuation settings.

IEC 62343-4-1:2016 is classified under the following ICS (International Classification for Standards) categories: 33.180.20 - Fibre optic interconnecting devices. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62343-4-1:2016 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 62343-4-1 ®

Edition 1.0 2016-03

INTERNATIONAL

STANDARD

Dynamic modules –

Part 4-1: Software and hardware interface – 1 x 9 wavelength selective switch

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

IEC Catalogue - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

The stand-alone application for consulting the entire The world's leading online dictionary of electronic and

bibliographical information on IEC International Standards, electrical terms containing 20 000 terms and definitions in

Technical Specifications, Technical Reports and other English and French, with equivalent terms in 15 additional

documents. Available for PC, Mac OS, Android Tablets and languages. Also known as the International Electrotechnical

iPad. Vocabulary (IEV) online.

IEC publications search - www.iec.ch/searchpub IEC Glossary - std.iec.ch/glossary

The advanced search enables to find IEC publications by a 65 000 electrotechnical terminology entries in English and

variety of criteria (reference number, text, technical French extracted from the Terms and Definitions clause of

committee,…). It also gives information on projects, replaced IEC publications issued since 2002. Some entries have been

and withdrawn publications. collected from earlier publications of IEC TC 37, 77, 86 and

CISPR.

IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published IEC Customer Service Centre - webstore.iec.ch/csc

details all new publications released. Available online and If you wish to give us your feedback on this publication or

also once a month by email. need further assistance, please contact the Customer Service

Centre: csc@iec.ch.

IEC 62343-4-1 ®

Edition 1.0 2016-03

INTERNATIONAL

STANDARD

Dynamic modules –

Part 4-1: Software and hardware interface – 1 x 9 wavelength selective switch

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

ICS 33.180.20 ISBN 978-2-8322-3199-9

– 2 – IEC 62343-4-1:2016 © IEC 2016

CONTENTS

FOREWORD . 3

INTRODUCTION . 5

1 Scope . 6

2 Normative references. 6

3 Terms, definitions and abbreviations . 6

3.1 Terms and definitions . 6

3.2 Abbreviations . 6

4 Basic configuration of WSS interface . 7

5 Software interface . 8

6 Hardware interface – Electrical connector . 11

Annex A (informative) Hardware interface details . 12

Annex B (informative) DPRAM memory map details and timing charts . 14

Bibliography . 30

Figure 1 – Basic configuration of WSS interface . 7

Figure B.1 – DPRAM READ CYCLE timing . 25

Figure B.2 – DPRAM WRITE CYCLE timing . 26

Figure B.3 – POWER ON timing . 26

Figure B.4 – START timing. 27

Figure B.5 – MASTER RESET timing . 27

Figure B.6 – SOFT RESET timing . 28

Figure B.7 – DPRAM BUSY timing . 28

Figure B.8 – ALARM timing . 29

Table 1 – Software interface . 9

Table 2 – DPRAM memory map . 10

Table A.1 – Connector form . 12

Table A.2 – Pin assignment . 12

Table A.3 – Supply voltages and currents . 13

Table A.4 – Low voltage TTL thresholds . 13

Table A.5 – Power consumption . 13

Table B.1 – DPRAM memory map specification A . 14

Table B.2 – DPRAM memory map specification B . 15

Table B.3 – Signal time specification . 24

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

DYNAMIC MODULES –

Part 4-1: Software and hardware interface –

1 x 9 wavelength selective switch

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62343-4-1 has been prepared by subcommittee SC86C: Fibre

optic systems and active devices, of IEC technical committee 86: Fibre optics.

The text of this standard is based on the following documents:

CDV Report on voting

86C/1304/CDV 86C/1346/RVC

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 62343 series, published under the general title Dynamic modules,

can be found on the IEC website.

– 4 – IEC 62343-4-1:2016 © IEC 2016

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

A bilingual version of this publication may be issued at a later date.

INTRODUCTION

A wavelength selective switch (WSS) is a dynamic module, which is mainly used in a

reconfigurable optical add drop multiplexer (ROADM) system to switch all wavelength signals

to their respective required output port in dense wavelength division multiplexing (DWDM)

networks. The WSS module has one input port and a plurality of output ports (i.e. 1 x N WSS)

and can be used reversely, such as N input ports and one output port, depending on its

application. It is electrically controlled with software, which directs each wavelength signal

among an input DWDM signal from one input port to the required output port for each

wavelength signal.

– 6 – IEC 62343-4-1:2016 © IEC 2016

DYNAMIC MODULES –

Part 4-1: Software and hardware interface –

1 x 9 wavelength selective switch

1 Scope

This part of IEC 62343 describes and provides specifications for a software and hardware

interface for the 1 x 9 wavelength selective switch.

These switches can be controlled by resident firmware with this interface. This standard

addresses the configuration and function to control a WSS. This interface is intended to

enable a user or host to retrieve the switch status and/or adjust relevant switch and

attenuation settings.

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60050-731, International Electrotechnical Vocabulary – Chapter 731: Optical fibre

communication (available at http://www.electropedia.org)

IEC 62343, Dynamic modules - General and guidance

3 Terms, definitions and abbreviations

3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60050-731 and

IEC 62343, as well as the following apply.

3.1.1

wavelength selective switch

WSS

dynamic module with one or more input ports and one or more output ports, which is mainly

used in a reconfigurable optical add drop multiplexer (ROADM) system to switch each

wavelength signal on each input port independently to its required output port in DWDM

networks

Note 1 to entry: It is electrically controlled with software.

Note 2 to entry: It can be used inverted, exchanging input and output ports.

Note 3 to entry: Each wavelength signal can be independently attenuated.

3.2 Abbreviations

For the purposes of this document, the following abbreviations apply.

DWDM dense wavelength division multiplexing

WSS wavelength selective switch

ROADM reconfigurable optical add drop multiplexer

HC host controller

DPRAM dual-port RAM

FPGA field programmable gate array

DSP digital signal processor

R/W read or write

RW read and write

RO read only

CE chip enable

OE output enable

TxD transmitted data

RxD received data

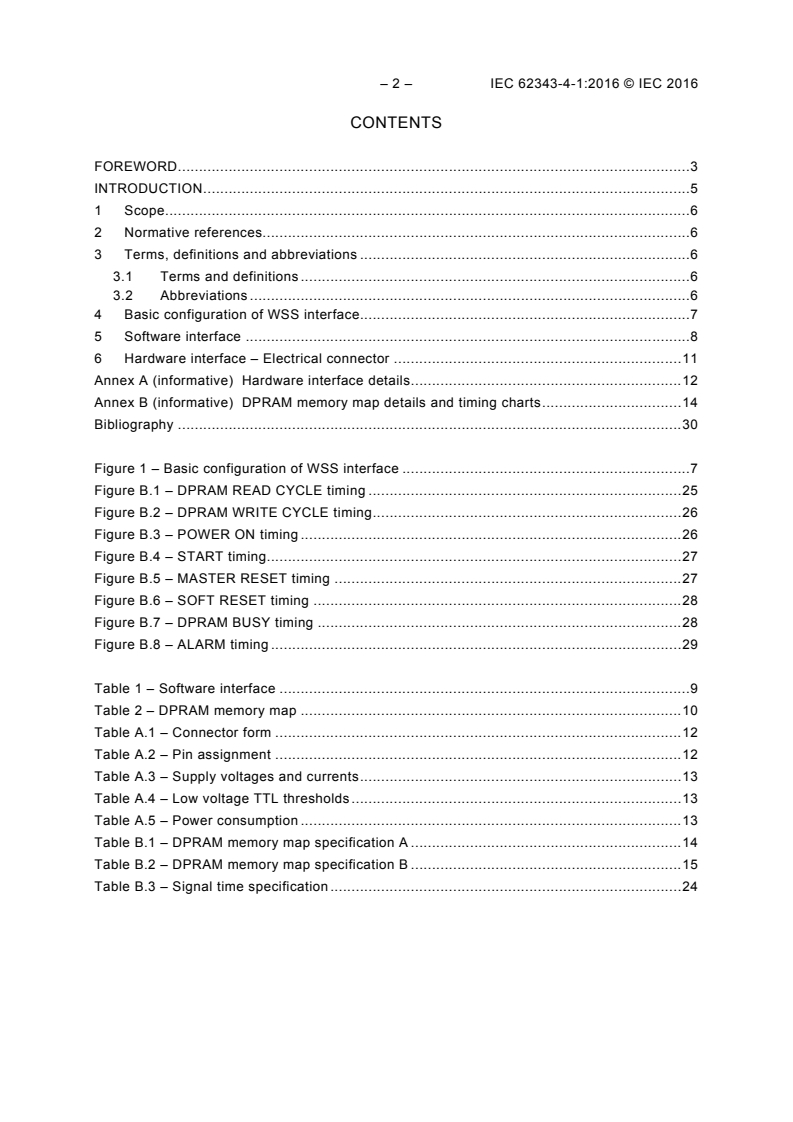

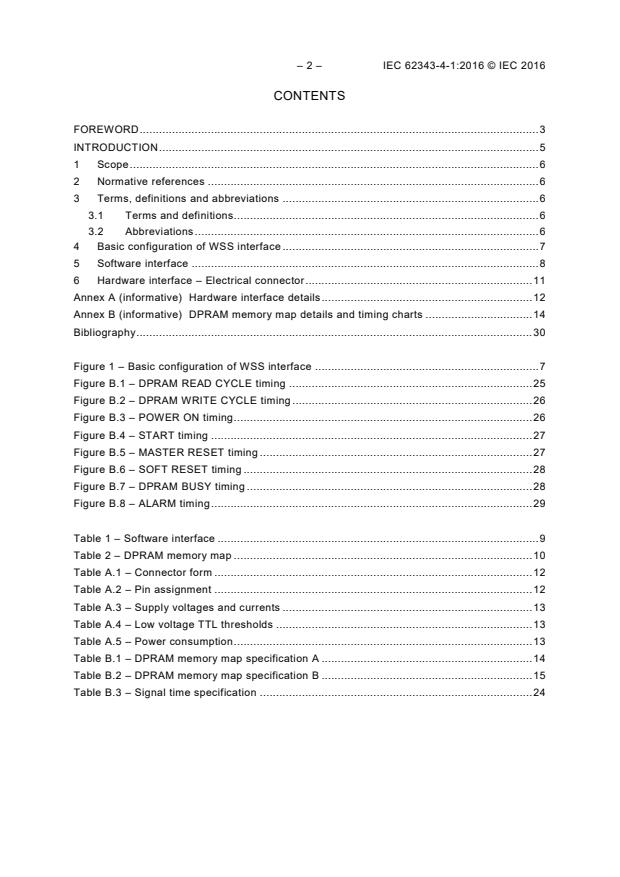

4 Basic configuration of WSS interface

The software interface is intended to provide an access to the functions of the WSS module

and be the primary interface to command the unit. The HC controls the WSS module by

sending control signal, as well as command data, to the WSS module via a 12-bit address bus,

a 16-bit data bus, and DPRAM related signal lines such as Read/Write, Chip Enable, and

Output Enable. The HC also receives from the WSS module response signals and status data.

Any address within the DPRAM can be written to via the HC, however many of these values

will be overwritten upon the application of a command to the WSS module. The addresses,

which are identified as inputs, can be found further along in this document. In addition to the

DPRAM interface, RS232 serial communication is also supported by the WSS module.

The WSS module has a non-volatile memory to store the latest setting when requested. A

functional diagram of the WSS module controls is illustrated in Figure 1 below.

HC WSS module

DPRAM Address bus (12)

DPRAM Date bus (16)

DSP/ Optical

FPGA engine

DPRAM Control

RS232C TxD

RS232C RxD

Interface

MASTER RESET

Memory

SOFT RESET

READY

ALARM

IEC

Figure 1 – Basic configuration of WSS interface

– 8 – IEC 62343-4-1:2016 © IEC 2016

5 Software interface

The signals between the HC and the WSS module are low voltage +3,3 V logic levels. The

definitions of the signals and memory map are described in Table 1 and Table 2. Annex A

provides additional information on pin assignment. Annex B provides additional information

DPRAM memory map and timing charts.

Table 1 – Software interface

No Functional Name Input/output Definitions

block

1 DPRAM Address (12- Input 12-bit address bus of DPRAM.

bit wide)

Data (16- Input/output 16-bit wide data bus of DPRAM.

bit wide)

START Input WSS module start input signal. This strobe is generated

by the HC to command the WSS module to perform a

specified task defined in command word 2. This signal is

an active low input signal.

DONE Output Done output signal. A level high is generated by the WSS

module when a specified task is completed.

ERROR Output Error output signal. A level high is generated by the WSS

module when it detects an error condition.

BUSY Output Busy output signal. This signal indicates that both the

WSS module and HC are trying to access the same dual

port RAM address at the same time. This signal is an

active low signal.

Read/write enable

(R/W) input signal.

This signal is

generated by the HC

to enable reading of

data from dual port

RAM, or writing of

data to dual port

RAM.

Chip enable (CE)

input signal. This

signal is generated

by the HC to select

the dual port RAM

devices. This signal

is an active low

signal.

– 10 – IEC 62343-4-1:2016 © IEC 2016

No Functional Name Input/output Definitions

block

Chip output enable

(OE) input signal.

This signal is

generated by the HC

to enable the dual

port RAM to send out

data on the data bus.

This signal is an

active low signal.

2 RS232C TxD Output Transmitted data (TxD): This signal is active when data is

transmitted from the WSS module to the HC. When no

data is transmitted, the signal is held in the mark

condition.

RxD Input Received data (RxD): This signal is active when the WSS

module receives data from the HC. When no data is

transmitted, the signal is held in the mark condition.

3 Module control MASTER Input Input signal. This strobe is generated by the HC to

RESET command the WSS module to perform Master reset which

affects optical configurations of the module. This signal is

an active low input signal.

SOFT RESET Input Input signal. This resets the WSS module DSP without

affecting optical state of the WSS module. This signal is

an active low input signal.

READY Output This signal is asserted (logic '0') by the WSS module to

inform the HC that transmission may begin.

ALARM Output This signal is generated by the WSS module when a

hardware alarm or a software alarm is generated.

Table 2 – DPRAM memory map

No. Address Content R/W Notes

1 0x0001 Hardware and software version RO The hardware and software versions are

embedded.

2 0x0020 Command register RW

3 0x0021 Command code register RW

4 0x0022 Command data 1 register RW

5 0x0023 Status register RW

6 0x0025 Error code register RW

7 0x0028 WSS case temperature RO

8 0x0029 Hardware error register RO

9 0x0034 Command data 2 register RW

10 0x0035 Command data 3 register RW

6 Hardware interface – Electrical connector

The electrical connector on the WSS module is an 80-contact receptacle. Annex A provides

additional information on connector form.

– 12 – IEC 62343-4-1:2016 © IEC 2016

Annex A

(informative)

Hardware interface details

Annex A describes two kinds of interfaces. All specifications in Annex A are informative. It is

recommended that the user chooses either connector form A or B. Table A.1 gives details on

connector form, Table A.2 on pin assignment, Table A.3 on the supply voltages and currents

for WSS module, Table A.4 on low voltage TTL thresholds and Table A.5 on power

consumption.

Table A.1 – Connector form

No Parameter Connector form A Connector form B

1 Connector form Samtec CLT-140-02-G-D-BE-A Samtec CLP-140-02-S-D

Table A.2 – Pin assignment

Functional

No Name Pin assignment A Pin assignment B

block

DPRA 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

10, 11

Dual port Address bit 0 to 11,

1 Address (12-bit wide)

RAM pin 51 to 62

Pin 70, 68, 66, 64, 62, 60, 58,

56, 54, 52, 48

DPRD 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

10, 11, 12, 13, 14,15

Data (16-bit wide) Data bit 0 to 15, pin 1 to 16

Pin 44, 42, 40, 38, 36, 34, 32,

30, 28, 26, 24, 22, 20, 18, 16,

START START, pin 21 nSTART, pin 27

DONE DONE, pin 23 DONE, pin 25

ERROR ERROR, pin 25 ERROR, pin 23

BUSY BUSY, pin 26, low nBUSY, pin 29

Read Write from RAM Read Write from RAM, pin 45 R/nW, pin 15

RAM Chip Enable RAM Chip Enable, pin 47 nCE, pin 13

RAM Chip Output RAM Chip Output Enable, pin

nOE, pin 17

Enable 48

2 RS232C TxD TxD, pin 65 TxD, pin 51

RxD RxD, pin 66 RxD, pin 53

Module

3 MASTER RESET MASTER RESET, pin 19 nRST, pin 74

control

SOFT RESET HARD RESET, pin 46 nSWRST, pin 67

READY CTS, pin 20 nREADY, pin 61

ALARM, pin 31 or nFAULT, pin

ALARM WDERR, pin 24

Table A.3 – Supply voltages and currents

Supply voltage and current A Supply voltage and current B

No Parameter Unit

Min. Typ. Max. Min. Typ. Max.

1 Supply voltage +3,3 V +3,14 +3,3 +3,5 NA NA NA V

2 Supply voltage +5,0 V +4,75 +5,0 +5,25 +4,75 +5,0 +5,6 V

Supply voltage

3 +4,75 +5,0 +5,25 +4,75 +5,0 +5,6 V

+5,0 V-Analog

Supply voltage

4 NA NA NA V

+14,25 +15,0 +15,75

+15,0 V-Analog

Supply voltage

5 -15,75 -15,0 -14,25 NA NA NA V

-15,0 V-Analog

6 NA NA NA NA NA A

Supply current +3,3 V +3,0

7 NA NA NA NA A

Supply current +5,0 V +2,0 +7,0

Supply current

8 NA NA NA NA NA A

+2,0

+5,0 V-Analog

Supply current

9 NA NA +1,0 NA NA NA A

+15,0 V-Analog

Supply current

10 NA NA 1,0 NA NA NA A

-15,0 V-Analog

All the WSS control signals are LVTTL CMOS (3,3 V). The voltage level thresholds are as

specified in Table A.4 below.

Table A.4 – Low voltage TTL thresholds

Low voltage TTL thresholds A Low voltage TTL thresholds B

No Parameter Unit

Min. Max. Min. Max.

1 Logic low input level NA -0,2 V

+0,8 +0,8

2 Logic high input level +2,0 +5,5 +2,0 +3,45 V

3 Logic low output level NA +0,4 NA +0,4 V

4 Logic high output level NA V

+2,4 +3,3 +2,8

Table A.5 – Power consumption

Power

Power consumption B

consumption A

No Parameter Unit

Max. Max.

Power

a

1 10 33 W

consumption

a

Including warm-up.

– 14 – IEC 62343-4-1:2016 © IEC 2016

Annex B

(informative)

DPRAM memory map details and timing charts

Annex B describes two types of DPRAM interfaces. All specifications in Annex B are

informative. It is recommended that the user chooses either specification A or B. Table B.1

provides the DPRAM memory map for specification A. Table B.2 provides the DPRAM

memory map for specification B. Table B.3 provides the signal time specification for both the

A and B interfaces. Figure B.1 through to Figure B.8 show the timing relationships of the

signals.

Table B.1 – DPRAM memory map specification A

Address Content (16 bits) Direction Note

From WSS The hardware and firmware

0x0001 Hardware and firmware version

module versions are embedded.

0x0020 Command register From host

controller

0x0021 Command code register

0x0022 Command data 1

From WSS Indicates command execution

0x0023 Status 1

module status, ready or error

Status code (contains results of

0x0024 Status 2

executed command)

0x0025 Error code

Temperature of WSS. This

0x0028 WSS module temperature address will be updated upon

receiving any command.

0x0029 Hardware failure register

0x0034 Command data 2 From host

controller

0x0035 Command data 3

Required port and differential From host Attenuation spectrum and port

Starting at 0x200

attenuation for each channel controller settings required

Port setting and accumulated differential From WSS Port settings and running sum of

Starting at 0x400

attenuations for each channel module differential attenuation

Stored port and accumulated From WSS Every time "store" command is

Starting at 0x600 attenuations for each channel read from module issued, the stored value is also

non-volatile RAM copied at 0x600

0x0803 Attenuation range (controllable range) The default stored value is 20 dB.

From WSS

Starting at 0x900 Wavelength of each channel Channel wavelength information

module

0x0F00- From host

User's reserved Confirmation module access

0x0FFF controller

Table B.2 – DPRAM memory map specification B

Initial

Address Content R/W Data type Note

value

Device identification and version information registers

Assigned by customer (constant

0x0000 Supplier identifier RO Number Invariant

compiled into the code-base)

This is a reduced detail version of the

0x0001 Version number RO Number Invariant version number. It includes both

hardware and software versions.

Assigned by customer (constant

0x0002 Part identifier RO Nu

...

IEC 62343-4-1 ®

Edition 1.0 2016-03

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Dynamic modules –

Part 4-1: Software and hardware interface – 1 x 9 wavelength selective switch

Modules dynamiques –

Partie 4-1: Interface logicielle et matérielle – Commutateur sélectif en longueur

d'onde 1 x 9

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

IEC Catalogue - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

The stand-alone application for consulting the entire The world's leading online dictionary of electronic and

bibliographical information on IEC International Standards, electrical terms containing 20 000 terms and definitions in

Technical Specifications, Technical Reports and other English and French, with equivalent terms in 16 additional

documents. Available for PC, Mac OS, Android Tablets and languages. Also known as the International Electrotechnical

iPad. Vocabulary (IEV) online.

IEC publications search - www.iec.ch/searchpub IEC Glossary - std.iec.ch/glossary

The advanced search enables to find IEC publications by a 65 000 electrotechnical terminology entries in English and

variety of criteria (reference number, text, technical French extracted from the Terms and Definitions clause of

committee,…). It also gives information on projects, replaced IEC publications issued since 2002. Some entries have been

and withdrawn publications. collected from earlier publications of IEC TC 37, 77, 86 and

CISPR.

IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published IEC Customer Service Centre - webstore.iec.ch/csc

details all new publications released. Available online and If you wish to give us your feedback on this publication or

also once a month by email. need further assistance, please contact the Customer Service

Centre: csc@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Catalogue IEC - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

Application autonome pour consulter tous les renseignements

Le premier dictionnaire en ligne de termes électroniques et

bibliographiques sur les Normes internationales,

électriques. Il contient 20 000 termes et définitions en anglais

Spécifications techniques, Rapports techniques et autres

et en français, ainsi que les termes équivalents dans 16

documents de l'IEC. Disponible pour PC, Mac OS, tablettes

langues additionnelles. Egalement appelé Vocabulaire

Android et iPad.

Electrotechnique International (IEV) en ligne.

Recherche de publications IEC - www.iec.ch/searchpub

Glossaire IEC - std.iec.ch/glossary

65 000 entrées terminologiques électrotechniques, en anglais

La recherche avancée permet de trouver des publications IEC

en utilisant différents critères (numéro de référence, texte, et en français, extraites des articles Termes et Définitions des

comité d’études,…). Elle donne aussi des informations sur les publications IEC parues depuis 2002. Plus certaines entrées

projets et les publications remplacées ou retirées. antérieures extraites des publications des CE 37, 77, 86 et

CISPR de l'IEC.

IEC Just Published - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications IEC. Just

Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur cette

Disponible en ligne et aussi une fois par mois par email. publication ou si vous avez des questions contactez-nous:

csc@iec.ch.

IEC 62343-4-1 ®

Edition 1.0 2016-03

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Dynamic modules –

Part 4-1: Software and hardware interface – 1 x 9 wavelength selective switch

Modules dynamiques –

Partie 4-1: Interface logicielle et matérielle – Commutateur sélectif en longueur

d'onde 1 x 9

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 33.180.20 ISBN 978-2-8322-4710-5

– 2 – IEC 62343-4-1:2016 © IEC 2016

CONTENTS

FOREWORD . 3

INTRODUCTION . 5

1 Scope . 6

2 Normative references . 6

3 Terms, definitions and abbreviations . 6

3.1 Terms and definitions . 6

3.2 Abbreviations . 6

4 Basic configuration of WSS interface . 7

5 Software interface . 8

6 Hardware interface – Electrical connector . 11

Annex A (informative) Hardware interface details . 12

Annex B (informative) DPRAM memory map details and timing charts . 14

Bibliography . 30

Figure 1 – Basic configuration of WSS interface . 7

Figure B.1 – DPRAM READ CYCLE timing . 25

Figure B.2 – DPRAM WRITE CYCLE timing . 26

Figure B.3 – POWER ON timing . 26

Figure B.4 – START timing . 27

Figure B.5 – MASTER RESET timing . 27

Figure B.6 – SOFT RESET timing . 28

Figure B.7 – DPRAM BUSY timing . 28

Figure B.8 – ALARM timing . 29

Table 1 – Software interface . 9

Table 2 – DPRAM memory map . 10

Table A.1 – Connector form . 12

Table A.2 – Pin assignment . 12

Table A.3 – Supply voltages and currents . 13

Table A.4 – Low voltage TTL thresholds . 13

Table A.5 – Power consumption . 13

Table B.1 – DPRAM memory map specification A . 14

Table B.2 – DPRAM memory map specification B . 15

Table B.3 – Signal time specification . 24

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

DYNAMIC MODULES –

Part 4-1: Software and hardware interface –

1 x 9 wavelength selective switch

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62343-4-1 has been prepared by subcommittee SC86C: Fibre

optic systems and active devices, of IEC technical committee 86: Fibre optics.

The text of this standard is based on the following documents:

CDV Report on voting

86C/1304/CDV 86C/1346/RVC

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 62343 series, published under the general title Dynamic modules,

can be found on the IEC website.

– 4 – IEC 62343-4-1:2016 © IEC 2016

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

INTRODUCTION

A wavelength selective switch (WSS) is a dynamic module, which is mainly used in a

reconfigurable optical add drop multiplexer (ROADM) system to switch all wavelength signals

to their respective required output port in dense wavelength division multiplexing (DWDM)

networks. The WSS module has one input port and a plurality of output ports (i.e. 1 x N WSS)

and can be used reversely, such as N input ports and one output port, depending on its

application. It is electrically controlled with software, which directs each wavelength signal

among an input DWDM signal from one input port to the required output port for each

wavelength signal.

– 6 – IEC 62343-4-1:2016 © IEC 2016

DYNAMIC MODULES –

Part 4-1: Software and hardware interface –

1 x 9 wavelength selective switch

1 Scope

This part of IEC 62343 describes and provides specifications for a software and hardware

interface for the 1 x 9 wavelength selective switch.

These switches can be controlled by resident firmware with this interface. This standard

addresses the configuration and function to control a WSS. This interface is intended to

enable a user or host to retrieve the switch status and/or adjust relevant switch and

attenuation settings.

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60050-731, International Electrotechnical Vocabulary – Chapter 731: Optical fibre

communication (available at http://www.electropedia.org)

IEC 62343, Dynamic modules - General and guidance

3 Terms, definitions and abbreviations

3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60050-731 and

IEC 62343, as well as the following apply.

3.1.1

wavelength selective switch

WSS

dynamic module with one or more input ports and one or more output ports, which is mainly

used in a reconfigurable optical add drop multiplexer (ROADM) system to switch each

wavelength signal on each input port independently to its required output port in DWDM

networks

Note 1 to entry: It is electrically controlled with software.

Note 2 to entry: It can be used inverted, exchanging input and output ports.

Note 3 to entry: Each wavelength signal can be independently attenuated.

3.2 Abbreviations

For the purposes of this document, the following abbreviations apply.

DWDM dense wavelength division multiplexing

WSS wavelength selective switch

ROADM reconfigurable optical add drop multiplexer

HC host controller

DPRAM dual-port RAM

FPGA field programmable gate array

DSP digital signal processor

R/W read or write

RW read and write

RO read only

CE chip enable

OE output enable

TxD transmitted data

RxD received data

4 Basic configuration of WSS interface

The software interface is intended to provide an access to the functions of the WSS module

and be the primary interface to command the unit. The HC controls the WSS module by

sending control signal, as well as command data, to the WSS module via a 12-bit address bus,

a 16-bit data bus, and DPRAM related signal lines such as Read/Write, Chip Enable, and

Output Enable. The HC also receives from the WSS module response signals and status data.

Any address within the DPRAM can be written to via the HC, however many of these values

will be overwritten upon the application of a command to the WSS module. The addresses,

which are identified as inputs, can be found further along in this document. In addition to the

DPRAM interface, RS232 serial communication is also supported by the WSS module.

The WSS module has a non-volatile memory to store the latest setting when requested. A

functional diagram of the WSS module controls is illustrated in Figure 1 below.

HC WSS module

DPRAM Address bus (12)

DPRAM Date bus (16)

DSP/ Optical

FPGA engine

DPRAM Control

RS232C TxD

RS232C RxD

Interface

MASTER RESET

Memory

SOFT RESET

READY

ALARM

IEC

Figure 1 – Basic configuration of WSS interface

– 8 – IEC 62343-4-1:2016 © IEC 2016

5 Software interface

The signals between the HC and the WSS module are low voltage +3,3 V logic levels. The

definitions of the signals and memory map are described in Table 1 and Table 2. Annex A

provides additional information on pin assignment. Annex B provides additional information

DPRAM memory map and timing charts.

Table 1 – Software interface

No Functional Name Input/output Definitions

block

1 DPRAM Address (12- Input 12-bit address bus of DPRAM.

bit wide)

Data (16- Input/output 16-bit wide data bus of DPRAM.

bit wide)

START Input WSS module start input signal. This strobe is generated

by the HC to command the WSS module to perform a

specified task defined in command word 2. This signal is

an active low input signal.

DONE Output Done output signal. A level high is generated by the WSS

module when a specified task is completed.

ERROR Output Error output signal. A level high is generated by the WSS

module when it detects an error condition.

BUSY Output Busy output signal. This signal indicates that both the

WSS module and HC are trying to access the same dual

port RAM address at the same time. This signal is an

active low signal.

Read/write enable

(R/W) input signal.

This signal is

generated by the HC

to enable reading of

data from dual port

RAM, or writing of

data to dual port

RAM.

Chip enable (CE)

input signal. This

signal is generated

by the HC to select

the dual port RAM

devices. This signal

is an active low

signal.

– 10 – IEC 62343-4-1:2016 © IEC 2016

No Functional Name Input/output Definitions

block

Chip output enable

(OE) input signal.

This signal is

generated by the HC

to enable the dual

port RAM to send out

data on the data bus.

This signal is an

active low signal.

2 RS232C TxD Output Transmitted data (TxD): This signal is active when data is

transmitted from the WSS module to the HC. When no

data is transmitted, the signal is held in the mark

condition.

RxD Input Received data (RxD): This signal is active when the WSS

module receives data from the HC. When no data is

transmitted, the signal is held in the mark condition.

3 Module control MASTER Input Input signal. This strobe is generated by the HC to

RESET command the WSS module to perform Master reset which

affects optical configurations of the module. This signal is

an active low input signal.

SOFT RESET Input Input signal. This resets the WSS module DSP without

affecting optical state of the WSS module. This signal is

an active low input signal.

READY Output This signal is asserted (logic '0') by the WSS module to

inform the HC that transmission may begin.

ALARM Output This signal is generated by the WSS module when a

hardware alarm or a software alarm is generated.

Table 2 – DPRAM memory map

No. Address Content R/W Notes

1 0x0001 Hardware and software version RO The hardware and software versions are

embedded.

2 0x0020 Command register RW

3 0x0021 Command code register RW

4 0x0022 Command data 1 register RW

5 0x0023 Status register RW

6 0x0025 Error code register RW

7 0x0028 WSS case temperature RO

8 0x0029 Hardware error register RO

9 0x0034 Command data 2 register RW

10 0x0035 Command data 3 register RW

6 Hardware interface – Electrical connector

The electrical connector on the WSS module is an 80-contact receptacle. Annex A provides

additional information on connector form.

– 12 – IEC 62343-4-1:2016 © IEC 2016

Annex A

(informative)

Hardware interface details

Annex A describes two kinds of interfaces. All specifications in Annex A are informative. It is

recommended that the user chooses either connector form A or B. Table A.1 gives details on

connector form, Table A.2 on pin assignment, Table A.3 on the supply voltages and currents

for WSS module, Table A.4 on low voltage TTL thresholds and Table A.5 on power

consumption.

Table A.1 – Connector form

No Parameter Connector form A Connector form B

1 Connector form Samtec CLT-140-02-G-D-BE-A Samtec CLP-140-02-S-D

Table A.2 – Pin assignment

Functional

No Name Pin assignment A Pin assignment B

block

DPRA 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

10, 11

Dual port Address bit 0 to 11,

1 Address (12-bit wide)

RAM pin 51 to 62

Pin 70, 68, 66, 64, 62, 60, 58,

56, 54, 52, 48

DPRD 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

10, 11, 12, 13, 14,15

Data (16-bit wide) Data bit 0 to 15, pin 1 to 16

Pin 44, 42, 40, 38, 36, 34, 32,

30, 28, 26, 24, 22, 20, 18, 16,

START START, pin 21 nSTART, pin 27

DONE DONE, pin 23 DONE, pin 25

ERROR ERROR, pin 25 ERROR, pin 23

BUSY BUSY, pin 26, low nBUSY, pin 29

Read Write from RAM Read Write from RAM, pin 45 R/nW, pin 15

RAM Chip Enable RAM Chip Enable, pin 47 nCE, pin 13

RAM Chip Output RAM Chip Output Enable, pin

nOE, pin 17

Enable 48

2 RS232C TxD TxD, pin 65 TxD, pin 51

RxD RxD, pin 66 RxD, pin 53

Module

3 MASTER RESET MASTER RESET, pin 19 nRST, pin 74

control

SOFT RESET HARD RESET, pin 46 nSWRST, pin 67

READY CTS, pin 20 nREADY, pin 61

ALARM, pin 31 or nFAULT, pin

ALARM WDERR, pin 24

Table A.3 – Supply voltages and currents

Supply voltage and current A Supply voltage and current B

No Parameter Unit

Min. Typ. Max. Min. Typ. Max.

1 Supply voltage +3,3 V +3,14 +3,3 +3,5 NA NA NA V

2 Supply voltage +5,0 V +4,75 +5,0 +5,25 +4,75 +5,0 +5,6 V

Supply voltage

3 +4,75 +5,0 +5,25 +4,75 +5,0 +5,6 V

+5,0 V-Analog

Supply voltage

4 NA NA NA V

+14,25 +15,0 +15,75

+15,0 V-Analog

Supply voltage

5 -15,75 -15,0 -14,25 NA NA NA V

-15,0 V-Analog

6 Supply current +3,3 V NA NA +3,0 NA NA NA A

7 NA NA NA NA A

Supply current +5,0 V +2,0 +7,0

Supply current

8 NA NA NA NA NA A

+2,0

+5,0 V-Analog

Supply current

9 NA NA +1,0 NA NA NA A

+15,0 V-Analog

Supply current

10 NA NA 1,0 NA NA NA A

-15,0 V-Analog

All the WSS control signals are LVTTL CMOS (3,3 V). The voltage level thresholds are as

specified in Table A.4 below.

Table A.4 – Low voltage TTL thresholds

Low voltage TTL thresholds A Low voltage TTL thresholds B

No Parameter Unit

Min. Max. Min. Max.

1 Logic low input level NA -0,2 V

+0,8 +0,8

2 Logic high input level +2,0 +5,5 +2,0 +3,45 V

3 Logic low output level NA +0,4 NA +0,4 V

4 Logic high output level +2,4 +3,3 +2,8 NA V

Table A.5 – Power consumption

Power

Power consumption B

consumption A

No Parameter Unit

Max. Max.

Power

a

1 10 33 W

consumption

a

Including warm-up.

– 14 – IEC 62343-4-1:2016 © IEC 2016

Annex B

(informative)

DPRAM memory map details and timing charts

Annex B describes two types of DPRAM interfaces. All specifications in Annex B are

informative. It is recommended that the user chooses either specification A or B. Table B.1

provides the DPRAM memory map for specification A. Table B.2 provides the DPRAM

memory map for specification B. Table B.3 provides the signal time specification for both the

A and B interfaces. Figure B.1 through to Figure B.8 show the timing relationships of the

signals.

Table B.1 – DPRAM memory map specification A

Address Content (16 bits) Direction Note

From WSS The hardware and firmware

0x0001 Hardware and firmware version

module versions are embedded.

0x0020 Command register From host

controller

0x0021 Command code register

0x0022 Command data 1

From WSS Indicates command execution

0x0023 Status 1

module status, ready or error

Status code (contains results of

0x0024 Status 2

executed command)

0x0025 Error code

Temperature of WSS. This

0x0028 WSS module temperature address will be updated upon

receiving any command.

0x0029 Hardware failure register

0x0034 Command data 2 From host

controller

0x0035 Command data 3

Required port and differential From host Attenuation spectrum and port

Starting at 0x200

attenuation for each channel controller settings required

Port setting and accumulated differential From WSS Port settings and running sum of

Starting at 0x400

attenuations for each channel module differential attenuation

Stored port and accumulated From WSS Every time "store" command is

Starting at 0x600 attenuations for each channel read from module issued, the stored value is also

non-volatile RAM copied at 0x600

0x0803 Attenuation range (controllable range) The default stored value is 20 dB.

From WSS

Starting at 0x900 Wavelength of each channel Channel wavelength information

module

0x0F00- From host

User's reserved Confirmation module access

0x0FFF controller

Table B.2 – DPRAM memory map specification B

Initial

Address Content R/W Data type Note

value

Device identification and version information registers

Assigned by customer (constant

0x0000 Supplier identifier RO Number Invariant

compiled into the code-base)

This is a reduced detail version of the

0x0001 Version number RO Number Invariant version number. It includes both

hardware and software versions.

Assigned by customer (constant

0x0002 Part identifier RO Number Invariant

compiled into the code-base)

Version

Hardware version Stored in NVRAM in the device, non

0x0003 RO (high 16 Invariant

high customer configurable

bits)

Version (low Stored in NVRAM in the device, non

0x0004 Hardware version low RO Invariant

16 bits) customer configurable

Version

Constant compiled into boot-loader code

0x0005 FPGA version high RO (high 16 Invariant

base (within FPGA configuration)

bits)

Version (low Constant compiled into boot-loader code

0x0006 FPGA version low RO Invariant

16 bits) base (within FPGA configuration)

Loaded

Version

Firmware version whenever Constant compiled into the code base

0x0007 RO (high 16

high code is and embedded in the file header

bits)

restarted

Loaded

Version (low whenever Constant compiled into the code base

0x0008 Firmware version low RO

16 bits) code is and embedded in the file header

restarted

Version

Boot-loader version Constant compiled into boot-loader code

0x0009 RO (high 16 Invariant

high base (within FPGA configuration)

bits)

Boot-loader version Version (low Constant compiled into boot-loader code

0x000A RO Invariant

low 16 bits) base (within FPGA configuration)

Loaded

Version Constant embedded in NVRAM,

whenever

0x000B NVRAM version high RO (high 16 compiled into the code base and

code is

bits) embedded in the file header

restarted

Loaded

Constant embedded in NVRAM,

Version (low whenever

0x000C NVRAM version low RO compiled into the code base and

16 bits) code is

embedded in the file header

restarted

Loaded

Version Constant embedded in NVRAM,

whenever

0x000D CAL version high RO (high 16 compiled into the code base and

code is

bits) embedded in the file header

restarted

Loaded

Constant embedded in NVRAM,

Version (low whenever

0x000E CAL version high RO compiled into the code base and

16 bits) code is

embedded in the file header

restarted

Version

Integer portion of the serial number

0x000F Serial number high RO (high 16 Invariant

(upper 16 bits); stored in NVRAM

bits)

Version (low Integer portion of the serial number

0x0010 Serial number low RO Invariant

16 bits) (lower 16 bits); stored in NVRAM

Number

Year of manufacture as an integer;

0x0011 Year of manufacture RO (2003 to Invariant

stored within calibration data

65536)

Number Month of manufacture as an integer;

0x0012 Month of manufacture RO Invariant

(1 to 12) stored within calibration data

– 16 – IEC 62343-4-1:2016 © IEC 2016

Initial

Address Content R/W Data type Note

value

Number Day of manufacture as an integer;

0x0013 Day of manufacture RO Invariant

(1 to 31) stored within calibration data

This is the location of the currently

First valid

executing code within the device. The

Number code

0x0014 Current file location RO value location is 3 for the primary code

(0 to 2) found

version, 4 for the secondary code

(3 to 5)

version or 5 for the third code version.

0x0015-

Reserved NA NA NA Reserved

0x001F

Command control and status reporting registers

0x0020 Command register RW NA NA

Command code

0x0021 RW NA NA

register

Command data 1

0x0022

RW NA NA

register

0x0023 Status register RW NA NA

0x0024 Reserved RW NA NA

0x0025 Error code register RW NA NA

ALMHI case Stored

0x0026 RO

temperature duplicate value

± 0,1 ºC: i.e.

ALMLO case 10 ºC = 100 Stored

0x0027 RO

temperature duplicate and -0,4 ºC value

= 0xFFFC

Current case 0x7FFF

0x0028 RO

temperature duplicate (unread)

Hardware error

0x0029 RO Bit field 0x0000

register

0x002A Alarm register high RO Bit field 0x0000

0x002B Alarm register low RO Bit field NA

Hardware error Stored

0x002C RO Bit field

register latched value

Alarm register Stored

0x002D RO Bit field

latched high value

Alarm register Stored

0x002E RO Bit field

latched low value

0x002F Reserved NA NA NA

Number

Download binary file Size of the file being transferred (upper

0x0030 RW (Upper 16 0x0000

size(upper16) 16 bits)

bits)

Number

Download binary file Size of the file being transferred (lower

0x0031 RW (Lower 16 0x0000

size(lower16) 16 bits)

bits)

Download buffer Offset of the download buffer from the

0x0032 RO Number 0x0A00

offset start of the DRPAM

Size within the DRPAM of the download

0x0033 Download buffer size RO Number 0x0400

buffer

Command data 2

0x0034 RW NA 0x0000

register

Command data 3

0x0035 RW NA 0x0000

register

Command data 4

0x0036 RW NA 0x0000

register

Basic configuration registers

Initial

Address Content R/W Data type Note

value

The currently stored start-up

configuration. This controls the

behaviour of the device on a warm start.

0x0037 Start-up state RO Number (1 to 3) Possible values are:

1 Start factory default

2 Start all blocked

3 Start last saved

The module's channel spacing in GHz

0x0038 Channel spacing RO Number 50

(stored status)

0x0039-

Reserved NA NA NA Reserved

0x003F

0x0040- Reserved for

NA NA 0x7FFF Reserved for insertion loss data

0x0049 insertion loss data

0x004A-

Reserved NA NA NA Reserved for port expansion

0x004F

File download registers

Number

0x0050 Overall file size high RO (high 16 0x0000

bits)

Number (low

0x0051 Overall file size low RO 0x0000

16 bits)

Number

Current block offset

0x0052 RO (high 16 0x0000

high

bits)

Current block offset Number (low

0x0053 RO 0x0000

low 16 bits)

0x0054 Current block length RO Number 0x0000

Number

Current block CRC

0x0055 RO (high 16 0x0000

high

bits)

Current block CRC Number (low

0x0056 RO 0x0000

low 16 bits)

Number

0x0057 Overall file CRC high RO (high 16 0x0000

bits)

Number (low

0x0058 Overall file CRC low RO 0x0000

16 bits)

0x0059 File validate status RO Bit field 0x0000

0x005A File save status RO Bit field 0x0000

Number

Hardware version –

0x005B RO (high 16 0x0000

file high

bits)

Hardware version – Number (low

0x005C RO 0x0000

file low 16 bits)

Number

FPGA version – file

0x005D RO (high 16 0x0000

high

bits)

FPGA version – file Number (low

0x005E RO 0x0000

low 16 bits)

Number

Firmware version –

0x005F RO (high 16 0x0000

file high

bits)

Firmware version – Number (low

0x0060 RO 0x0000

file low 16 bits)

Number

Boot-loader version –

0x0061 RO (high 16 0x0000

file high

bits)

– 18 – IEC 62343-4-1:2016 © IEC 2016

Initial

Address Content R/W Data type Note

value

Boot-loader version – Number (low

0x0062 RO 0x0000

file low 16 bits)

Number

NVRAM version – file

0x0063

RO (high 16 0x0000

high

bits)

NVRAM version – file Number (low

0x0064 RO 0x0000

low 16 bits)

Number

CAL version – file

0x0065 RO (high 16 0x0000

high

bits)

Number (low

0x0066 CAL version – file low RO 0x0000

16 bits)

0x0067-

Reserved NA NA NA Reserved

0x01FF

Port and attenuation configuration registers

One 16-bit word per channel; upper byte

is the port; lower byte is the attenuation.

The port is a number from 1 to the

number of ports in the device.

As Attenuation is a number from 0 to 150

Array of one specified and is measured in 0,1 dB increments. If

0x0200- Required port and

RW hundred by the the port or the attenuation is set to

0x0263 attenuation

16-bit values "start-up 0xFF, the channel will be blocked. The

state" first channel is stored in the first

memory location. This array is used to

determine which channels are to be

updated when a switch command is

received.

0x0264-

Reserved NA NA NA Reserved for channel expansion

0x02FF

One 16-bit word per channel; upper byte

is the port; lower byte is the attenuation.

The port is a number from 1 to the

As number of ports in the device.

specified Attenuation is a number from 0 to 150

0x0300- Current port and

RO NA by the and is measured in 0,1 dB increments. If

0x0363 attenuation

"start-up the port or the attenuation is set to

state" 0xFF, the channel will be blocked. The

first channel is stored in the first

memory location. This array represents

the current configuration of the switch.

0x0364-

Reserved NA NA NA Reserved for channel expansion

0x03FF

One 16-bit word per channel; upper byte

is the port; lower byte is the attenuation.

The port is a number from 1 to the

As number of ports in the device.

specified Attenuation is a number from 0 to 150

0x0400 Stored port and

RO NA by the and is measured in 0,1 dB increments. If

0x0463 attenuation

"start-up the port or the attenuation is set to

state" 0xFF, the channel will be blocked. The

first channel is stored in the first

memory location. This array represents

the current configuration of the switch.

0x0464-

Reserved NA NA NA Reserved for channel expansion

0x04FF

Reserved space

0x0500-

Reserved NA NA NA Reserved

0x09FF

File transfer buffer

Initial

Address Content R/W Data type Note

value

If the size in bytes of the block in the

0x0A00-

Download buffer RW NA NA buffer is odd, the last byte will be in the

0x0DFF

upper byte of the last used 16-bit word.

Manufacturer specific diagnostics

0x0E00- Manufacturer

NA NA NA Reserved for manufacturer diagnostics

0x0EFF diagnostics

Monitored signal and alarm configuration registers

This is the It is an instantaneous

Current case 0x7FFF current case sample that is

0x0F00 RO

temperature (unread) temperature of updated once every

the module 10 s. It is a signed

value measured in

steps of 0,1 ºC. The

± 0,1 ºC: i.e.

accuracy of this

10 ºC = 100

value is not

and

This is the

guaranteed, and it is

-0,4 ºC =

current

not calibrated.

Current device 0x7FFF

0xFFFC

0x0F01 RO temperature of

temperature (unread)

the optical The value 0x7FFF or

package 32768 indicates that

the rail has not been

sampled yet or is not

being sampled.

The number of

This is an

mA being used

0x7FFF

instantaneous

0x0F02 TEC current RO ± mA by the

(unread)

sample that is

temperature

updated once every

controller

10 s. The value

This is the

0x7FFF or 32768

current (5 V)

indicates that the rail

0x7FFF supply voltage

has not been

0x0F03 Supply voltage (5V) RO ± mV

(unread) of the DWP

sampled yet or is not

device

being sampled.

measured in mV

Internal power rail 0x7FFF

0x0F04 RO ± mV

13v4 (unread)

Internal power rail 0x7FFF

0x0F05 RO ± mV

12v4 (unread)

Internal power rail 0x7FFF

These are internally generated power

0x0F06 RO ± mV

3v3 (unread)

rails on the DWP device.

Internal power rail 0x7FFF

They are instantaneous samples that

0x0F07 RO ± mV

2v5 (unread)

are updated once every 10 s. They are

signed values measured in mV.

Internal power rail 0x7FFF

0x0F08 RO ± mV

1v8 (unread)

The value 0x7FFF or 32768 indicates

that the rail has not been sampled yet or

Internal power rail 0x7FFF

0x0F09 RO

± mV is not being sampled.

1v5 (unread)

Internal power rail 0x7FFF

0x0F0A RO

± mV

N2V (unread)

Internal power rail 0x7FFF

0x0F0B RO

± mV

N5V (unread)

0x0F0C- Reserved for expansion of monitoring

Reserved NA NA NA

0x0F1F options

ALMHI case Stored This is the level at which an alarm will

0x0F20 RO ± 0,1 ºC

temperature value be reported.

ALMHI device Stored It is directly compared against the

0x0F21 RO ± 0,1 ºC

corresponding monitored signal.

temperature value

A value of 0x7FFF indicates to the

Stored

0x0F22 ALMHI TEC current RO ± mA

value device that the alarm will be ignored.

Stored

0x0F23 ALMHI supply voltage RO ± mV

value

– 20 – IEC 62343-4-1:2016 © IEC 2016

Initial

Address Content R/W Data type Note

value

ALMHI internal rail Stored

0x0F24 RO ± mV

13v4 value

ALMHI internal power Stored

0x0F25 RO ± mV

12v4 value

ALMHI internal power Stored

0x0F26 RO ± mV

3v3 value

ALMHI internal power Stored

0x0F27 RO ± mV

2v5 value

ALMHI internal power Stored

0x0F28 RO ± mV

1v8 value

ALMHI internal power Stored

0x0F29 RO

± mV

1v5 value

ALMHI internal power Stored

0x0F2A RO

± mV

N2V value

ALMHI internal power Stored

0x0F2B RO

± mV

N5V value

Stored

0x0F2C ALMHI VCOM RO ± mV

value

This is the upper limit of the temperature

range of the device.

ALMHI temperature Stored At or above this limit the device will shut

0x0F2D RO

± 0,1 ºC

shutdown value down the optional components.

A value of 0x7FFF indicates to the

device that the alarm will be ignored.

These are secondary alarms; if triggered

the alarm events are recorded and it is

ALMHI TEC current Stored

not possible to clear them.

0x0F2E RO

± mA

OOR value

A value of 0x7FFF indicates to the

device that the alarm will be ignored.

ALMHI supply voltage Stored

0x0F2F RO

± mV

OOR value

Stored

0x0F30 ALMHI VCOM OOR RO ± mV

value

0x0F31- Reserved for expansion of monitoring

Reserved NA NA NA

0x0F3F options

ALMHI hysteresis Stored After the alarm has triggered because it

0x0F40 RO ± 0,1 ºC

case temperature value is above the high threshold, it will

remain active until it drops back below

ALMHI hysteresis Stored

this threshold.

0x0F41 RO ± 0,1 ºC

device temperature value

A value of 0x7FFF indicates to the

ALMHI hysteresis Stored

device that the hysteresis level is

0x0F42 RO ± mA

TEC current value

ignored and that the alarm will be

cleared as soon as the signal drops

ALMHI hysteresis Stored

0x0F43 RO ± mV below the high threshold.

supply voltage (5V) value

("Temperature Shutdown", "TEC Current

ALMHI hysteresis Stored

0x0F44 RO OOR", "Supply OOR" and "VCOM OOR"

± mV

internal rail 13v4 value

are special cases as they are duplicates

and compare against other values.)

ALMHI hysteresis Stored

0x0F45 RO

± mV

internal power 12v4 value

ALMHI hysteresis Stored

0x0F46 RO

± mV

internal power 3v3 value

ALMHI hysteresis Stored

0x0F47 RO

± mV

internal power 2v5 value

ALMHI hysteresis Stored

0x0F48 RO ± mV

internal power 1v8 value

ALMHI hysteresis Stored

0x0F49 RO ± mV

internal power 1v5 value

Initial

Address Content R/W Data type Note

value

ALMHI hysteresis Stored

0x0F4A RO ± mV

internal power N2V value

ALMHI hysteresis Stored

0x0F4B RO ± mV

internal power N5V value

ALMHI hysteresis Stored

0x0F4C RO ± mV

VCOM value

ALMHI hysteresis

Stored

0x0F4D temperature RO

± 0,1 ºC

value

shutdown

ALMHI hysteresis Stored

0x0F4E RO ± mA

TEC current OOR value

ALMHI hysteresis Stored

0x0F4F RO ± mV

supply OOR value

Stored

0x0F50 ALMHI VCOM OOR RO

± mV

value

0x0F51- Reserved for expansion of monitoring

Reserved NA NA NA

0x0F5F options

ALMLO case Stored This is the level at or below which an

0x0F60 RO

± 0,1 ºC

temperature value alarm will be reported.

It is directly compared against the

ALMLO device Stored

0x0F61 RO

± 0,1 ºC

corresponding monitored signal.

temperature value

A value of 0x7FFF indicates to the

ALMLO TEC Stored

0x0F62 RO ± mA

device that the alarm will be ignored.

temperature value

ALMLO supply Stored

0x0F63 RO ± mV

voltage (5V) value

ALMLO internal rail Stored

0x0F64 RO ± mV

13v4 value

ALMLO internal Stored

0x0F65 RO ± mV

power 12v4 value

ALMLO internal Stored

0x0F66 RO ± mV

power 3v3 value

ALMLO internal Stored

0x0F67 RO ± mV

power 2v5 value

ALMLO internal Stored

0x0F68 RO

± mV

power 1v8 value

ALMLO internal Stored

0x0F69 RO

± mV

power 1v5

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...