IEC 62271-101:2006

(Main)High-voltage switchgear and controlgear - Part 101: Synthetic testing

High-voltage switchgear and controlgear - Part 101: Synthetic testing

This part of IEC 62271 mainly applies to a.c. circuit-breakers within the scope of IEC 62271-100. It provides the general rules for testing a.c. circuit-breakers, for making and breaking capacities over the range of test duties described in 6.102 to 6.111 of IEC 62271-100, by synthetic methods.

This publication is to be read in conjunction with IEC 62271-100:2008.

Appareillage à haute tension - Partie 101: Essais synthétiques

La présente partie de la CEI 62271 s'applique principalement aux disjoncteurs à courant alternatif définis dans le domaine d'application de la CEI 62271-100. Elle donne les règles générales d'essais de ces disjoncteurs, pour les pouvoirs de fermeture et de coupure dans la gamme des séquences d'essais décrites de 6.102 à 6.111 de la CEI 62271-100, à l'aide de méthodes d'essais synthétiques.

Cette publication doit être lue conjointement avec la CEI 62271-100:2008.

General Information

- Status

- Published

- Publication Date

- 28-Nov-2010

- Technical Committee

- SC 17A - Switching devices

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 12-Oct-2012

- Completion Date

- 14-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 62271-101:2006 is an international standard published by the International Electrotechnical Commission (IEC) that specifies the rules and methodologies for the synthetic testing of high-voltage switchgear and controlgear, specifically focusing on a.c. circuit-breakers as outlined in IEC 62271-100. Synthetic testing is a vital procedure for verifying the making and breaking capacities of a.c. circuit-breakers under controlled conditions that simulate real-life operating scenarios. The standard defines general requirements, techniques, and criteria to ensure that synthetic tests reliably replicate the performance and safety attributes required for high-voltage equipment.

Key Topics

- Scope and Purpose: This standard applies primarily to a.c. circuit-breakers tested for making and breaking capabilities through synthetic methods, covering a wide range of test duties in alignment with IEC 62271-100.

- Synthetic Testing Principles: Provides detailed descriptions regarding:

- Types of tests: distinguishing between direct tests (using a single power source) and synthetic tests (utilizing separate sources for current and voltage).

- Definitions and roles of current circuits, voltage circuits, test circuit-breakers, and auxiliary circuit-breakers within test systems.

- Test Techniques: Covers major synthetic test methods including:

- Current-injection and voltage-injection approaches.

- Three-phase synthetic testing techniques for more complex validation.

- Specific requirements for testing making and breaking performances.

- Criteria and Evaluation: Establishes parameters for evaluating the validity of test methods without constraining innovation while defining essential criteria for repeatable, accurate, and standardized reporting of test results.

- Annexes for Additional Guidance: Includes informative and normative annexes with detail on current and voltage distortion, test circuits, procedures for special circuit-breaker configurations, and further technical considerations.

Applications

The IEC 62271-101:2006 standard is widely used by the following professionals and organizations:

- Manufacturers of High-voltage Circuit-breakers: To demonstrate that products meet international safety and performance requirements through proven synthetic testing methods.

- Testing Laboratories: For setting up accurate and compliant test circuits that replicate system conditions for product type testing and certification.

- Utilities and Asset Owners: When specifying technical requirements in procurement to ensure new equipment meets rigorous synthetic test criteria.

- Engineers and System Integrators: To design, select, and validate high-voltage switchgear in substations or grids, ensuring reliability and safety under fault conditions.

By following the guidelines in IEC 62271-101, stakeholders ensure that high-voltage circuit-breakers are validated in conditions that closely mimic possible service scenarios, supporting both safety and performance across national and international power networks.

Related Standards

Several standards complement IEC 62271-101 and are frequently referenced together in the context of high-voltage equipment testing and certification:

- IEC 62271-100: High-voltage switchgear and controlgear - Part 100: High-voltage alternating current circuit-breakers (core test requirements for circuit-breakers, to be read in conjunction with Part 101).

- IEC 61633: Guide for short-circuit and switching test procedures.

- IEC 62271-308: Guide for asymmetrical short-circuit test duty T100a.

Adherence to these standards collectively ensures a unified approach to the type testing and performance verification of high-voltage switchgear and controlgear, contributing to grid stability and international equipment compatibility.

By aligning with IEC 62271-101:2006, organizations contribute to safer, more reliable, and standardized electrical infrastructure on a global scale. This standard is fundamental for anyone involved in the design, testing, and deployment of high-voltage circuit-breakers and related controlgear.

Buy Documents

IEC 62271-101:2006 - High-voltage switchgear and controlgear - Part 101: Synthetic testing Released:5/23/2006

IEC 62271-101:2006+AMD1:2010 CSV - High-voltage switchgear and controlgear - Part 101: Synthetic testing Released:11/29/2010

Get Certified

Connect with accredited certification bodies for this standard

IMQ S.p.A. (Certification)

Italian electrical product certification.

SLG Prüf- und Zertifizierungs GmbH

German testing and certification body.

UL Solutions

Global safety science company with testing, inspection and certification.

Sponsored listings

Frequently Asked Questions

IEC 62271-101:2006 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "High-voltage switchgear and controlgear - Part 101: Synthetic testing". This standard covers: This part of IEC 62271 mainly applies to a.c. circuit-breakers within the scope of IEC 62271-100. It provides the general rules for testing a.c. circuit-breakers, for making and breaking capacities over the range of test duties described in 6.102 to 6.111 of IEC 62271-100, by synthetic methods. This publication is to be read in conjunction with IEC 62271-100:2008.

This part of IEC 62271 mainly applies to a.c. circuit-breakers within the scope of IEC 62271-100. It provides the general rules for testing a.c. circuit-breakers, for making and breaking capacities over the range of test duties described in 6.102 to 6.111 of IEC 62271-100, by synthetic methods. This publication is to be read in conjunction with IEC 62271-100:2008.

IEC 62271-101:2006 is classified under the following ICS (International Classification for Standards) categories: 29.130.10 - High voltage switchgear and controlgear. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62271-101:2006 has the following relationships with other standards: It is inter standard links to IEC 60427:2000, IEC 62271-101:2006/AMD1:2010, IEC 62271-101:2012. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 62271-101:2006 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE

IEC

62271-101

INTERNATIONAL

Première édition

STANDARD

First edition

2006-05

Appareillage à haute tension –

Partie 101:

Essais synthétiques

High-voltage switchgear and controlgear –

Part 101:

Synthetic testing

Numéro de référence

Reference number

CEI/IEC 62271-101:2006

Numérotation des publications Publication numbering

Depuis le 1er janvier 1997, les publications de la CEI As from 1 January 1997 all IEC publications are

sont numérotées à partir de 60000. Ainsi, la CEI 34-1 issued with a designation in the 60000 series. For

devient la CEI 60034-1. example, IEC 34-1 is now referred to as IEC 60034-1.

Editions consolidées Consolidated editions

Les versions consolidées de certaines publications de la The IEC is now publishing consolidated versions of its

CEI incorporant les amendements sont disponibles. Par publications. For example, edition numbers 1.0, 1.1

exemple, les numéros d’édition 1.0, 1.1 et 1.2 indiquent and 1.2 refer, respectively, to the base publication,

respectivement la publication de base, la publication de the base publication incorporating amendment 1 and

base incorporant l’amendement 1, et la publication de the base publication incorporating amendments 1

base incorporant les amendements 1 et 2. and 2.

Informations supplémentaires Further information on IEC publications

sur les publications de la CEI

Le contenu technique des publications de la CEI est The technical content of IEC publications is kept

constamment revu par la CEI afin qu'il reflète l'état under constant review by the IEC, thus ensuring that

actuel de la technique. Des renseignements relatifs à the content reflects current technology. Information

cette publication, y compris sa validité, sont dispo- relating to this publication, including its validity, is

nibles dans le Catalogue des publications de la CEI available in the IEC Catalogue of publications

(voir ci-dessous) en plus des nouvelles éditions, (see below) in addition to new editions, amendments

amendements et corrigenda. Des informations sur les and corrigenda. Information on the subjects under

sujets à l’étude et l’avancement des travaux entrepris consideration and work in progress undertaken by the

par le comité d’études qui a élaboré cette publication, technical committee which has prepared this

ainsi que la liste des publications parues, sont publication, as well as the list of publications issued,

également disponibles par l’intermédiaire de: is also available from the following:

• Site web de la CEI (www.iec.ch) • IEC Web Site (www.iec.ch)

• Catalogue des publications de la CEI • Catalogue of IEC publications

Le catalogue en ligne sur le site web de la CEI The on-line catalogue on the IEC web site

(www.iec.ch/searchpub) vous permet de faire des (www.iec.ch/searchpub) enables you to search by a

recherches en utilisant de nombreux critères, variety of criteria including text searches,

comprenant des recherches textuelles, par comité technical committees and date of publication. On-

d’études ou date de publication. Des informations en line information is also available on recently

ligne sont également disponibles sur les nouvelles issued publications, withdrawn and replaced

publications, les publications remplacées ou retirées, publications, as well as corrigenda.

ainsi que sur les corrigenda.

• IEC Just Published • IEC Just Published

Ce résumé des dernières publications parues This summary of recently issued publications

(www.iec.ch/online_news/justpub) est aussi dispo- (www.iec.ch/online_news/justpub) is also available

nible par courrier électronique. Veuillez prendre by email. Please contact the Customer Service

contact avec le Service client (voir ci-dessous) Centre (see below) for further information.

pour plus d’informations.

• Service clients • Customer Service Centre

Si vous avez des questions au sujet de cette If you have any questions regarding this

publication ou avez besoin de renseignements publication or need further assistance, please

supplémentaires, prenez contact avec le Service contact the Customer Service Centre:

clients:

Email: custserv@iec.ch Email: custserv@iec.ch

Tél: +41 22 919 02 11 Tel: +41 22 919 02 11

Fax: +41 22 919 03 00 Fax: +41 22 919 03 00

.

NORME CEI

INTERNATIONALE

IEC

62271-101

INTERNATIONAL

Première édition

STANDARD

First edition

2006-05

Appareillage à haute tension –

Partie 101:

Essais synthétiques

High-voltage switchgear and controlgear –

Part 101:

Synthetic testing

IEC 2006 Droits de reproduction réservés Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni No part of this publication may be reproduced or utilized in any

utilisée sous quelque forme que ce soit et par aucun procédé, form or by any means, electronic or mechanical, including

électronique ou mécanique, y compris la photocopie et les photocopying and microfilm, without permission in writing from

microfilms, sans l'accord écrit de l'éditeur. the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

CODE PRIX

XG

PRICE CODE

Commission Electrotechnique Internationale

International Electrotechnical Commission

МеждународнаяЭлектротехническаяКомиссия

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 62271-101 CEI:2006

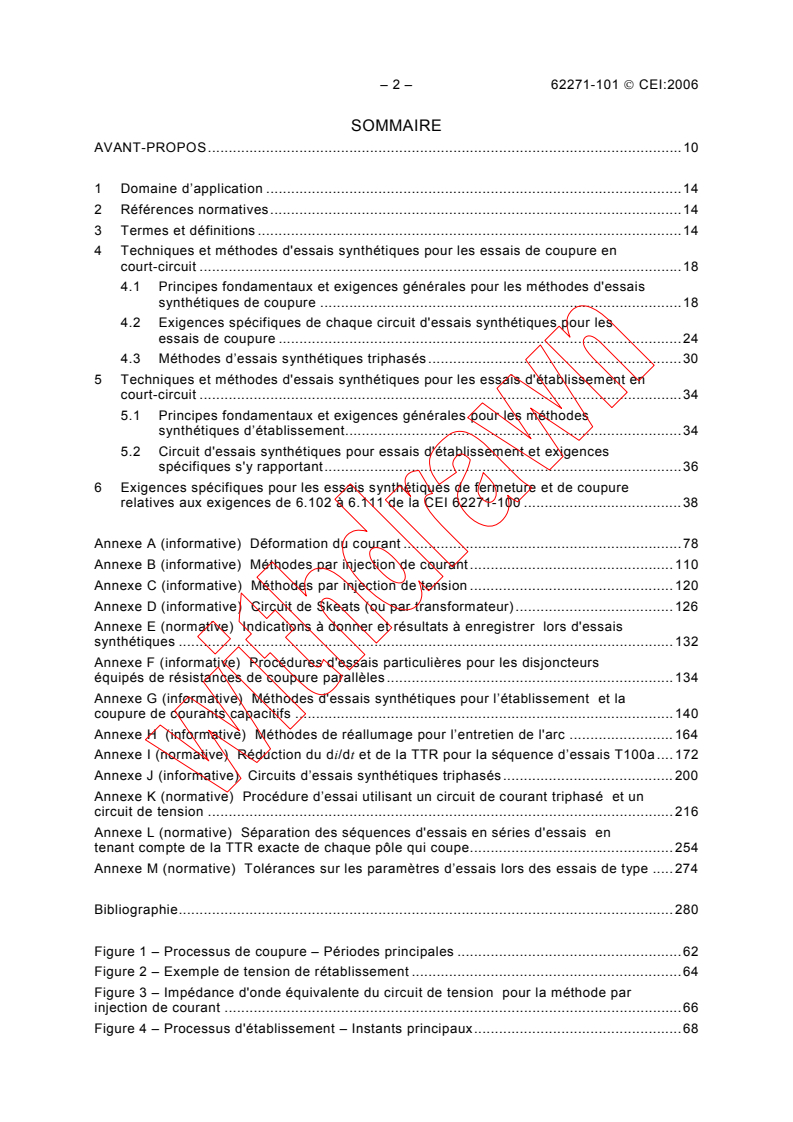

SOMMAIRE

AVANT-PROPOS.10

1 Domaine d’application .14

2 Références normatives.14

3 Termes et définitions .14

4 Techniques et méthodes d'essais synthétiques pour les essais de coupure en

court-circuit .18

4.1 Principes fondamentaux et exigences générales pour les méthodes d'essais

synthétiques de coupure .18

4.2 Exigences spécifiques de chaque circuit d'essais synthétiques pour les

essais de coupure .24

4.3 Méthodes d’essais synthétiques triphasés .30

5 Techniques et méthodes d'essais synthétiques pour les essais d'établissement en

court-circuit .34

5.1 Principes fondamentaux et exigences générales pour les méthodes

synthétiques d’établissement.34

5.2 Circuit d'essais synthétiques pour essais d'établissement et exigences

spécifiques s'y rapportant.36

6 Exigences spécifiques pour les essais synthétiques de fermeture et de coupure

relatives aux exigences de 6.102 à 6.111 de la CEI 62271-100 .38

Annexe A (informative) Déformation du courant .78

Annexe B (informative) Méthodes par injection de courant.110

Annexe C (informative) Méthodes par injection de tension .120

Annexe D (informative) Circuit de Skeats (ou par transformateur).126

Annexe E (normative) Indications à donner et résultats à enregistrer lors d'essais

synthétiques .132

Annexe F (informative) Procédures d'essais particulières pour les disjoncteurs

équipés de résistances de coupure parallèles.134

Annexe G (informative) Méthodes d'essais synthétiques pour l’établissement et la

coupure de courants capacitifs .140

Annexe H (informative) Méthodes de réallumage pour l’entretien de l'arc .164

Annexe I (normative) Réduction du di/dt et de la TTR pour la séquence d’essais T100a .172

Annexe J (informative) Circuits d’essais synthétiques triphasés.200

Annexe K (normative) Procédure d’essai utilisant un circuit de courant triphasé et un

circuit de tension .216

Annexe L (normative) Séparation des séquences d'essais en séries d'essais en

tenant compte de la TTR exacte de chaque pôle qui coupe.254

Annexe M (normative) Tolérances sur les paramètres d’essais lors des essais de type .274

Bibliographie.280

Figure 1 – Processus de coupure – Périodes principales .62

Figure 2 – Exemple de tension de rétablissement .64

Figure 3 – Impédance d'onde équivalente du circuit de tension pour la méthode par

injection de courant .66

Figure 4 – Processus d'établissement – Instants principaux.68

62271-101 IEC:2006 – 3 –

CONTENTS

FOREWORD.11

1 Scope.15

2 Normative references .15

3 Terms and definitions .15

4 Synthetic testing techniques and methods for short-circuit breaking tests.19

4.1 Basic principles and general requirements for synthetic breaking test

methods .19

4.2 Synthetic test circuits and related specific requirements for breaking tests .25

4.3 Three-phase synthetic test methods .31

5 Synthetic testing techniques and methods for short-circuit making tests .35

5.1 Basic principles and general requirements for synthetic making test methods .35

5.2 Synthetic test circuit and related specific requirements for making tests .37

6 Specific requirements for synthetic tests for making and breaking performance

related to the requirements of 6.102 through 6.111 of IEC 62271-100 .39

Annex A (informative) Current distortion .79

Annex B (informative) Current injection methods.111

Annex C (informative) Voltage injection methods .121

Annex D (informative) Duplicate circuit (transformer or Skeats circuit) .127

Annex E (normative) Information to be given and results to be recorded for synthetic tests . 133

Annex F (informative) Special procedures for testing circuit-breakers having parallel

breaking resistors .135

Annex G (informative) Synthetic methods for capacitive-current switching .141

Annex H (informative) Re-ignition methods to prolong arcing .165

Annex I (normative) Reduction in di/dt and TRV for test duty T100a .173

Annex J (informative) Three-phase synthetic test circuits.201

Annex K (normative) Test procedure using a three-phase current circuit and one

voltage circuit .217

Annex L (normative) Splitting of test duties in test series taking into account the

associated TRV for each pole-to-clear .255

Annex M (normative) Tolerances on test quantities for type tests.275

Bibliography.281

Figure 1 – Interrupting process – Basic time intervals .63

Figure 2 – Example of recovery voltage .65

Figure 3 – Equivalent surge impedance of the voltage circuit for the current injection

method .67

Figure 4 – Making process – Basic time intervals.69

– 4 – 62271-101 CEI:2006

Figure 5 – Circuit d’essais synthétiques de fermeture type pour les essais

monophasés .70

Figure 6 – Circuit type d’essais synthétiques d'établissement pour les essais triphasés

(k = 1,5) .72

pp

Figure 7 – Comparaison des réglages de la durée d’arc pendant les essais directs

triphasés (gauche) et les essais synthétiques triphasés (droite) pour T100s avec k =1,5 .74

p

Figure 8 – Comparaison des réglages de la durée d’arc pendant les essais directs

triphasés (gauche) et les essais synthétiques triphasés (droite) pour T100a avec k =1,5 .76

pp

Figure A.1 – Circuit direct, schéma simplifié .92

Figure A.2 – Courant de court-circuit présumé .92

Figure A.3 – Courant déformant.92

Figure A.4 – Courant déformant.94

Figure A.5 – Schéma de circuit simplifié .96

Figure A.6 – Caractéristiques du courant et de la tension d'arc pour courant

symétrique.98

Figure A.7 – Caractéristiques de courant et de tension d'arc pour courant asymétrique .100

Figure A.8 – Réduction de l'amplitude et de la durée de la dernière alternance d’arc

de courant .102

Figure A.9 – Réduction de l'amplitude et de la durée de la dernière alternance d’arc

de courant .104

Figure A.10 – Réduction de l'amplitude et de la durée de la dernière alternance d’arc

de courant .106

Figure A.11 – Réduction de l'amplitude et de la durée de la dernière alternance d’arc

de courant .108

Figure B.1 – Circuit type à injection de courant où la source de tension est en

parallèle avec le disjoncteur en essai.114

Figure B.2 – Séquence de l'injection du courant dans le circuit de la Figure B.1 .114

Figure B.3 – Circuit type à injection de courant où la source de tension est en

parallèle avec le disjoncteur auxiliaire.116

Figure B.4 – Séquence de l'injection du courant dans le circuit de la Figure B.3 .116

Figure B.5 – Exemples de détermination de la durée de changement significatif de la

tension d'arc à partir d'oscillogrammes .118

Figure C.1 – Schéma caractéristique de l'injection de tension avec la source de

tension en parallèle avec le disjoncteur auxiliaire (schéma simplifié) .122

Figure C.2 – Formes d'ondes de TTR obtenues dans un circuit à injection de tension

avec la source de tension en parallèle avec le disjoncteur auxiliaire .124

Figure D.1 – Circuit de Skeats ou par transformateur.128

Figure D.2 – Circuit de Skeats ou par transformateur déclenché.130

Figure G.1 – Circuits de courant capacitif (mode parallèle) .146

Figure G.2 – Circuit à injection de courant .148

Figure G.3 – Circuit oscillant LC .150

Figure G.4 – Source de courant inductive en parallèle avec le circuit oscillant LC.152

Figure G.5 – Circuit à injection de courant, tension de rétablissement normale

appliquée aux deux bornes du disjoncteur en essai .154

Figure G.6 – Circuit d’essais synthétiques (circuit série), tension de rétablissement

normale appliquée aux deux bornes du disjoncteur en essai.156

Figure G.7 – Circuit à injection de courant, tension de rétablissement appliquée aux

deux bornes du disjoncteur en essai .158

Figure G.8 – Circuit d’essai d’établissement .160

Figure G.9 – Circuit d'établissement du courant d'appel de fermeture .162

62271-101 IEC:2006 – 5 –

Figure 5 – Typical synthetic make circuit for single-phase tests .71

Figure 6 – Typical synthetic make circuit for three-phase tests (k = 1,5).73

pp

Figure 7 – Comparison of arcing time settings during three-phase direct tests (left)

and three-phase synthetic (right) for T100s with k = 1,5 .75

pp

Figure 8 – Comparison of arcing time settings during three-phase direct tests (left)

and three-phase synthetic (right) for T100a with k = 1,5.77

pp

Figure A.1 – Direct circuit, simplified diagram .93

Figure A.2 – Prospective short-circuit current .93

Figure A.3 – Distortion current .93

Figure A.4 – Distortion current .95

Figure A.5 – Simplified circuit diagram.97

Figure A.6 – Current and arc voltage characteristics for symmetrical current .99

Figure A.7 – Current and arc voltage characteristics for asymmetrical current .101

Figure A.8 – Reduction of amplitude and duration of final current loop of arcing .103

Figure A.9 – Reduction of amplitude and duration of final current loop of arcing .105

Figure A.10 – Reduction of amplitude and duration of final current loop of arcing .107

Figure A.11 – Reduction of amplitude and duration of final current loop of arcing .109

Figure B.1 – Typical current injection circuit with voltage circuit in parallel with the test

circuit-breaker.115

Figure B.2 – Injection timing for current injection scheme with circuit B.1.115

Figure B.3 – Typical current injection circuit with voltage circuit in parallel with the

auxiliary circuit-breaker.117

Figure B.4 – Injection timing for current injection scheme with circuit B.3.117

Figure B.5 – Examples of the determination of the interval of significant change of arc

voltage from the oscillograms .119

Figure C.1 – Typical voltage injection circuit diagram with voltage circuit in parallel

with the auxiliary circuit-breaker (simplified diagram) .123

Figure C.2 – TRV waveshapes in a voltage injection circuit with the voltage circuit in

parallel with the auxiliary circuit-breaker .125

Figure D.1 – Transformer or Skeats circuit.129

Figure D.2 – Triggered transformer or Skeats circuit .131

Figure G.1 – Capacitive current circuits (parallel mode) .147

Figure G.2 – Current injection circuit.149

Figure G.3 – LC oscillating circuit .151

Figure G.4 – Inductive current circuit in parallel with LC oscillating circuit.153

Figure G.5 – Current injection circuit, normal recovery voltage applied to both

terminals of the circuit-breaker.155

Figure G.6 – Synthetic test circuit (series circuit), normal recovery voltage applied to

both sides of the test circuit breaker .157

Figure G.7 – Current injection circuit, recovery voltage applied to both sides of the

circuit-breaker.159

Figure G.8 – Making test circuit .161

Figure G.9 – Inrush making current test circuit.163

– 6 – 62271-101 CEI:2006

Figure H.1 – Schéma type du circuit de réallumage servant à prolonger la durée d'arc .166

Figure H.2 – Circuits combinés à injection de courant et de Skeats .168

Figure H.3 – Formes d'ondes typiques obtenues pendant un essai asymétrique en

utilisant le circuit de la Figure H.2.170

Figure J.1a – Circuit combiné d’essais synthétiques triphasés .204

Figure J.1b – Formes d’ondes de courants, tensions phase-terre et entre phases

pendant un essai synthétique triphasé (T100s; k = 1,5) réalisé conformément au

pp

circuit combiné d’essais synthétiques triphasés .206

Figure J.2a – Circuit d’essais synthétiques triphasés avec injection dans toutes les

phases pour k = 1,5 .208

pp

Figure J.2b – Formes d’ondes de courants et tensions phase-terre pendant un essai

synthétique triphasé (T100s; k =1,5) réalisé conformément au circuit d’essais

pp

synthétiques triphasés avec injection dans toutes les phases .210

Figure J.3a – Circuit d’essais synthétiques triphasés pour les essais de défauts aux

bornes avec k = 1,3 (méthode par injection de courant) .212

pp

Figure J.3b – Formes d’ondes de courants, tensions phase-terre et entre phases

pendant un essai synthétique triphasé (T100s; k =1,3 ) réalisé conformément au

pp

circuit d’essais synthétiques triphasés représenté à la Figure J.3a .212

Figure J.3c – Formes d’ondes de la TTR du circuit d’essai décrit à la Figure J.3a.214

Figure K.1 – Exemple d’une source de courant triphasée avec une injection

synthétique monophasée .236

Figure K.2 – Représentation des conditions d’essais du Tableau K.1a.238

Figure K.3 – Représentation des conditions d’essais du Tableau K.1b.240

Figure K.4 – Représentation des conditions d’essais du Tableau K.2a.242

Figure K.5 – Représentation des conditions d’essais du Tableau K.2b.244

Figure K.6 – Représentation des conditions d’essais du Tableau K.3a.246

Figure K.8 – Représentation des conditions d’essais du Tableau K.4a.250

Figure K.9 – Représentation des conditions d’essais du Tableau K.4b.252

Figure L.1 – Représentation graphique de l’essai représenté au Tableau L.1.266

Figure L.2 – Représentation graphique de l’essai représenté au Tableau L.2.268

Tableau 1 – Circuits d’essais pour les séquences d’essais T100s et T100a .30

Tableau 2 – Séquences d’essais T10, T30, T60 et T100s .32

Tableau 2a – Facteur de premier pôle: 1,5 – Paramètres d’essais pendant la coupure

triphasée .32

Tableau 2b – Facteur de premier pôle: 1,3 – Paramètres d’essais pendant la coupure

triphasée .32

Tableau 3 – Méthodes d’essais synthétiques pour les séquences d’essais T10, T30,

T60, T100s, T100a, SP, DEF, OP et SLF .58

Tableau I.1a – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 50Hz τ = 45 ms.174

Tableau I.1b – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 50Hz τ = 60 ms.176

Tableau I.1c – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 50Hz τ = 75 ms.178

Tableau I.1d – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 50 Hz τ = 120 ms.180

62271-101 IEC:2006 – 7 –

Figure H.1 – Typical re-ignition circuit diagram for prolonging arc-duration .167

Figure H.2 – Combined Skeats and current injection circuits.169

Figure H.3 – Typical waveforms obtained during an asymmetrical test using the circuit

in Figure H.2.171

Figure J.1a – Three-phase synthetic combined circuit.205

Figure J.1b – Waveshapes of currents, phase-to-ground and phase-to phase voltages

during a three-phase synthetic test (T100s; k = 1,5 ) performed according to the

pp

three-phase synthetic combined circuit .207

Figure J.2a – Three-phase synthetic circuit with injection in all phases for k = 1,5 .209

pp

Figure J.2b – Waveshapes of currents and phase-to-ground voltages during a three-

phase synthetic test (T100s; k =1,5) performed according to the three-phase

pp

synthetic circuit with injection in all phases .211

Figure J.3a – Three-phase synthetic circuit for terminal fault tests with k = 1,3

pp

(current injection method) .213

Figure J.3b – Waveshapes of currents, phase-to-ground and phase-to-phase voltages

during a three-phase synthetic test (T100s; k =1,3 ) performed according to the

pp

three-phase synthetic circuit shown in Figure J.3a .213

Figure J.3c – TRV voltages waveshapes of the test circuit described in Figure J.3a.215

Figure K.1 – Example of a three-phase current circuit with single-phase synthetic injection . 237

Figure K.2 – Representation of the testing conditions of Table K.1a.239

Figure K.3 – Representation of the testing conditions of Table K.1b.241

Figure K.4 – Representation of the testing conditions of Table K.2a.243

Figure K.5 – Representation of the testing conditions of Table K.2b.245

Figure K.6 – Representation of the testing conditions of Table K.3a.247

Figure K.7 – Representation of the testing conditions of Table K.3b.249

Figure K.8 – Representation of the testing conditions of Table K.4a.251

Figure K.9 – Representation of the testing conditions of Table K.4b.253

Figure L.1 – Graphical representation of the test shown in Table L.1 .267

Figure L.2 – Graphical representation of the test shown in Table L.2 .269

Table 1 – Test circuits for test duties T100s and T100a .31

Table 2 – Test duties T10, T30, T60 and T100s .33

Table 2a – First-pole-to-clear factor: 1,5 – Test parameters during three-phase

interruption .33

Table 2b – First-pole-to-clear factor: 1,3 – Test parameters during three-phase

interruption .33

Table 3 – Synthetic test methods for test duties T10, T30, T60, T100s, T100a, SP,

DEF, OP and SLF .59

Table I.1a – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 45 ms.175

Table I.1b – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 60 ms.177

Table I.1c – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 75 ms.179

Table I.1d – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 120 ms.181

– 8 – 62271-101 CEI:2006

Tableau I.2a – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 60Hz τ = 45 ms.182

Tableau I.2b – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 60 Hz τ = 60 ms.184

Tableau I.2c – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 60 Hz τ = 75 ms.186

Tableau I.2d – Paramètres de la dernière alternance de courant applicables lors d’une

séquence d’essais de court-circuit T100a en 60 Hz τ = 120 ms.188

Tableau I.3a – Réduction du di/dt de la dernière alternance en 50 Hz dans des

conditions triphasées avec le premier pôle qui coupe en phase A et l’asymétrie

requise en phase C.190

Tableau I.3b – Réduction du di/dt de la dernière alternance en 60 Hz dans des

conditions triphasées avec le premier pôle qui coupe en phase A et l’asymétrie

requise en phase C.192

Tableau I.4a – Valeurs corrigées de TTR pour k = 1,3 et f = 50 Hz .194

pp r

Tableau I.4b – Valeurs corrigées de TTR pour k = 1,3 et f = 60 Hz .196

pp r

Tableau I.4c – Valeurs corrigées de TTR pour k = 1,5 et f = 50 Hz .198

pp r

Tableau I.4d – Valeurs corrigées de TTR pour k = 1,5 et f = 60 Hz .198

pp r

Tableau K.1a – Démonstration des durées d’arc pour un facteur de premier pôle de 1,5.218

Tableau K.1b – Démonstration alternative des durées d’arc pour un facteur de premier

pôle de 1,5.220

Tableau K.2a – Démonstration des durées d’arc pour un facteur de premier pôle de 1,3.222

Tableau K.2b – Démonstration alternative des durées d’arc pour un facteur de premier

pôle de 1,3.224

Tableau K.3a – Démonstration des durées d’arc pour un facteur de premier pôle de 1,5.228

Tableau K.3b – Autre démonstration des durées d’arc pour un facteur de premier pôle

de 1,5 .230

Tableau K.4a – Démonstration des durées d’arc pour un facteur de premier pôle de 1,3.232

Tableau K.4b – Autre démonstration des durées d’arc pour un facteur de premier pôle

de 1,3 .234

Tableau L.1 – Procédure d’essais pour un facteur de premier pôle de 1,5.256

Tableau L.2a – Démonstration alternative des durées d’arc pour un facteur de premier

pôle de 1,3.258

Tableau L.2b – Procédure d’essais simplifiée pour un facteur de premier pôle de 1,3 .260

Tableau L.3 – Procédure d’essais pour des courants asymétriques dans le cas d’un

facteur de premier pôle de 1,5 .262

Tableau L.4 – Procédure d’essais pour des courants asymétriques dans le cas d’un

facteur de premier pôle de 1,3 .264

Tableau L.5 – Conditions d’arc requises en ° pour les différentes conditions

asymétriques, f = 50 Hz.270

r

Tableau L.6 – Conditions d’arc requises en ° pour les différentes conditions

asymétriques, f = 60 Hz.272

r

Tableau M.1 – Tolérances sur les paramètres d’essais lors des essais de type .276

62271-101 IEC:2006 – 9 –

Table I.2a – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 45 ms.183

Table I.2b – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 60 ms.185

Table I.2c – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 75 ms.187

Table I.2d – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 120 ms.189

Table I.3a – Last loop di/dt reduction for 50 Hz under three-phase conditions with the

first pole to clear in phase A and the required asymmetry in phase C.191

Table I.3b – Last loop di/dt reduction for 60 Hz under three- phase conditions with the

first pole to clear in phase A and the required asymmetry in phase C.193

Table I.4a – Corrected TRV values for k = 1,3 and f = 50 Hz.195

pp r

Table I.4b – Corrected TRV values for k = 1,3 and f = 60 Hz.197

pp r

Table I.4c – Corrected TRV values for k = 1,5 and f = 50 Hz.199

pp r

Table I.4d – Corrected TRV values for k = 1,5 and f = 60 Hz.199

pp r

Table K.1a – Demonstration of arcing times for a first-pole-to-clear factor of 1,5.219

Table K.1b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,5 .221

Table K.2a – Demonstration of arcing times for a first-pole-to-clear factor of 1,3.223

Table K.2b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 .225

Table K.3a – Demonstration of arcing times for a first-pole-to-clear factor of 1,5.229

Table K.3b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,5 .231

Table K.4a – Demonstration of arcing times for a first-pole-to-clear factor of 1,3.233

Table K.4b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 .235

Table L.1 – Test procedure for a first-pole-to-clear factor of 1,5.257

Table L.2a – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 .259

Table L.2b – Simplified test procedure for a first-pole-to-clear factor of 1,3.261

Table L.3 – Test procedure for asymmetrical currents in the case of a first-pole-to-

clear factor of 1,5.263

Table L.4 – Test procedure for asymmetrical currents in the case of a first-pole-to-

clear factor of 1,3.265

Table L.5 – Required arcing windows in ° for different asymmetrical conditions, f =

r

50 Hz.271

Table L.6 – Required arcing windows in ° for different asymmetrical conditions, f =

r

60 Hz.273

Table M.1 – Tolerances on test quantities for type tests.277

– 10 – 62271-101 CEI:2006

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

___________

APPAREILLAGE À HAUTE TENSION –

Partie 101: Essais synthétiques

AVANT-PROPOS

1) La Commission Electrotechnique Internationale (CEI) est une organisation mondiale de normalisation

composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a

pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les

domaines de l'électricité et de l'électronique. A cet effet, la CEI – entre autres activités – publie des Normes

internationales, des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au

public (PAS) et des Guides (ci-après dénommés "Publication(s) de la CEI"). Leur élaboration est confiée à des

comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les

organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent

également aux travaux.

...

IEC 62271-101 ®

Edition 1.1 2010-11

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

High-voltage switchgear and controlgear –

Part 101: Synthetic testing

Appareillage à haute tension –

Partie 101: Essais synthétiques

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by

any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or

IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

§ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

§ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

§ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

§ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

§ Catalogue des publications de la CEI: www.iec.ch/searchpub/cur_fut-f.htm

Le Catalogue en-ligne de la CEI vous permet d’effectuer des recherches en utilisant différents critères (numéro de référence,

texte, comité d’études,…). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

§ Just Published CEI: www.iec.ch/online_news/justpub

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles

publications parues. Disponible en-ligne et aussi par email.

§ Electropedia: www.electropedia.org

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et

définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé

Vocabulaire Electrotechnique International en ligne.

§ Service Clients: www.iec.ch/webstore/custserv/custserv_entry-f.htm

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du

Service clients ou contactez-nous:

Email: csc@iec.ch

Tél.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 62271-101 ®

Edition 1.1 2010-11

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

High-voltage switchgear and controlgear –

Part 101: Synthetic testing

Appareillage à haute tension –

Partie 101: Essais synthétiques

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

PRICE CODE

C7

CODE PRIX

ICS 29.130.10

ISBN 978-2-88912-191-5

– 2 – 62271-101 IEC:2006+A1:2010

CONTENTS

FOREWORD . 6

INTRODUCTION (to amendment 1) . 8

1 Scope . 9

2 Normative references . 9

3 Terms and definitions . 9

4 Synthetic testing techniques and methods for short-circuit breaking tests . 11

4.1 Basic principles and general requirements for synthetic breaking test

methods . 11

4.2 Synthetic test circuits and related specific requirements for breaking tests . 14

4.3 Three-phase synthetic test methods . 17

5 Synthetic testing techniques and methods for short-circuit making tests . 19

5.1 Basic principles and general requirements for synthetic making test methods . 19

5.2 Synthetic test circuit and related specific requirements for making tests . 20

6 Specific requirements for synthetic tests for making and breaking performance

related to the requirements of 6.102 through 6.111 of IEC 62271-100 . 21

Annex A (informative) Current distortion . 42

Annex B (informative) Current injection methods. 58

Annex C (informative) Voltage injection methods . 63

Annex D (informative) Duplicate circuit (transformer or Skeats circuit) . 66

Annex E (normative) Information to be given and results to be recorded for synthetic tests . 69

Annex F (informative) Special procedures for testing circuit-breakers having parallel

breaking resistors . 70

Annex G (informative) Synthetic methods for capacitive-current switching . 73

Annex H (informative) Re-ignition methods to prolong arcing . 85

Annex I (normative) Reduction in di/dt and TRV for test duty T100a . 89

Annex J (informative) Three-phase synthetic test circuits . 103

Annex K (normative) Test procedure using a three-phase current circuit and one

voltage circuit . 111

Annex L (normative) Splitting of test duties in test series taking into account the

associated TRV for each pole-to-clear . 130

Annex M (normative) Tolerances on test quantities for type tests . 140

Annex N (informative) Typical test circuits for metal-enclosed and dead tank circuit

breakers . 143

Bibliography . 143

Figure 1 – Interrupting process – Basic time intervals . 33

Figure 2 – Example of recovery voltage . 34

Figure 3 – Equivalent surge impedance of the voltage circuit for the current injection

method . 35

Figure 4 – Making process – Basic time intervals . 36

Figure 5 – Typical synthetic make circuit for single-phase tests . 38

Figure 6 – Typical synthetic make circuit for three-phase tests (k = 1,5) . 39

pp

Figure 7 – Comparison of arcing time settings during three-phase direct tests (left)

and three-phase synthetic (right) for T100s with k = 1,5 . 40

pp

62271-101 IEC:2006+A1:2010 – 3 –

Figure 8 – Comparison of arcing time settings during three-phase direct tests (left)

and three-phase synthetic (right) for T100a with k = 1,5 . 41

pp

Figure A.1 – Direct circuit, simplified diagram . 49

Figure A.2 – Prospective short-circuit current . 49

Figure A.3 – Distortion current . 49

Figure A.4 – Distortion current . 50

Figure A.5 – Simplified circuit diagram . 51

Figure A.6 – Current and arc voltage characteristics for symmetrical current . 52

Figure A.7 – Current and arc voltage characteristics for asymmetrical current . 53

Figure A.8 – Reduction of amplitude and duration of final current loop of arcing . 54

Figure A.9 – Reduction of amplitude and duration of final current loop of arcing . 55

Figure A.10 – Reduction of amplitude and duration of final current loop of arcing . 56

Figure A.11 – Reduction of amplitude and duration of final current loop of arcing . 57

Figure B.1 – Typical current injection circuit with voltage circuit in parallel with the test

circuit-breaker . 60

Figure B.2 – Injection timing for current injection scheme with circuit B.1 . 60

Figure B.3 – Typical current injection circuit with voltage circuit in parallel with the

auxiliary circuit-breaker . 61

Figure B.4 – Injection timing for current injection scheme with circuit B.3 . 61

Figure B.5 – Examples of the determination of the interval of significant change of arc

voltage from the oscillograms . 62

Figure C.1 – Typical voltage injection circuit diagram with voltage circuit in parallel

with the auxiliary circuit-breaker (simplified diagram) . 64

Figure C.2 – TRV waveshapes in a voltage injection circuit with the voltage circuit in

parallel with the auxiliary circuit-breaker . 65

Figure D.1 – Transformer or Skeats circuit . 67

Figure D.2 – Triggered transformer or Skeats circuit . 68

Figure G.1 – Capacitive current circuits (parallel mode) . 76

Figure G.2 – Current injection circuit . 77

Figure G.3 – LC oscillating circuit . 78

Figure G.4 – Inductive current circuit in parallel with LC oscillating circuit . 79

Figure G.5 – Current injection circuit, normal recovery voltage applied to both

terminals of the circuit-breaker . 80

Figure G.6 – Synthetic test circuit (series circuit), normal recovery voltage applied to

both sides of the test circuit breaker . 81

Figure G.7 – Current injection circuit, recovery voltage applied to both sides of the

circuit-breaker . 82

Figure G.8 – Making test circuit . 83

Figure G.9 – Inrush making current test circuit . 84

Figure H.1 – Typical re-ignition circuit diagram for prolonging arc-duration . 86

Figure H.2 – Combined Skeats and current injection circuits . 87

Figure H.3 – Typical waveforms obtained during an asymmetrical test using the circuit

in Figure H.2 . 88

Figure J.1a – Three-phase synthetic combined circuit . 105

Figure J.1b – Waveshapes of currents, phase-to-ground and phase-to phase voltages

during a three-phase synthetic test (T100s; k = 1,5 ) performed according to the

pp

three-phase synthetic combined circuit . 106

Figure J.2a – Three-phase synthetic circuit with injection in all phases for k = 1,5 . 107

pp

– 4 – 62271-101 IEC:2006+A1:2010

Figure J.2b – Waveshapes of currents and phase-to-ground voltages during a three-

phase synthetic test (T100s; k =1,5) performed according to the three-phase

pp

synthetic circuit with injection in all phases . 108

Figure J.3a – Three-phase synthetic circuit for terminal fault tests with k = 1,3

pp

(current injection method) . 109

Figure J.3b – Waveshapes of currents, phase-to-ground and phase-to-phase voltages

during a three-phase synthetic test (T100s; k =1,3 ) performed according to the

pp

three-phase synthetic circuit shown in Figure J.3a . 109

Figure J.3c – TRV voltages waveshapes of the test circuit described in Figure J.3a . 110

Figure K.1 – Example of a three-phase current circuit with single-phase synthetic injection . 121

Figure K.2 – Representation of the testing conditions of Table K.1a . 122

Figure K.3 – Representation of the testing conditions of Table K.1b . 123

Figure K.4 – Representation of the testing conditions of Table K.2a . 124

Figure K.5 – Representation of the testing conditions of Table K.2b . 125

Figure K.6 – Representation of the testing conditions of Table K.3a . 126

Figure K.7 – Representation of the testing conditions of Table K.3b . 127

Figure K.8 – Representation of the testing conditions of Table K.4a . 128

Figure K.9 – Representation of the testing conditions of Table K.4b . 129

Figure L.1 – Graphical representation of the test shown in Table L.1 . 136

Figure L.2 – Graphical representation of the test shown in Table L.2 . 137

Figure N.1 – Test circuit for unit testing (circuit-breaker with interaction

due to gas circulation) . 144

Figure N.2 – Half-pole testing of a circuit-breaker in test circuit given by Figure N.1 –

Example of the required TRVs to be applied between the terminals of the unit(s)

under test and between the live parts and the insulated enclosure . 145

Figure N.3 – Synthetic test circuit for unit testing (if unit testing is allowed as per

Subclause 6.102.4.2 of IEC 62271-100:2008) . 146

Figure N.4 – Half-pole testing of a circuit-breaker in the test circuit of Figure N.3 –

Example of the required TRVs to be applied between the terminals of the unit(s)

under test and between the live parts and the insulated enclosure . 147

Figure N.5 – Capacitive current injection circuit with enclosure of the circuit-breaker

energized . 148

Figure N.6 – Capacitive synthetic circuit using two power-frequency sources

and with the enclosure of the circuit-breaker energized . 149

Figure N.7 – Capacitive synthetic current injection circuit – Example of unit testing

on half a pole of a circuit-breaker with two units per pole – Enclosure energized

with d.c. voltage source . 150

Figure N.8 – Symmetrical synthetic test circuit for out-of-phase switching tests on a

complete pole of a circuit-breaker . 151

Figure N.9 – Full pole test with voltage applied to both terminals

and the metal enclosure . 152

Table 1 – Test circuits for test duties T100s and T100a . 17

Table 2 – Test duties T10, T30, T60 and T100s . 18

Table 2a – First-pole-to-clear factor: 1,5 – Test parameters during three-phase

interruption . 18

Table 2b – First-pole-to-clear factor: 1,3 – Test parameters during three-phase

interruption . 18

Table 3 – Synthetic test methods for test duties T10, T30, T60, T100s, T100a, SP,

DEF, OP and SLF . 31

62271-101 IEC:2006+A1:2010 – 5 –

Table I.1a – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 45 ms . 90

Table I.1b – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 60 ms . 91

Table I.1c – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 75 ms . 92

Table I.1d – Last current loop parameters for 50 Hz operation in relation to short-circuit

test duty T100a τ = 120 ms . 93

Table I.2a – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 45 ms . 94

Table I.2b – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 60 ms . 95

Table I.2c – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 75 ms . 96

Table I.2d – Last current loop parameters for 60 Hz operation in relation to short-circuit

test duty T100a τ = 120 ms . 97

Table I.3a I.1a – Last loop di/dt reduction for 50 Hz under three-phase conditions with

the first pole to clear in phase A and the required asymmetry in phase C . 98

Table I.3b I.1b – Last loop di/dt reduction for 60 Hz under three- phase conditions with

the first pole to clear in phase A and the required asymmetry in phase C . 99

Table I.4a I.2a – Corrected TRV values for k = 1,3 and f = 50 Hz . 100

pp r

Table I.4b I.2b – Corrected TRV values for k = 1,3 and f = 60 Hz . 101

pp r

Table I.4c I.2c – Corrected TRV values for k = 1,5 and f = 50 Hz . 102

pp r

Table I.4d I.2d – Corrected TRV values for k = 1,5 and f = 60 Hz . 102

pp r

Table K.1a – Demonstration of arcing times for a first-pole-to-clear factor of 1,5 . 112

Table K.1b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,5 . 113

Table K.2a – Demonstration of arcing times for a first-pole-to-clear factor of 1,3 . 114

Table K.2b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 . 115

Table K.3a – Demonstration of arcing times for a first-pole-to-clear factor of 1,5 . 117

Table K.3b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,5 . 118

Table K.4a – Demonstration of arcing times for a first-pole-to-clear factor of 1,3 . 119

Table K.4b – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 . 120

Table L.1 – Test procedure for a first-pole-to-clear factor of 1,5 . 131

Table L.2a – Alternative demonstration of arcing times for a first-pole-to-clear factor

of 1,3 . 132

Table L.2b – Simplified test procedure for a first-pole-to-clear factor of 1,3 . 133

Table L.3 – Test procedure for asymmetrical currents in the case of a first-pole-to-

clear factor of 1,5 . 134

Table L.4 – Test procedure for asymmetrical currents in the case of a first-pole-to-

clear factor of 1,3 . 135

Table L.5 – Required arcing windows in ° for different asymmetrical conditions, f = 50 Hz . 138

r

Table L.6 – Required arcing windows in ° for different asymmetrical conditions, f = 60 Hz . 139

r

Table M.1 – Tolerances on test quantities for type tests . 141

– 6 – 62271-101 IEC:2006+A1:2010

INTERNATIONAL ELECTROTECHNICAL COMMISSION

___________

HIGH-VOLTAGE SWITCHGEAR AND CONTROLGEAR –

Part 101: Synthetic testing

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

This consolidated version of IEC 62271-101 consists of the first edition (2006)

[documents 17A/753/FDIS and 17A/755/RVD] and its amendment 1 (2010) [documents

17A/907/FDIS and 17A/919/RVD]. It bears the edition number 1.1.

The technical content is therefore identical to the base edition and its amendment and

has been prepared for user convenience. A vertical line in the margin shows where the

base publication has been modified by amendment 1. Additions and deletions are

displayed in red, with deletions being struck through.

62271-101 IEC:2006+A1:2010 – 7 –

International Standard IEC 62271-101 has been prepared by subcommittee 17A: High-voltage

switchgear and controlgear, of IEC technical committee 17: Switchgear and controlgear.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

This publication shall be read in conjunction with IEC 62271-100. The numbering of the

subclauses of Clause 6 is the same as in IEC 62271-100. However, not all subclauses of IEC

62271-100 are addressed; merely those where synthetic testing has introduced changes.

The IEC 62271-100 series consists of the following parts, under the general title High-voltage

switchgear and controlgear:

Part 100: High-voltage alternating-current circuit-breakers

Part 101: Synthetic testing

Part 102: Alternating current disconnectors and earthing switches

Part 104: Alternating current switches for rated voltages of 52 kV and above

Part 105: Alternating current switch-fuse combinations

Part 107: Alternating current fused circuit-switchers for rated voltages above 1 kV up to and

including 52 kV

Part 108: High voltage alternating current disconnecting circuit-breakers for rated voltages

of 72,5 kV and above

Part 109: Alternating-current series capacitor by-pass switches

Part 110: Inductive load switching

A list of the other parts belonging to the IEC 62271 series can be found on the IEC website

http://www.iec.ch. Further information is available on http://tc17.iec.ch.

The committee has decided that the contents of the base publication and its amendments will

remain unchanged until the stability date indicated on the IEC web site under

"http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will

be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The “colour inside” logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct understanding

of its contents. Users should therefore print this publication using a colour printer.

___________

Some of these parts are still in the process of being developed.

– 8 – 62271-101 IEC:2006+A1:2010

INTRODUCTION

(to amendment 1)

This amendment cancels and replaces IEC 61633.

The original edition of IEC 62271-101 (2006) makes extensive reference to

IEC 62271-100:2001. Since then, a new edition of IEC 62271-100 has been published (2008).

Within this amendment, references are made to IEC 62271-100:2008. Unless they are

explicitly mentioned in this amendment, all of the references in the original edition of

IEC 62271-101 (2006) still make reference to IEC 62271-100:2001. A second amendment to

IEC 62271-101, which will update all cross-references to the new IEC 62271-100:2008, is

under consideration.

62271-101 IEC:2006+A1:2010 – 9 –

HIGH-VOLTAGE SWITCHGEAR AND CONTROLGEAR –

Part 101: Synthetic testing

1 Scope

This part of IEC 62271 mainly applies to a.c. circuit-breakers within the scope of IEC 62271-100.

It provides the general rules for testing a.c. circuit-breakers, for making and breaking capacities

over the range of test duties described in 6.102 to 6.111 of IEC 62271-100, by synthetic methods.

NOTE Circuits for the test duties described in 6.111 have not yet been standardized. However, present methods

are given in Annex G.

It has been proven that synthetic testing is an economical and technically correct way to test

high-voltage a.c. circuit-breakers according to the requirements of IEC 62271-100 and that it

is equivalent to direct testing.

The methods and techniques described are those in general use. The purpose of this

standard is to establish criteria for synthetic testing and for the proper evaluation of results.

Such criteria will establish the validity of the test method without imposing restraints on

innovation of test circuitry.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61633:1995, High-voltage alternating current circuit-breakers – Guide for short-circuit and

switching test procedures for metal-enclosed and dead tank circuit-breakers

IEC 62271-100:2001 2008, High-voltage switchgear and controlgear – Part 100: High-voltage

Alternating current circuit-breakers

IEC 62271-308:2002, High-voltage switchgear and controlgear – Part 308: Guide for asym-

metrical short-circuit test duty T100a

3 Terms and definitions

For the purposes of this document, the terms and definitions of IEC 62271-100, as well as the

following terms and definitions, apply.

3.1

direct test

test in which the applied voltage, the current and the transient and power-frequency recovery

voltages are all obtained from a circuit having a single-power source, which may be a power

system or special alternators as used in short-circuit testing stations or a combination of both

___________

Unless explicitly otherwise mentioned, all of the references to IEC 62271-100 make reference to IEC 62271-100:2001. A

second amendment to IEC 62271-101, which will update all cross-references to the new IEC 62271-100:2008, is under

consideration.

– 10 – 62271-101 IEC:2006+A1:2010

3.2

synthetic test

test in which all of the current, or a major portion of it, is obtained from one source (current

circuit), and in which the applied voltage and/or the recovery voltages (transient and power

frequency) are obtained wholly or in part from one or more separate sources (voltage circuits)

3.3

test circuit-breaker

circuit-breaker under test (see 6.102.2 of IEC 62271-100:2001)

3.4

auxiliary circuit-breaker(s)

circuit-breaker(s) forming part of a synthetic test circuit used to put the test circuit-breaker

into the required relation with various circuits

3.5

current circuit

that part of the synthetic test circuit from which all or the major part of the power-frequency

current is obtained

3.6

voltage circuit

that part of the synthetic test circuit from which all or the major part of the applied voltage

and/or recovery voltage is obtained

3.7

prospective current (of a circuit and with respect to a circuit-breaker)

current that would flow in the circuit if each pole of the test and auxiliary circuit-breakers were

replaced by a conductor of negligible impedance

[IEV 441-17-01, modified]

3.8

actual current

current through the test circuit-breaker (prospective current modified by the arc voltage of the

test and auxiliary circuit-breakers)

3.9

distortion current

calculated current equal to the difference between the prospective current and the actual

current

3.10

post-arc current

current which flows through the arc gap of a circuit-breaker when the current and arc voltage

have fallen to zero and the transient recovery voltage has begun to rise

3.11

current-injection method

synthetic test method in which the voltage circuit is applied to the test circuit-breaker before

power-frequency current zero

3.12

initial transient making current

ITMC

transient current which flows through the circuit-breaker at the moment of voltage breakdown

prior to the initiation of current from the current circuit during making

62271-101 IEC:2006+A1:2010 – 11 –

3.13

injected current

current supplied by the voltage circuit of a current injection circuit when it is connected to the

circuit-breaker under test

3.14

voltage-injection method

synthetic test method in which the voltage circuit is applied to the test circuit-breaker after

power frequency current zero

3.15

reference system conditions

conditions of an electrical system having the parameters from which the rated and test values

of IEC 62271-100 are derived

3.16

time delay of making device

t

m

time interval, during synthetic making test, between the instant of breakdown of the applied

voltage and the initiation of current from the current circuit

3.17

minimum clearing time

sum of the minimum opening time, minimum relay time (½ cycle), and the minimum arcing

time for the minor loop of the first-pole-to-clear, during test duty T100a only, as declared by

the manufacturer. This definition should be used only for the determination of the test

parameters for test duty T100a.

NOTE 1 The minimum clearing time obtained during the tests should not be lower than the value declared by the

manufacturer. Prior to the tests, the minimum opening time should be measured at maximum trip coil voltage

maximum pressure for operation and minimum pressure for interruption. If the minimum opening time measured

prior to the tests is lower than the one declared by the manufacturer, this lower value should be used for the

determination of the required test parameters.

NOTE 2 This definition assumes that the minimum clearing time obtained with the minimum pressure for

interruption is similar to the one that would be obtained with the maximum pressure for interruption. Normally, the

minimum clearing time is obtained with the maximum pressure for interruption. If such pressure condition is giving

a minimum clearing time such that the minimum clearing time range applicable (as given in Tables 1a to 2d of

IEC 62271-308:2002) for tests is different than the one obtained at minimum pressure for interruption, then it is

permissible to verify the minimum clearing time by using the maximum pressure for interruption.

3.18

pre-strike

voltage breakdown between the contacts during a making operation which initiates current

flow

4 Synthetic testing techniques and methods for short-circuit breaking tests

4.1 Basic principles and general requirements for synthetic breaking test methods

Any particular synthetic method chosen for testing shall adequately stress the test circuit-

breaker. Generally, the adequacy is established when the test method meets the requirements

set forth in the following subclauses.

– 12 – 62271-101 IEC:2006+A1:2010

A circuit-breaker has two basic positions: closed and open. In the closed position a circuit-

breaker conducts full current with negligible voltage drop across its contacts. In the open

position it conducts negligible current but with full voltage across the contacts. This defines

the two main stresses, the current stress and the voltage stress, which are separated in time.

If closer attention is paid to the voltage and current stresses during the interrupting process

(Figure 1), three main intervals can be recognized:

– High-current interval

The high-current interval is the time from contact separation to the start of the significant

change in arc voltage. The high-current interval precedes the interaction and high-voltage

intervals.

– Interaction interval

The interaction interval is the time from the start of the significant change in arc voltage

prior to current zero to the time when the current including the post-arc current, if any,

ceases to flow through the test circuit-breaker (see also Clause B.2).

– High-voltage interval

The high-voltage interval is the time from the moment when the current including the post-

arc current, if any, ceases to flow through the test circuit-breaker to the end of the test.

4.1.1 High-current interval

During the high-current interval the test circuit-breaker shall be stressed by the test circuit in

such a way that the starting conditions for the interaction interval, within tolerances to be

specified, are the same as under reference system conditions.

In synthetic test circuits the ratio of the power-frequency voltage of the current circuit to the

arc voltage is low in comparison with tests at reference system conditions due to:

– the voltage of the current circuit being a fraction of the system voltage;

– the fact that the arc voltages of the test circuit-breaker and of the auxiliary circuit-breaker

are added.

As a result the duration of the current loop and the peak value of the current will be reduced.

This distortion of the current is outlined in Annex A.

Considerations with respect to the arc energy released in the test circuit-breaker lead to a

maximum permissible influence in terms of tolerances on two characteristic values of the

shape of the current, i.e. current-peak value and current-loop duration (see Annex A).

The tolerance on the amplitude and the power frequency of the prospective breaking current

is given in 6.103.2 and 6.104.3 of IEC 62271-100. Therefore, the following conditions

concerning the actual current through the test circuit-breaker shall be met:

– for symmetrical testing the current amplitude and final loop duration shall not be less than

90 % of the required values based on rated current;

– for asymmetrical testing, the current amplitude and final loop duration shall be between

90 % and 110 % of the required values, based on rated current and time constant (see

Tables I.1a to I.2d 15 through 22 of IEC 62271-100:2008).

62271-101 IEC:2006+A1:2010 – 13 –

Adjustment measures:

The amplitude and duration of the last current loop may be adjusted by several means,

such as

– increasing or decreasing of the r.m.s. value of the short-circuit test current,

– changing of the frequency of the test current,

– using pre-tripping or delayed tripping,

– changing the instant of current initiation (initial d.c. component).

For reference see 5.3 of IEC 62271-308.

4.1.2 Interaction interval

During the interaction interval, the short-circuit current stress changes into high-voltage stress

and the circuit-breaker performance can significantly influence the current and voltages in the

circuit. As the current decreases to zero, the arc voltage m

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...