IEC 61691-4:2004

(Main)Behavioural languages - Part 4: Verilog® hardware description language

Behavioural languages - Part 4: Verilog® hardware description language

Contains the formal syntax and semantics of all Verilog HDL constructs; the formal syntax and semantics of Standard Delay Format (SDF) constructs; simulation system tasks and functions,such as text output display commands; compiler directives,such as text substitution macros and simulation time scaling; the Programming Language Interface (PLI) binding mechanism; the formal syntax and semantics of access routines,task/function routines,and Verilog procedural interface routines; informative usage examples; informative delay model for SDF; listings of header files for PLI This publication has the status of a double logo IEEE/IEC standard

General Information

- Status

- Withdrawn

- Publication Date

- 04-Oct-2004

- Withdrawal Date

- 31-May-2011

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 2 - TC 91/WG 2

- Current Stage

- WPUB - Publication withdrawn

- Start Date

- 01-Jun-2011

- Completion Date

- 14-Feb-2026

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 61691-4:2004 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Behavioural languages - Part 4: Verilog® hardware description language". This standard covers: Contains the formal syntax and semantics of all Verilog HDL constructs; the formal syntax and semantics of Standard Delay Format (SDF) constructs; simulation system tasks and functions,such as text output display commands; compiler directives,such as text substitution macros and simulation time scaling; the Programming Language Interface (PLI) binding mechanism; the formal syntax and semantics of access routines,task/function routines,and Verilog procedural interface routines; informative usage examples; informative delay model for SDF; listings of header files for PLI This publication has the status of a double logo IEEE/IEC standard

Contains the formal syntax and semantics of all Verilog HDL constructs; the formal syntax and semantics of Standard Delay Format (SDF) constructs; simulation system tasks and functions,such as text output display commands; compiler directives,such as text substitution macros and simulation time scaling; the Programming Language Interface (PLI) binding mechanism; the formal syntax and semantics of access routines,task/function routines,and Verilog procedural interface routines; informative usage examples; informative delay model for SDF; listings of header files for PLI This publication has the status of a double logo IEEE/IEC standard

IEC 61691-4:2004 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.060 - Languages used in information technology. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61691-4:2004 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL IEC

STANDARD 61691-4

First edition

2004-10

™

IEEE 1364

Behavioural languages –

Part 4:

Verilog® hardware description language

Reference number

IEC 61691-4(E):2004

IEEE Std. 1364(E):2001

Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the

60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example,

edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the

base publication incorporating amendment 1 and the base publication incorporating

amendments 1 and 2.

Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC,

thus ensuring that the content reflects current technology. Information relating to

this publication, including its validity, is available in the IEC Catalogue of

publications (see below) in addition to new editions, amendments and corrigenda.

Information on the subjects under consideration and work in progress undertaken

by the technical committee which has prepared this publication, as well as the list

of publications issued, is also available from the following:

• IEC Web Site (www.iec.ch)

• Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/searchpub) enables you to

search by a variety of criteria including text searches, technical committees

and date of publication. On-line information is also available on recently issued

publications, withdrawn and replaced publications, as well as corrigenda.

• IEC Just Published

This summary of recently issued publications (www.iec.ch/online_news/ justpub)

is also available by email. Please contact the Customer Service Centre (see

below) for further information.

• Customer Service Centre

If you have any questions regarding this publication or need further assistance,

please contact the Customer Service Centre:

Email: custserv@iec.ch

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

INTERNATIONAL IEC

STANDARD 61691-4

First edition

2004-10

™

IEEE 1364

Behavioural languages –

Part 4:

Verilog® hardware description language

Copyright © IEEE 2004 ⎯ All rights reserved

IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Inc.

No part of this publication may be reproduced or utilized in any form or by any means, electronic or

mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

The Institute of Electrical and Electronics Engineers, Inc, 3 Park Avenue, New York, NY 10016-5997, USA

Telephone: +1 732 562 3800 Telefax: +1 732 562 1571 E-mail: stds-info@ieee.org Web: www.standards.ieee.org

Commission Electrotechnique Internationale

International Electrotechnical Commission

Международная Электротехническая Комиссия

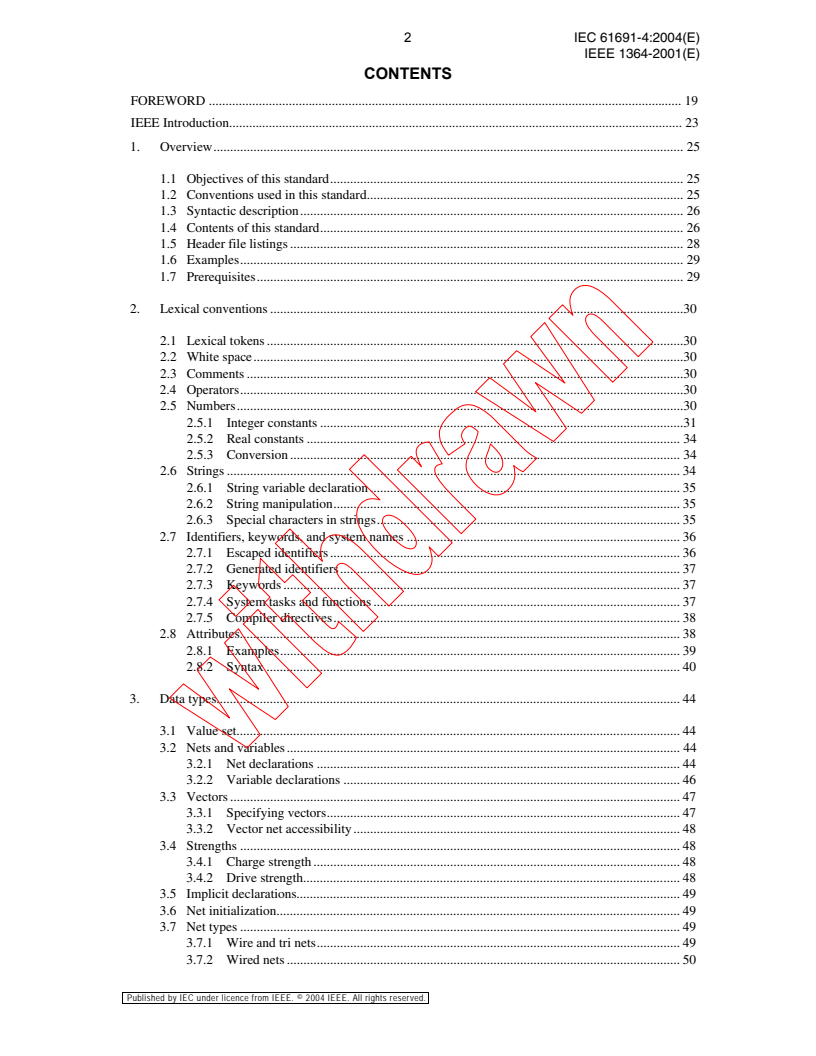

2 IEC 61691-4:2004(E)

IEEE 1364-2001(E)

CONTENTS

FOREWORD . 19

IEEE Introduction. 23

1. Overview. 25

1.1 Objectives of this standard. 25

1.2 Conventions used in this standard. 25

1.3 Syntactic description. 26

1.4 Contents of this standard. 26

1.5 Header file listings . 28

1.6 Examples. 29

1.7 Prerequisites. 29

2. Lexical conventions .30

2.1 Lexical tokens .30

2.2 White space.30

2.3 Comments .30

2.4 Operators.30

2.5 Numbers.30

2.5.1 Integer constants .31

2.5.2 Real constants . 34

2.5.3 Conversion . 34

2.6 Strings . 34

2.6.1 String variable declaration . 35

2.6.2 String manipulation. 35

2.6.3 Special characters in strings. 35

2.7 Identifiers, keywords, and system names . 36

2.7.1 Escaped identifiers. 36

2.7.2 Generated identifiers. 37

2.7.3 Keywords . 37

2.7.4 System tasks and functions . 37

2.7.5 Compiler directives. 38

2.8 Attributes. 38

2.8.1 Examples. 39

2.8.2 Syntax . 40

3. Data types. 44

3.1 Value set. 44

3.2 Nets and variables. 44

3.2.1 Net declarations . 44

3.2.2 Variable declarations . 46

3.3 Vectors . 47

3.3.1 Specifying vectors. 47

3.3.2 Vector net accessibility. 48

3.4 Strengths . 48

3.4.1 Charge strength . 48

3.4.2 Drive strength. 48

3.5 Implicit declarations. 49

3.6 Net initialization. 49

3.7 Net types . 49

3.7.1 Wire and tri nets. 49

3.7.2 Wired nets . 50

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1364-2001(E)

3.7.3 Trireg net. 50

3.7.4 Tri0 and tri1 nets. 54

3.7.5 Supply nets. 55

3.8 regs. 55

3.9 Integers, reals, times, and realtimes. 55

3.9.1 Operators and real numbers . 56

3.9.2 Conversion . 56

3.10 Arrays. 57

3.10.1 Net arrays. 57

3.10.2 reg and variable arrays. 57

3.10.3 Memories . 57

3.11 Parameters. 58

3.11.1 Module parameters. 59

3.11.2 Local parameters—localparam . 60

3.11.3 Specify parameters. 61

3.12 Name spaces. 62

4. Expressions . 64

4.1 Operators. 64

4.1.1 Operators with real operands . 65

4.1.2 Binary operator precedence . 66

4.1.3 Using integer numbers in expressions . 67

4.1.4 Expression evaluation order. 67

4.1.5 Arithmetic operators . 68

4.1.6 Arithmetic expressions with regs and integers . 69

4.1.7 Relational operators . 70

4.1.8 Equality operators . 70

4.1.9 Logical operators . 71

4.1.10 Bit-wise operators . 71

4.1.11 Reduction operators . 72

4.1.12 Shift operators. 73

4.1.13 Conditional operator . 74

4.1.14 Concatenations. 75

4.1.15 Event or. 76

4.2 Operands . 76

4.2.1 Vector bit-select and part-select addressing . 76

4.2.2 Array and memory addressing. 78

4.2.3 Strings . 79

4.3 Minimum, typical, and maximum delay expressions . 81

4.4 Expression bit lengths. 83

4.4.1 Rules for expression bit lengths. 83

4.4.2 An example of an expression bit-length problem. 84

4.4.3 Example of self-determined expressions . 85

4.5 Signed expressions. 86

4.5.1 Rules for expression types . 86

4.5.2 Steps for evaluating an expression. 86

4.5.3 Steps for evaluating an assignment. 87

4.5.4 Handling X and Z in signed expressions . 87

5. Scheduling semantics. 88

5.1 Execution of a model . 88

5.2 Event simulation . 88

viii Copyright © 2001 IEEE. All rights reserved.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

4 IEC 61691-4:2004(E)

IEEE 1364-2001(E)

5.3 The stratified event queue. 88

5.4 The Verilog simulation reference model . 89

5.4.1 Determinism. 90

5.4.2 Nondeterminism. 90

5.5 Race conditions. 90

5.6 Scheduling implication of assignments . 90

5.6.1 Continuous assignment . 91

5.6.2 Procedural continuous assignment. 91

5.6.3 Blocking assignment. 91

5.6.4 Nonblocking assignment. 91

5.6.5 Switch (transistor) processing. 91

5.6.6 Port connections. 92

5.6.7 Functions and tasks. 92

6. Assignments. 93

6.1 Continuous assignments. 93

6.1.1 The net declaration assignment. 94

6.1.2 The continuous assignment statement . 94

6.1.3 Delays . 96

6.1.4 Strength. 96

6.2 Procedural assignments. 97

6.2.1 Variable declaration assignment. 97

6.2.2 Variable declaration syntax. 98

7. Gate and switch level modeling. 99

7.1 Gate and switch declaration syntax. 99

7.1.1 The gate type specification . 101

7.1.2 The drive strength specification. 101

7.1.3 The delay specification . 102

7.1.4 The primitive instance identifier.102

7.1.5 The range specification. 102

7.1.6 Primitive instance connection list . 103

7.2 and, nand, nor, or, xor, and xnor gates. 105

7.3 buf and not gates .106

7.4 bufif1, bufif0, notif1, and notif0 gates.107

7.5 MOS switches . 109

7.6 Bidirectional pass switches.110

7.7 CMOS switches .110

7.8 pullup and pulldown sources .111

7.9 Logic strength modeling .112

7.10 Strengths and values of combined signals .113

7.10.1 Combined signals of unambiguous strength.113

7.10.2 Ambiguous strengths: sources and combinations.114

7.10.3 Ambiguous strength signals and unambiguous signals .119

7.10.4 Wired logic net types .123

7.11 Strength reduction by nonresistive devices. 126

7.12 Strength reduction by resistive devices. 126

7.13 Strengths of net types. 126

7.13.1 tri0 and tri1 net strengths . 126

7.13.2 trireg strength. 126

7.13.3 supply0 and supply1 net strengths . 126

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1364-2001(E)

7.14 Gate and net delays . 127

7.14.1 min:typ:max delays. 128

7.14.2 trireg net charge decay. 129

8. User-defined primitives (UDPs) . 131

8.1 UDP definition. 131

8.1.1 UDP header. 133

8.1.2 UDP port declarations. 133

8.1.3 Sequential UDP initial statement. 133

8.1.4 UDP state table . 133

8.1.5 Z values in UDP. 134

8.1.6 Summary of symbols . 134

8.2 Combinational UDPs . 135

8.3 Level-sensitive sequential UDPs . 136

8.4 Edge-sensitive sequential UDPs . 136

8.5 Sequential UDP initialization . 137

8.6 UDP instances. 139

8.7 Mixing level-sensitive and edge-sensitive descriptions. 140

8.8 Level-sensitive dominance. 141

9. Behavioral modeling. 142

9.1 Behavioral model overview . 142

9.2 Procedural assignments. 143

9.2.1 Blocking procedural assignments . 143

9.2.2 The nonblocking procedural assignment . 145

9.3 Procedural continuous assignments . 148

9.3.1 The assign and deassign procedural statements. 149

9.3.2 The force and release procedural statements . 150

9.4 Conditional statement . 151

9.4.1 If-else-if construct. 152

9.5 Case statement . 154

9.5.1 Case statement with don’t-cares . 157

9.5.2 Constant expression in case statement. 157

9.6 Looping statements . 158

9.7 Procedural timing controls. 160

9.7.1 Delay control. 161

9.7.2 Event control. 162

9.7.3 Named events. 162

9.7.4 Event or operator. 163

9.7.5 Implicit event_expression list . 164

9.7.6 Level-sensitive event control . 165

9.7.7 Intra-assignment timing controls . 166

9.8 Block statements . 170

9.8.1 Sequential blocks . 170

9.8.2 Parallel blocks. 171

9.8.3 Block names. 172

9.8.4 Start and finish times . 172

9.9 Structured procedures . 173

9.9.1 Initial construct . 174

9.9.2 Always construct. 174

x Copyright © 2001 IEEE. All rights reserved.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

6 IEC 61691-4:2004(E)

IEEE 1364-2001(E)

10. Tasks and functions. 176

10.1 Distinctions between tasks and functions . 176

10.2 Tasks and task enabling . 176

10.2.1 Task declarations . 177

10.2.2 Task enabling and argument passing . 178

10.2.3 Task memory usage and concurrent activation. 180

10.3 Functions and function calling. 181

10.3.1 Function declarations. 182

10.3.2 Returning a value from a function . 183

10.3.3 Calling a function. 184

10.3.4 Function rules. 184

10.3.5 Use of constant functions. 185

11. Disabling of named blocks and tasks. 187

12. Hierarchical structures . 190

12.1 Modules. 190

12.1.1 Top-level modules . 192

12.1.2 Module instantiation . 192

12.1.3 Generated instantiation . 194

12.2 Overriding module parameter values. 204

12.2.1 defparam statement . 206

12.2.2 Module instance parameter value assignment . 207

12.2.3 Parameter dependence . 209

12.3 Ports . 209

12.3.1 Port definition . 209

12.3.2 List of ports. 209

12.3.3 Port declarations. 210

12.3.4 List of ports declarations. 212

12.3.5 Connecting module instance ports by ordered list. 212

12.3.6 Connecting module instance ports by name . 213

12.3.7 Real numbers in port connections. 214

12.3.8 Connecting dissimilar ports . 215

12.3.9 Port connection rules.215

12.3.10 Net types resulting from dissimilar port connections . 216

12.3.11 Connecting signed values via ports. 217

12.4 Hierarchical names . 217

12.5 Upwards name referencing . 220

12.6 Scope rules . 222

13. Configuring the contents of a design . 224

13.1 Introduction. 224

13.1.1 Library notation . 224

13.1.2 Basic configuration elements. 225

13.2 Libraries . 225

13.2.1 Specifying libraries - the library map file. 225

13.2.2 Using multiple library mapping files . 227

13.2.3 Mapping source files to libraries. 227

13.3 Configurations. 227

13.3.1 Basic configuration syntax. 227

13.3.2 Hierarchical configurations. 230

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

IEEE 1364-2001(E)

13.4 Using libraries and configs . 231

13.4.1 Precompiling in a single-pass use-model. 231

13.4.2 Elaboration-time compiling in a single-pass use-model. 231

13.4.3 Precompiling using a separate compilation tool . 231

13.4.4 Command line considerations. 231

13.5 Configuration examples. 232

13.5.1 Default configuration from library map file . 232

13.5.2 Using the default clause. 232

13.5.3 Using the cell clause . 233

13.5.4 Using the instance clause. 233

13.5.5 Using a hierarchical config . 233

13.6 Displaying library binding information . 234

13.7 Library mapping examples . 234

13.7.1 Using the command line to control library searching. 234

13.7.2 File path specification examples. 234

13.7.3 Resolving multiple path specifications . 235

14. Specify blocks. 236

14.1 Specify block declaration. 236

14.2 Module path declarations. 237

14.2.1 Module path restrictions . 238

14.2.2 Simple module paths. 238

14.2.3 Edge-sensitive paths. 239

14.2.4 State-dependent paths . 240

14.2.5 Full connection and parallel connection paths. 244

14.2.6 Declaring multiple module paths in a single statement . 245

14.2.7 Module path polarity. 246

14.3 Assigning delays to module paths. 247

14.3.1 Specifying transition delays on module paths . 248

14.3.2 Specifying x transition delays. 249

14.3.3 Delay selection. 250

14.4 Mixing module path delays and distributed delays. 251

14.5 Driving wired logic. 252

14.6 Detailed control of pulse filtering behavior. 253

14.6.1 Specify block control of pulse limit values. 254

14.6.2 Global control of pulse limit values. 255

14.6.3 SDF annotation of pulse limit values. 255

14.6.4 Detailed pulse control capabilities. 256

15. Timing checks. 262

15.1 Overview. 262

15.2 Timing checks using a stability window. 265

15.2.1 $setup . 266

15.2.2 $hold . 266

15.2.3 $setuphold. 267

15.2.4 $removal . 269

15.2.5 $recovery. 270

15.2.6 $recrem . 271

15.3 Timing checks for clock and control signals . 273

15.3.1 $skew . 274

15.3.2 $timeskew . 275

15.3.3 $fullskew. 277

xii Copyright © 2001 IEEE. All rights reserved.

Published by IEC under licence from IEEE. © 2004 IEEE. All rights reserved.

8 IEC 61691-4:2004(E)

IEEE 1364-2001(E)

15.3.4 $width . 279

15.3.5 $period . 280

15.3.6 $nochange . 281

15.4 Edge-control specifiers . 283

15.5 Notifiers: user-defined responses to timing violations . 284

15.5.1 Requirements for accurate simulation .

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...