ISO/IEC 11458:1993

(Main)Information technology — Microprocessor systems — VICbus — Inter-crate cable bus

Information technology — Microprocessor systems — VICbus — Inter-crate cable bus

The objectives are to provide a standard cable bus for the interconnection of multiple devices, both backplane bus systems, such as the IEC 821 VMEbus, and stand-alone apparatus; to specify the electrical characteristics of the cable bus; to specify the protocols that precisely define the interaction between devices connected to the VICbus; to specify the mechanisms necessary to construct fault-tolerant, multi-device systems; to provide the necessary definitions, terminology and background information to fully describe the VICbus protocols and other mechanisms.

Technologies de l'information — Systèmes à microprocesseurs — VICbus — Bus à câbles inter-châssis

General Information

- Status

- Published

- Publication Date

- 15-Dec-1993

- Technical Committee

- ISO/IEC JTC 1/SC 25 - Interconnection of information technology equipment

- Current Stage

- 9093 - International Standard confirmed

- Start Date

- 13-Jul-2018

- Completion Date

- 14-Feb-2026

Relations

- Effective Date

- 06-Jun-2022

- Effective Date

- 15-Apr-2008

Overview

ISO/IEC 11458:1993 - Information technology: Microprocessor systems - VICbus - Inter-crate cable bus defines a standardized inter-crate (inter-chassis) cable bus for connecting multiple microprocessor-based devices. The standard specifies the electrical characteristics, signal assignments, bus protocols, timing rules and mechanisms required to build robust, fault-tolerant multi-device systems. It also provides terminology, register definitions and guidance for interfacing with backplane bus systems such as VMEbus (IEC 821).

Keywords: ISO/IEC 11458:1993, VICbus, inter-crate cable bus, VMEbus, microprocessor systems, cable bus, fault-tolerant.

Key Topics

- Scope & objectives: standardizes a cable bus for interconnection of devices and backplane systems; promotes interoperability and fault tolerance.

- Data transfer bus (DTB): defines DTB cycle types (direct and transparent), address/data lines (e.g., AD31–AD00), control lines (CL3–CL0), identification and device-number signals, block transfers, read-modify-write cycles, and detailed timing rules.

- Arbitration: protocols, arbiter/requester roles, arbitration lines and timing to control DTB mastership and avoid bus contention.

- Interrupts: interrupt lines, selection, protocol, interrupter and handler behavior, timing regulations.

- Utilities & fault tolerance: reset mechanisms (VICRESET), arbitration lock (ALOCK), device-failure signaling (DEVFAIL), online/offline states, cable connection/disconnection rules for robust systems.

- Electrical specifications: bus driver/receiver behavior, cable characteristics, connectors, terminators and termination power; continuity rules for offline devices.

- Registers & identification: control and status registers (CSR), online register (OLR), device operational register (DOR), reset register (RR), transparent and device identification registers (TR, DIR).

- VMEbus interfacing: annex material on mapping VICbus cycles and signals to VMEbus semantics (transparent cycles, AM codes, RETRY* behavior).

Applications

- Designing inter-chassis communications for embedded and industrial microprocessor systems.

- Implementing cable-based extensions of VMEbus systems or integrating stand-alone apparatus with backplane buses.

- Building fault-tolerant server clusters, modular instrumentation, or real-time control systems that require deterministic bus arbitration, interrupts and robust cable handling.

- Specifying cable/connector and termination schemes for multi-device installations.

Who uses this standard

- System architects and hardware engineers designing modular microprocessor systems.

- Embedded systems integrators working with VMEbus or similar backplane technologies.

- Test & validation engineers implementing timing, arbitration and interrupt behavior.

- Product teams producing device interface hardware (cables, terminators, bus transceivers).

Related standards

- IEC 821 / VMEbus specifications (for backplane compatibility and interface mapping).

- Relevant electrical and connector standards referenced for cable and termination practices.

This standard is essential when you need a documented, interoperable approach to inter-crate communication, deterministic bus protocols and reliable fault-tolerant behavior in microprocessor systems.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

NYCE

Mexican standards and certification body.

Sponsored listings

Frequently Asked Questions

ISO/IEC 11458:1993 is a standard published by the International Organization for Standardization (ISO). Its full title is "Information technology — Microprocessor systems — VICbus — Inter-crate cable bus". This standard covers: The objectives are to provide a standard cable bus for the interconnection of multiple devices, both backplane bus systems, such as the IEC 821 VMEbus, and stand-alone apparatus; to specify the electrical characteristics of the cable bus; to specify the protocols that precisely define the interaction between devices connected to the VICbus; to specify the mechanisms necessary to construct fault-tolerant, multi-device systems; to provide the necessary definitions, terminology and background information to fully describe the VICbus protocols and other mechanisms.

The objectives are to provide a standard cable bus for the interconnection of multiple devices, both backplane bus systems, such as the IEC 821 VMEbus, and stand-alone apparatus; to specify the electrical characteristics of the cable bus; to specify the protocols that precisely define the interaction between devices connected to the VICbus; to specify the mechanisms necessary to construct fault-tolerant, multi-device systems; to provide the necessary definitions, terminology and background information to fully describe the VICbus protocols and other mechanisms.

ISO/IEC 11458:1993 is classified under the following ICS (International Classification for Standards) categories: 35.160 - Microprocessor systems. The ICS classification helps identify the subject area and facilitates finding related standards.

ISO/IEC 11458:1993 has the following relationships with other standards: It is inter standard links to ISO/IEC 11458:1993/Amd 1:2000; is excused to ISO/IEC 11458:1993/Amd 1:2000. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

ISO/IEC 11458:1993 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

lSO/IEC

INTERNATIONAL

STANDARD

First edition

1993-l 2-01

Information technology -

Microprocessor systems -

VlCbus - llnter-crate cable bus

Technologies de /‘information -

Syst&mes a microprocesseurs -

WCbus - Bus a cables inter-chassis

Reference number

ISOA EC 11458: l993( E)

- - 6 ISO/IEC 11458 : 1993

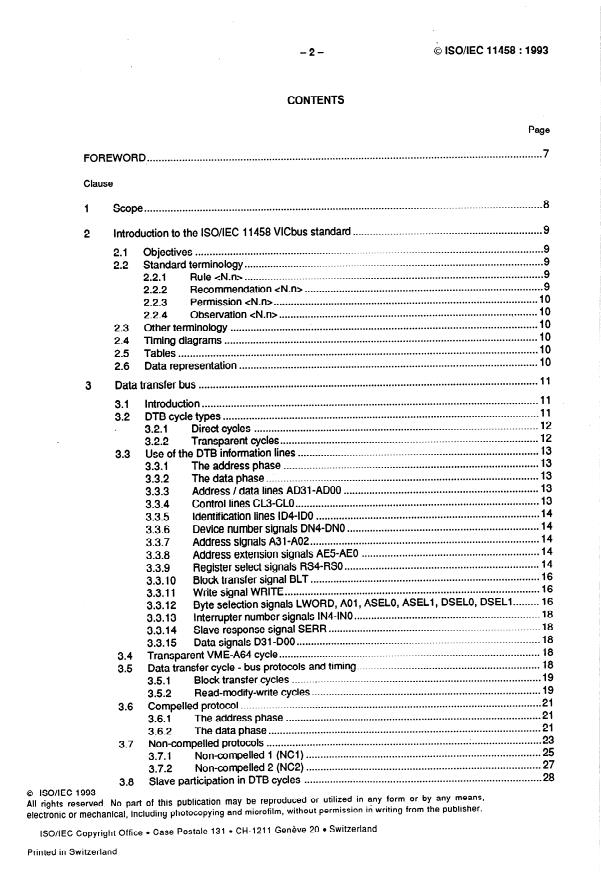

CONTENTS

Page

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .*.*.

FOREWORD

Clause

1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Scope

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Introduction to the ISO/IEC 11458 VICbus standard

........................................................................................................................

2.1 Objectives

.......................................................................................................

2.2 Standard terminology

.......................................................................................................

2.2.1 Rule

..................................................................................

2.2.2 Recommendation

...........................................................................................

2.2.3 Permission

.........................................................................................

2.2.4 Observation

..........................................................................................................

2.3 Other terminology

............................................................................................................

2.4 Timing diagrams

............................................................................................................................

2.5 Tables

.......................................................................................................

2.6 Data representation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Data transfer bus

3.1 Introduction .

.............................................................................................................

3.2 DTB cycle types

. 12

3.2.1 Direct cycles .

.........................................................................................

3.2.2 Transparent cycles

...................................................................................

3.3 Use of the DTB information lines

........................................................................................

3.3.1 The address phase

..............................................................................................

3.3.2 The data phase

...................................................................

Address / data lines AD31-ADO0

3.3.3

....................................................................................

Control lines CL3CLO

3.3.4

.............................................................................

Identification lines ID4-ID0

3.3.5

..................................................................

3.3.6 Device number signals DN4-DNO

...............................................................................

3.3.7 Address signals A31-A02

.............................................................

3.3.8 Address extension signals AES-AEO

...................................................................

Register select signals RS4-RSO

3.3.9

...............................................................................

Block transfer signal BLT

3.3.10

........................................................................................

3.3.11 Write signal WRITE

......... 16

3.3.12 Byte selection signals LWORD, AOl, ASELO, ASELI, DSELO, DSELI

. 18

....................

Interrupter number signals IN40IN0 .

3.3.13

.........................................................................

Slave response signal SERR

3.3.14

Data signals 031 -DO0 .

3.3.15

..........................................................................................

3.4 Transparent VME-A64 cycle

...............................................................

3.5 Data transfer cycle - bus protocols and timing

......................................................................................

3.5.1 Block transfer cycles

...............................................................................

3.52 Read-modify-write cycles

........................................................................................................

3.6 Compelled protocol

........................................................................................

The address phase

3.6.1

..............................................................................................

3 6.2 The data phase

:

...............................................................................................

3.7 Non-compelled protocols

.................................................................................

3.7.1 Non-compelled 1 (NCl)

.................................................................................

3.7.2 Non-compelled 2 (NC2)

..................................................................................

3.8 Slave participation in DTB cycles

Q ISO/lEC 1993

All rights reserved. No part of this publication may be reproduced or utilized in any form or by any means,

electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

ISOAEC Copyright Office l Case Postale 131 l CH-1211 Gen8ve 20 l Switzerland

Printed in Switzerland

w -

0 ISO/IEC 11458 : 1993

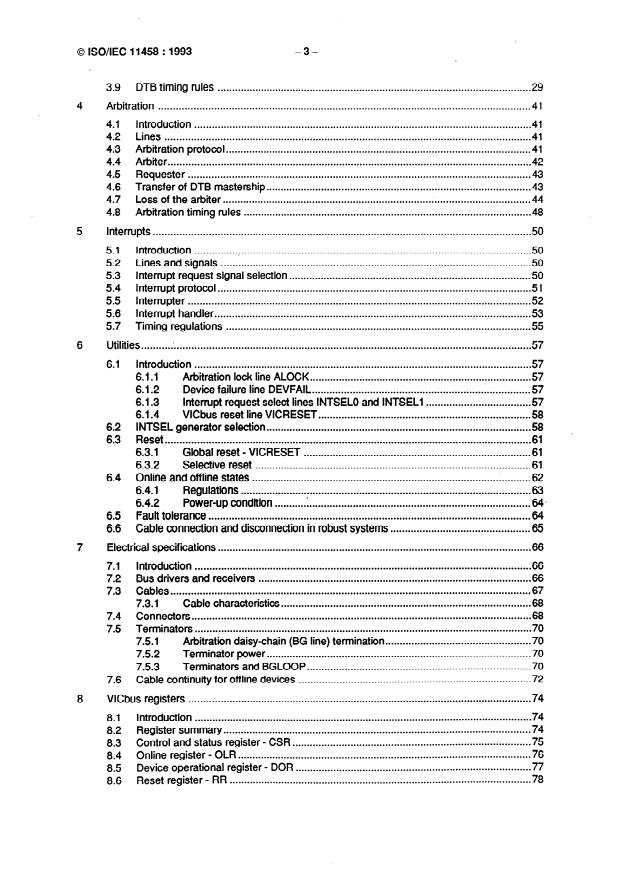

3.9 DTB timing rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

" 41

4 Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41 Introduction .

412 Lines .

4.3 Arbitration protocol .

4.4 Arbiter .

4.5 Requester . 43

4.6 Transfer of DTB mastership . 43

.......................................................................................................... 44

4.7 Loss of the arbiter

................................................................................................... 48

4.8 Arbitration timing rules

5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

51 . Introduction . 50

5.2 . Lines and signals . ” 50

53 . Interrupt request signal selection . 50

54 . Interrupt protocol . 51

. . 52

55 Interrupter

............................................................................................................. 53

56 . Interrupt handler

57 . Timing regulations .

I

6 Utilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.1 Introduction

Arbitration lock line ALOCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .*. 57

6.1 .l

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.1.2 Device failure line DEVFAIL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

6.1.3 Interrupt request select lines INTSELO and INTSELl

6.1.4 VlCbus reset line VICRESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 INTSEL generator selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .~.

6.3.1 Global reset - VICRESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.3.2 Selective reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Online and offline states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.4

6.4.1 Regulations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

,

Power-up condition . . . . . . . . . . . l . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.4.2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.5 Fautt tolerance

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.6 Cable connection and disconnection in robust systems

7 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Introduction .

7.2 Bus drivers and receivers .

7.3 Cables .

7.3.1 Cable characteristics .

.....................................................................................................................

7.4 Connectors

.................................................................................................................... 70

7.5 Terminators

Arbitration daisy-chain (BG line) termination . 70

7.5.1

Terminator power . 70

7.5.2

............................................................................. 70

7.5.3 Terminators and BGLOOP

7.6 Cable continuity for off line devices .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 VlCbus registers

....................................................................................................................

8.1 Introduction

..........................................................................................................

8.2 Register summary

..................................................................................

8.3 Control and status register - CSR

.....................................................................................................

8.4 Online register - OLR

.................................................................................

8.5 Device operational register - DOR

........................................................................................................

8.6 Reset register - RR

- -

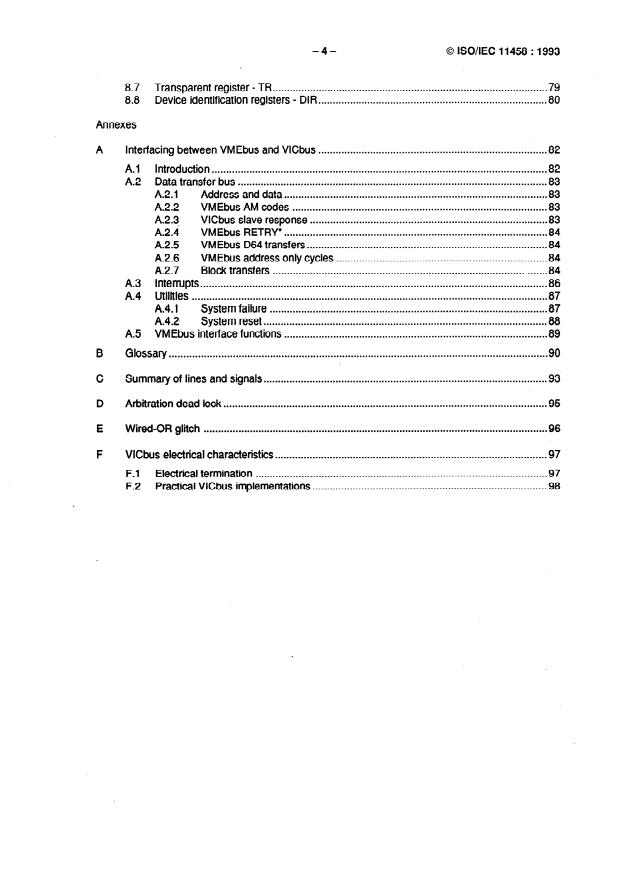

4 0 ISOllEC 11458 : 1993

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-.*. 79

8.7 Transparent register - TR

8.8 Device identification registers - DIR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Annexes

............................. . .................................................. 82

A Interfacing between VMEbus and VlCbus

.................................................................................................................... 82

A.1 Introduction

A.2 Data transfer bus . 83

A.201 Address and data . 83

A.202 VMEbus AM codes . 83

.................................................................................. 83

A-2.3 VlCbus slave response

........................................................................................... 84

A.204 VMEbus RETRY*

................................................................................... 84

A-2.5 VMEbus 064 transfers

A-2.6 . 84

VMEbus address only cycles

A.207 . 84

Block transfers

........................................................................................................................ 86

A.3 Interrupts

A.4 Utilities .

A.401 System failure . 87

A-4.2. System reset . 88

A.5 VMEbus interface functions . 89

................................................................................................................................... 90

Glossary

Summary of lines and signals . 93

Arbitration dead lock . 95

Wired-OR glitch . 96

.............................................................................................. 97

VlCbus electrical cha.racteristics

..................................................................................................... 97

F-1 Electrical termination

................................................................................. 98

F-2 Practical VlCbus implementations

- -

0 ISOAEC 11458 : 1993

Page

Tables

.....................................................................................................

1 VICbus data representation

.............................................................................................................................

2 Direct cycles

...................................................................................................................

3 Transparent cycles

........................................................ 15

4 Use of the address / data, control and identification lines

...........................................................................................................

5 VMEbus byte alignment

.................................................................................................................

6 Byte lane alignment

................................................................................

7 Transparent VME-A64 signal assignment

.........................................................................

8 Summary of slave participation in DTB cycles

.......................................................................................................

9 Master - timing regulations

.........................................................................................................

10 Slave - timing regulations

.......................................................................................................

11 Arbiter - timing regulations

.................................................................................................

12 Requester - timing regulations

...................................................................................................

13 Interrupt request multiplexing

14 IACK byte alignment .

Summary of interrupt protocol actions .

15 .

...................................................................................................

16 Interrupts - timing regulations

.

.....................................................................

17 INTSEL generator selection - timing regulations

............................. 62

18 Summary of the online / offline state of a device following various actions

.............................................

Summary of actions permitted in the three online / off line states

.............................................................................................................................

20 VlCbus lines

..........................................................................................

21 VlCbus connector pin assignments

....................................................................................................................

22 Register summary

...................................................................................................

23 Command and status register

24 Online register .

......................................................................................................

Device operational register

...........................................................................................................................

26 Reset register

.................................................................................................................

27 Transparent register

...................................................................

28 Device identification registers - byte assignments

.....................................................................

29 Device identification register 2 - bit assignments

.....................................................................

30 Device identification register 3 - bit assignments

........................................................................

Al . VMEbus interface control and status functions

- -

0 ISOIIEC II458 : 1993

,

Page

Figures

1 DTB cycle .

..................................................................................................................

2 Compelled protocol

........................................................................................................

3 Non-compelled 1 protocol

........................................................................................................

4 Non-compelled 2 protocol

.......................................................................................................................

5 Compelled cycle

................................................................

6 Compelled cycle last data transfer and end of cycle

..............................................................................

7 NC1 address phase and first data transfer

...................................................................................

NC1 last data transfer and end of cycle

..............................................................................

9 NC2 address phase and first data transfer

...................................................................................

NC2 last data transfer and end of cycle

Arbitration-l .

Arbitration-2 .

Arbitration-3 .

.............................................................................................

14 Interrupt request selection timing

.....................................................................................................

15 INTSEL generator selection

.............................................................................................................

16 Electrical transmission

.

.......................................................................................

17 Bus grant daisy-chain and BGLOOP

.............................................

Bus Grant termination and continuity of lines in robust systems

........................................................................................................

Al Inter-crate block transfers

............................... 87

A2 . DEVFAIL / SYSFAlL* interconnection for a VMEbus to VlCbus interface

.......................................................................

Reset circuit for a VMEbus to VlCbus interface

A3

...............................................................................................

Dl . Arbitration dead-lock resolution

.......................................................................................................................

El . Wired-OR glitch

..................................................................................................................

Fl . VlCbus termination

.................................................................................................

F2 . Device / cable length derating

-70

0 ISOAEC II458 : 1993

Foreword

IS0 (the International Organization for Standardization) and IEC (the International Electrotechnical

Commission) form the specialised system for world-wide standardisation. National bodies that are

members of IS0 or IEC participate in the development of International Standards through technical

committees established by the respective organisation to deal with particular fields of technical

activity. IS0 and IEC technical committees collaborate in fields of mutual interest. Other international

organisations, governmental and non-governmental, in liaison with IS0 and IEC, also take part in the

work.

In the field of information technology, IS0 and IEC have established a joint technical committee,

ISO/IEC JTCI. Draft International Standards adopted by the joint technical committee are circulated

to national bodies for voting. Publication as an International Standard requires approval by at least

75 % of the national bodies casting a vote.

International Standard lSO/IEC 11458 was prepared by Joint technical committee ISO/IEC JTC 1,

Informafr’on technology, SC 26: Microprocessor Systems.

Annex A forms an integral part of ISO/IEC 11458. Annexes B to F are for information only.

- -

8 0 ISO/IEC 11458 : 1993

Information technology - Microprocessor systems -

VICbus - Inter-crate cable bus

The widespread use of high-performance, multi-processor systems based on backplane buses such

as the IEC 821 bus (VMEbus), has inevitably led to the requirement to create multi-crate (subrack,

-chassis, etc.) systems. The VlCbu,s inter-crate cable bus is designed to achieve such assemblies in

a standard way.

VICbus, a multiplexed, multi-master, multi-slave cable bus, connects multiple backplane buses or

stand-alone devices, providing transparent, softwareless interconnection for low latency short data

transactions and fast transmission of data blocks over cables of up to 100 m in length. Address and

data signals, each of 32 bits, together with those necessary for the control of the bus protocols,

signal multiplexing, reset and error reporting are transmitted on twisted-wire pairs using differential

line drivers and receivers. Up to 31 devices are permitted on a single VICbus cable.

VICbus data transfer protocols include both a compelled mode with end-to-end acknowledgement as

well as two, high speed, non-compelled modes for high rate data transfers. The compelled protocols

allow both broadcast (master write) and broadcall (master read) data transfers. One of the non-

compelled protocols allows broadcast transfers, whereas neither permit broadcall operation.

Inter-master arbitration uses an efficient, modified single-level, daisy-chained mechanism. The

interrupt mechanism allows 32 interrupt requests, multiplexed on eight physical lines. The

specification includes system failure reporting, reset and live connection and disconnection, as well

as the specification of control and status registers. Particular attention has been paid to redundancy

-

of operation.

Whilst VlCbus has been derived with multi-crate backplane bus systems in mind, this specificat.ion

does not preclude the design of stand-alone VlCbus devices. A normative annex giving rules and

recommendations for a VMEbus to VlCbus interface has been included, and further, similar annexes

for other backplane bus standards will be added as the need arises.

- e

0 ISO/IEC 11458 : 1993

2 Introduction to the ISOAEC 11458 VlCbus standard

2.1 Objectives

VlCbus is a cable bus intended to be used to connect together multiple devices, particularly

backplane bus systems, efficiently and with the possibility of software transparent operation, to allow

large mutti-crate, multi-processor systems to be constructed.

The objectives of this standard are to:

provide a standard cable bus for the interconnection of multiple devices, both backplane bus

a)

systems, such as the lEC821 VMEbus, and stand-alone apparatus;

specify the electrical characteristics of the cable bus;

b)

specify the protocols that precisely define the interaction between devices connected to the

C)

VICbus;

.

specify the mechanisms necessary to construct fault-tolerant, mutti-device systems;

d)

provide the necessary definitions, terminology and background information to fully describe the

e)

VlCbus protocols and other mechanisms.

2.2 Standard terminology

To avoid ambiguity, and to ensure that it is clear what the requirements for compliance are, many of

the paragraphs in this standard are prefixed with sequentially numbered keywords by clause (N),

known collectively as regulations, thus:

,

RULE cN,n>

RECOMMENDAnON 4N.m

PERMISSION 4N.m

OBSERVA77ON chl,n>

2.3.7 Rule

Rules form the basis of the VlCbus standard, and may be expressed in textual, diagrammatic or

tabular form. They use the imperative form and i’nclude the upper case words SHALL or SHALL

NOT, which are resewed for this purpose only. Rules are printed in italics, thus:

RULE 2.1

Example: rules contain the upper case words SHALL or SHALL NOT.

2.2.2 Recommendation

Recommendations contain information which will be very useful, if not vital, when designing to the

VlCbus standard and designers are encouraged to heed the advice given to ensure the best possible

interpretation of the specification’s requirements.

.

RECOMMENDATION 2.1

Example: recommendations contain very useful information.

-IO- OISO/IEC 11458:1993

2.2.3 Permission

Permissions clarify aspects of the standard where multiple choices might be possible, and indicate

acceptable lines of approach. The upper case word MAY is reserved for this purpose only.

PERMISSION 2.1

Example: permissions help you choose and include the upper case word MAY.

2.2.4 Observation

Observations serve to explain the rationale behind rules and other requirements.

OBSERVATION 2.1

Example: observations explain the rationale of certain requirements.

2.3 Other terminology

All normative terms (that is those having a specified meaning within the context of this document) are

typed in bold font, in general the first time they appear, thus: arbiter. Such terms are explained in the

informative glossary, included as annex B, in addition to any references within the body of the text.

2.4 Timing diagrams

Timing diagrams are drawn such that a high level represents the asserted state (logical 1).

2.5 Tables

The asserted (logical 1) and deasserted (logical 0) states are indicated in tables as “1” and “0”

respectively.

2.6 Data representation

Table 1 shows the labelling and significance of the bytes (groups of eight bits) within the four-byte

location selected by a VlCbus address or by the register select signals.

Table 1 - VlCbus data representation

Least‘signiticant bit

Most significant bit

v

‘I

Byte (1) Byte (2) Byte (3)

Byte (0)

8 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

. . . . . . . . . . . . . . . . . * . . . . . . . . . 24 23 . . . . . . . . . . . . . . . . . . . . l . . . . . . 16 15 . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data bits 31

Al-

0 iSO/iEC 11458 : 1993

3 Data transfer bus

3.1 Introduction

The Data Transfer Bus (DTB) is the means by which data, address, control and status information is

transferred between VlCbus devices. The device containing the current master uses the address

information to select one or more participating slaves and the addresses within them with which it

wishes to exchange data. The control information specifies the direction of data transfer and the

number and position of bytes within the four-byte data bus which are to be transferred.

VICbus devices can be self-contained units, interfaces between VlCbus and a backplane bus such

as VMEbus, or both. Thus the DTB also carries control information which indicates whether the

required slave is within a participating slave device or on a backplane associated with it.

Two types of data transfer protocol are specified for use on the DTB: compelled and

non-compelled. The compelled protocol uses a full handshake which permits the cycle timing to be

controlled by both the master and the participating slave(s) and, if the slave is on a backplane bus,

permits the VlCbus timing, to be interlocked with that of the backplane. The two non-compelled

protocols provide a faster means of transmitting data, by eliminating the round-trip propagation time

of the cable which is inherent in the compelled protocol, however they can only be used to access

slaves within VICbus devices.

The VlCbus arbitration mechanism (specified in clause 4) ensures that only one master may use the

DTB at a time. However, the use of bus drivers with a Wired-OR” capability permits a master to

transmit data to several participating slaves simultaneously (broadcast operation) or to receive data

from several participating slaves simultaneously (broadcall operation) when using the compelled

protocol, or when using one of the non-compelled protocols in the case of broadcast operation.

Additionally, whichever protocol is in use, data transfers may be spied upon (that is read on-the-fly

with no active participation in the transfer protocol by the device concerned).

The DTB consists of two groups of physical lines: the 42 information lines (AD31-ADOO, CL3CL0,

ID&ID0 and SERR) onto which logical signals are multiplexed, and the three timing lines (AS, DS

.

and WAIT) which are not multiplexed and for which the terms “lines” and “signals” can therefore be

used interchangeably.

3.2 DTB cycle types

When initiating a DTB cycle, the master transmits control information indicating the cycle type to be

performed, so defining the following:

the data transfer protocol to be used;

a)

whether the required slave is within the addressed device (direct cycles) or on an associated

W

backplane bus, if the device is an interface (transparent cycles);

whether a data transfer cycle or an interrupt acknowledge cycle is to be performed (the latter-

Cl

is specified in clause 5);

the address width used (32 or 64 bits) on associated VMEbus backplanes;

d)

the byte.alignment used (VMEbus or byte lane aligned (BLA), specified in 3.3.12).

e)

Table 4 details the cycle types in terms of the lines and signals used.

-12- OISOAEC 11458:1993

3.2.1 Direct cycles

Direct cycles access VlCbus slaves within devices rather than those connected to an associated

backplane bus. The RS4-RSO signals (see 3.3.9, below), are used to select one of 32 register

locations (some of which may use the A31-A02 signals for sub-addressing). The allocation of

mandatory and user definable register locations is specified in clause 8.

The three direct cycle types described in this specification are listed in table 2.

RULE 3.1

A device SHALL be capable of responding to direct compelled cycles as a slave.

Table 2 - Direct cycles

P

Protocol Data alignment Application

cycle type

Byte lane Transfers to slaves within devices (that is not on

Direct compelled Compelled

an associated backplane bus) with handshake

control

Transfers to slaves within devices with no

Direct non-compelled 1 Non-compelled Byte lane

handshake control

Direct non-compelled 2 Non-compelled Byte lane Transfers to slaves within devices with no

immediate handshake control; the slave’s

responses being pipelined. The initiai transfer is

the exception, since it is fully handshaken in

order to confirm the existence and capability of

the slave

3.2.2 Transparent cycles

The compelled protocol is used to access slaves connected to the backplane bus associated with an

interface device, and the timing is interlocked with that of the backplane bus. Note that the non-

compelled protocols cannot be used to implement transparent cycles, as this interlock is not

possible.

The three types of transparent cycle described in this specification are listed in table 3.

Table 3 - Transparent cycles

Protoco1 Data alignment Application

cycle type

VMEbus A64 cycles are transmitted over

Transparent Transparent VME-A64 VME-A64 1 1 ) ) Compelled VMEbus

VlCbus and a corresponding A64 cycle is

generated on an associated VMEbus backplane

r

VMEbus A32, A24 or Al6 cycles are transmitted

Compelled VMEbus

Transparent Transparent VME VME

over VlCbus and corresponding cycles are

generated on an associated VMEbus backplane

Compelled Byte lane Cycles are generated on an associated non-

Transparent BlA

VMEbus backplane (intended for future

applications)

l) A64 transfers are described in the proposed revision of the VMEbus specification document known as “VME64”.

-130

0 ISOAEC 11458 : 1993

3.3 Use of the DTB information lines

In order to keep the number of physical lines to a practical number for a cable bus, the DTB

information lines are multiplexed, and a DTB cycle therefore consists of an address phase and a

data phase the latter consisting of one or more data transfers. The structure of a DTB.cycle is

illustrated in figure 1.

The address phase

3.3. I

The address phase is used by the master to:

select the slave device or devices which it requires to participate in the cycle;

a)

specify the cycle type;

b)

transmit an address internal to the slave or slaves.

c)

3.3.2 The data phase

The data phase is used to transmit data to and / or from the selected address within the slave or

slaves. In the case of a block transfer, it transfers data to or from successive addresses.

The multiplexed signals carried by the DTB information lines during the address and data phases are

shown in tables 4,5 and 6, and defined in subclauses 3.3.3 to 3.3.15, inclusive. In some cases the

signal carried by a particular line depends on the cycle type, as well as on the phase of the cycle

(address or data).

---oIIoIIII pmo----m----- p-----------

8 8

b

*rrrrrrmrrr-r m-

Nmm0IIIII-I *rrrrrrrm.rr

-L

+ Data

Oada +

transfer

transfer

- Address +4

Data phase

phase

p- DTBcycle **‘I

.

Figure 1 - DTB cycle

3.3.3 Address /data lines AD31-AD00

The 32 address / data lines (AD31-ADOO) carry address and byte selection signals during the

address phase, and data signals during the data phase.

3.3.4 Control lines CL3-CL0

The four control lines (CL3CLO) carry control signals during both the address and data phases. In

addition, they carry some addressing signals during the address phase of the transparent VME and

VME-A64 cycle types. During the address phase, CL3 and CL2 carry cycle type definition signals,

whilst CL1 and CL0 either carry further cycle type definition signals or addressing signals. During the

-14- OISO/IEC 11458:1993

data phase, all four control lines carry additional protocol and byte selection signals.

Identification lines lD4-ID0

3.3.5

The five identification lines (ID4-IDO) carry device selection and other addressing signals. During the

address phase they carry the device number (or, in the case of an IACK cycle, the interrupter

number) signals. During the data phase they carry address extension signals for transparent cycles,

and register select signals for direct cycles.

3.3.6 Device number signals DN#-DNO

The device number signals carry the highest level of addressing information. They are used by the

master to select the VICbus slave device or devices which it wishes to participate in the cycle.

Device numbers in the range 31-1 select individual devices, whilst device number 0 (zero) selects all

on-line devices capable and willing to participate in broadcast or broadcall operations. Every slave

device is normally equipped with a means (for example a switch or switches) to allow the user to set

the device number by which it will be selected.

RECOMMENDATION 3.1

Equip a slave device with a means whereby a user can set the device number by which it will

.

be selected. Design the device such that the device number can be set and is subsequently

visible at its front panel.

OBSERVATION 3.1

It is the responsibility of the user to ensure that no more than one slave has a particular device

number, if this is undesirable.

RULE 3.2

A cycle canying device number 0 (zero) SHALL indicate a bn>adcast or broadcall cycle.

Address signak A31-A02

3.3.7

The address signals A31-A02 are used to select a four-byte (32 bit) location within selected slave or

.

slaves, except during certain direct cycles when only the register select signals are used for this

purpose. The selection of bytes within a four-byte location is described in 3.3.12.

PERMISSION 3.1

An interface to a backplane bus MAY provide address mapping facilities whereby the user can

program the correspondence between blocks of addresses on VlCbus and blocks of

addresses on the backplane bus.

Address extension signals AES-AEO

3.3.8

The address extension signals AES-AEO are used during transparent cycles to pass extra

addressing information over the VlCbus (for example the VMEbus address modifier signals - see

a

annex A).

3.3.9 Register sekct signals RS4-RSO

The register select signals are used during direct cycles to select one of 32, four-byte register

locations within selected slave or slaves, as specified in clause 8. For most register locations, the

address signals (A31-A02) are not used and, therefore, do not need to be decoded by the slave or

slaves, however, access to facilities within the device, such as banks of memory, may require their .

use.

0 ISOllEC 11458 : 1993 -15-

Table 4 - Use of the address /data, control and Identification lines

NOTE - RSVD

= Reserved for future allocation. All other mnemonics are explained in the

accompanying text.

Address Phase Address / data Contrc bl lines Identification lines

CL2 CL1 CL0 ID4 ID3 ID2 ID1 ID0

Transparent VME-A64 A31-A02 0 0 AES AE4 DN4 DN3 DN2 DNl DNO

I

~ Transparent BLA A31-A02 0 1 0 0 DN4 DN3 DN2 DNl

DNO

I

I

~ Reserved A3 1 -A02 0 1 0 1 RSVD RSVD RSVD RSVD RSVD

I

I

RWWWd A31-A02 0 1 1 0 RSVD RSVD RSVD RSVD

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...